多通道PXI總線數據采集卡的設計與實現

劉龍飛 張彥軍 朱思敏

(中北大學儀器科學與動態測試教育部重點實驗室,山西 太原 030051)

0 引言

美國國家儀器公司(簡稱NI公司)是全球著名研制生產信號采集設備和虛擬儀器的專業機構,1997年,NI公司在PCI基礎上開發了PXI(PCIextensions for instrumentation)總線。在儀器擴展方面,PXI總線已成為工業標準;在數據傳遞方面,PXI的性能較早期的系統有了顯著的提高。目前,全世界有近60個研究機構推出約500種PXI產品[1]。PXI在我國航天航空領域的應用也比較廣泛,但引進設備的接口和信號參數等大多與實際需求不符。為更方便地應用與推廣由PXI總線構成的信號采集和信號源等系統,必須根據技術要求來開發符合標準的產品。本文提出了一種基于PXI總線的多通道數據采集卡,并介紹了各功能模塊的工作原理。

1 系統總體結構與設計原理

1.1 系統總體結構

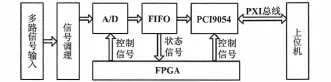

本數據采集系統由PCI9054總線控制器、FPGA、外部FIFO、數模轉換電路、信號調理電路、多路信號選通電路等部分組成。其中,PCI9054總線控制器實現PXI總線接口功能,ADS8041用于對輸入模擬信號進行A/D轉換,FIFO存儲器在前后數據傳輸過程中起到數據緩沖的作用,FPGA對數模轉換器、FIFO、PCI9054、多路模擬信號選通進行控制。系統總體結構框圖如圖1所示。

圖1 系統總體結構框圖Fig.1 Block diagram of the system structure

1.2 系統工作原理

本系統工作原理如下:多路模擬信號經過調理電路后,在FPGA的控制下通過ADG706進行選通;然后送入ADS8041進行模數轉換,轉換后的數字量存儲到FIFO中;當FIFO存儲器中的數據量達到半滿時,數據通過PCI9054傳遞給PXI總線并存儲到PC機內存中,通過上位機軟件進行存盤、顯示、繪圖。

整個系統采集過程采用FPGA進行嚴格的時序控制。

2 硬件設計

2.1 PXI總線接口設計

PXI總線規范具有PCI的性能和特點,其兼容CompactPCI的技術規范,故PXI總線接口芯片采用了PLX公司的PCI通用接口芯片(PCI9054)。PCI9054支持主模式、從模式和DMA傳輸方式,能夠廣泛地應用到各種適配卡和嵌入式系統中。

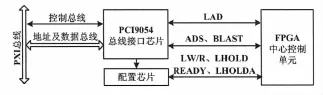

PCI9054提供了PCI總線接口、LOCAL總線接口和串行EPROM接口這3種物理總線接口。PCI總線接口信號主要有RST#、FRAME#、AD[31∶0]、C/BE[3∶0]#、IRDY#、CLK、TRDY#、DEVSEL#和 INTA#;串行 EEPROM 接口信號有EECS、EEDI、EESK和EEDO;本地總線接口信號有ADS#、BLAST#、CS0#、LA[5∶2]、LW/R#、LRESET#、READY#和 L INTi1[2]。PCI總線接口與 PXI接口對應端口相連即可。串行EEPROM接口信號只需要連接到NM93CS56芯片對應的引腳即可,而本地總線信號則要根據系統設計的需要進行選擇。PCI9054有C、M和J模式[3]這3種工作模式。本設計采用的是C模式下PCI Initiotor操作,本地處理器或本地總線主控設備能夠直接通過 PCI9054訪問 PXI總線,從而進行數據傳輸。PCI9054接口示意圖如圖2所示。

圖2 PCI9054接口示意圖Fig.2 Schematic diagram of PCI9054 interface

串行EEPROM采用93CS56芯片,用于存放PCI9054的重要配置信息,如廠商ID、器件型號ID、局部空間基地址、局部空間大小及映射類型、中斷控制和響應等信息。當系統上電時,這些配置信息將被自動加載到PCI9054的PCI配置寄存器和本地配置寄存器中,用于對系統進行初始化。主控計算機將根據PCI9054內部相關配置寄存器的內容分配系統所需要的資源。

2.2 EEPROM配置芯片接口設計

各種接口芯片都需要外接串行EEPROM芯片來加載配置數據。EEPROM配置芯片存儲了PCI9054的配置信息,只有正確加載了EEPROM內部的正確信息,才能夠順利進入系統。

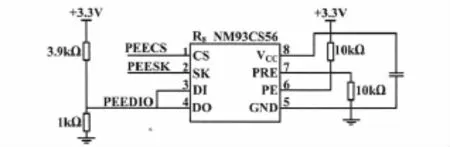

針對EEPROM配置芯片的選型問題,PLX公司在相應資料中已經給出了若干推薦的型號,要求EEPROM配置芯片必須同時滿足以下兩個條件:芯片必須支持串行連續讀寫模式;3.3 V供電時芯片能夠保證最大支持的串行時鐘速率大于1 MHz。本文選擇了由Fairchild Semiconductor公司生產的NM93CS56。PCI9054提供了4個管腳與串行EEPROM相連接,它們分別是 PEECS、PEEDI、PEEDO、PEESK,對應 于NM93CS56的 CS、DI、DO、SK 這4個管腳,這4對管腳一一對應連接[4]。PCI9054與EEPROM的接口電路設計如圖3所示。

圖3 PCI9054與EEPROM的接口電路Fig.3 Interface circuit between PCI9054 and EEPROM

值得注意的是,當PCI在沒有使用EEPROM時,應該使用1 kΩ下拉電阻才能進入系統;當使用空的EEPROM或者已經燒好的EEPROM時,則需要使用3.9 kΩ上拉電阻才能夠進入系統。因此,設計時應將此引腳根據實際需要焊接上拉或下拉電阻。

PCI板卡模塊的上電工作流程如下:PCI卡插到PC機插槽中→系統上電自檢→PCI9054的RST#復位→PCI9054檢測EEPROM是否存在→PCI9054根據EEPROM的配置信息初始化其內部寄存器→BIOS根據PCI9054配置寄存器的內容進行系統資源分配→進入系統,安裝 PCI9054 驅動[5]。

2.3 信號調理電路

2.4 采集控制電路

A/D轉換電路采用ADS8401芯片來實現。ADS8401是一個16位、1.25 MHz的A/D轉換芯片,它具有零遲緩、片上基準、低功耗等特性。調理選通后的輸入信號首先進入ADS8401并轉換為16位數字信號,在FPGA的控制下依次取高8位與低8位進行編幀;然后存入FIFO存儲器中;當達到半滿狀態時,在FPGA的控制下,FIFO輸出的HF#信號產生一個低電平信號,用于驅動PCI9054的本地總線中斷信號有效;產生PXI總線中斷后,將FIFO存儲器中的數據送入PC機進行處理,這樣就實現了整個系統的采集工作[6]。

3 系統硬件描述語言設計

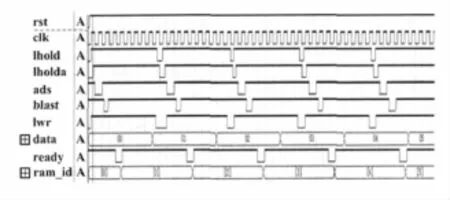

PCI9054的讀寫時序是狀態編寫VHDL代碼的參考關鍵,一些關鍵信號如READY#等的狀態控制稍有失誤,就會造成讀寫數據不正確,甚至會造成計算機死機、藍屏等嚴重后果[7]。本文詳細研究了PCI9054的讀寫時序狀態機,并按照狀態機的邏輯編寫VHDL代碼,實現了PCI總線對本地總線的讀寫操作。系統仿真結果如圖4所示。

圖4 系統仿真結果界面圖Fig.4 Interface of system simulation result

圖4中,rst為全局復位信號;clk為外部50 MHz時鐘信號;lhold為本地總線請求信號;lholda為本地總線請求應答信號;ads為本地總線觸發信號;blast#為突發傳輸信號;lwr為本地讀寫信號(高電平為寫,低電平為讀);ready為本地總線準備好的信號;data為PCI寫入的多通道參數數據;ram_id為定義的通道計數器。

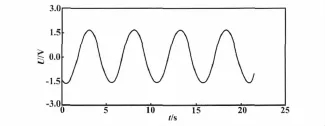

采用LabVIEW軟件對輸入信號采集模塊進行了實際測試。實際測試結果如圖5所示。

圖5 實際測試結果圖Fig.5 The actual test results

4 結束語

本文在PXI-1031硬件平臺上,設計實現了多通道PXI總線數據采集卡。該卡采用PCI9054芯片作為與PXI總線信號連接的接口芯片。本采集卡已成功應用于航空航天中大型設備的測試,并取得了很好的效果。

[1] 吳曉琳,鞏偉.PXI6534數字采集卡的原理與應用[J].信息技術,2012(1):154-158.

[2] 尹勇,李宇.PCI總線設備開發寶典[M].北京:北京航空航天大學出版社,2005.

[3] 張秀峰,毛先萍,阿米妮古.基于Matlab的PCI數據采集在過程控制系統中的應用研究[J].工業控制計算機,2012,25(8):11-13.

[4] 馬超,皮亦鳴.基于PCI9054的PCI接口數據通信系統[J].中國科技論文在線,2008,3(1):70-73.

[5] 安冬.基于 PCI9054從模式的數據采集卡設計與應用[J].北京:計算機測量與控制,2010:2439-2440.

[6] 方慶山.基于PCI總線的數據采集卡設計[D].南京:南京理工大學,2008.

[7] 羊三周.基于FPGA的PCI數據采集卡設計[D].太原:中北大學,2006.