基于FPGA和SD卡的任意波形發生器設計

王 潔,陸正剛,龔 健

(同濟大學鐵道與城市軌道交通研究院,上海 201804)

1 引言

基于頻率合成的波形發生器廣泛運用于通信和電子儀器中。受使用環境的限制,要求波形發生器設備具有便攜性和通用性。目前任意波形發生器的研制主要基于DDS技術,與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在通信、測量與電子儀器領域,是設備全數字化的一個關鍵技術[1]。

根據DDS直接數字波形方法設計了基于FPGA和SD卡的便攜式任意波形發生器,兼具使用方便(波形文件可以直接由通用讀卡器寫入SD卡中)和工作可靠的特點。

2 系統結構與硬件設計

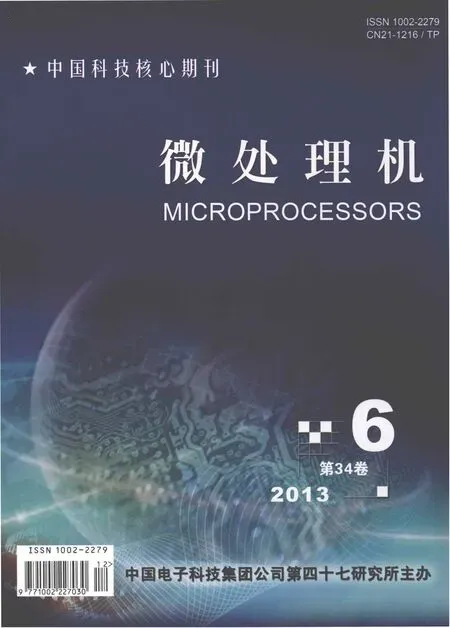

波形發生器提供一個通道,可產生多種不同頻率、不同形式的信號。系統結構如圖1所示,主控制器采用ALTER公司的CYCLONE3系列FPGA EP3C25Q來完成DDS直接數字波形生成以及SRAM和SD卡的控制。數據存儲采用SD卡,可存放2G波形文件。數據緩存則采用 ISSI公司的SRAM IS61NLP102418A,可以緩存18×1024Kbit的數據,實現低速SD卡數據讀取和高速波形產生之間的緩存,最后由MAXIM公司的MX7451A完成數字波形到模擬波形的轉換,由集成式開關電容濾波器完成濾波。系統結構如圖1所示。

圖1 任意波形發生器系統結構

3 DDS組成及工作原理

任意波形發生器一般采用DDS(Direct Digital Synthesis,直接數字合成)技術作為波形合成的核心技術。其信號源容易實現,精度高,能把信號源的頻率穩定度、準確度提高到和基準頻率同樣的水平,且可以在很寬的頻率范圍內進行精細的頻率調節[4]。

考慮FPGA片內資源的有限性,使用了如圖2所示的DDS結構。

圖2 DDS構架圖

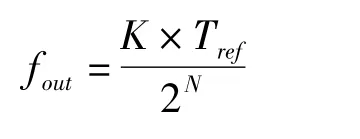

圖中頻率控制字K和相位累加器用來控制輸出頻率,輸出頻率為

其中N為相位累加器的位數,K為頻率控制字,Tref為基準時鐘頻率。

4 SD卡數據存儲

SD卡作為多功能存儲卡,具有較快的傳輸速度和較大的存儲容量,適合存儲大量波形文件,以供調用。SD卡有兩種總線模式,SD卡總線模式和SPI總線模式。SD卡總線模式采用4根總線傳輸數據,傳輸能力強但協議復雜。SPI總線模式采用單根數據線傳輸數據,其傳輸能力基本滿足設計要求,并且具有協議簡單的優勢。設計采用SPI模式讀取SD卡中波形文件數據。

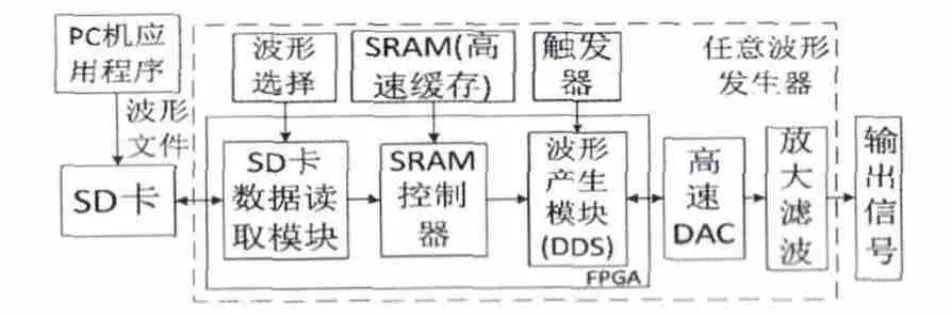

在SPI模式下,FPGA與SD卡的連接主要有四根線(包括一根時鐘線,兩根數據傳輸線和一根片選線),其硬件連接如圖3所示。

讀取SD卡中波形數據前需確定波形數據存放的首地址,可由上位機程序先行確定其存放格式,例如FAT16、FAT32等。讀取SD卡中數據的基本流程如下:

初始化步驟

(1)延時至少74clocks;

(2)發送 CMD0,需要返回 0x01,進入 Idle狀態;

(3)循環發送 CMD55+ACMD41,直到返回0x00,進入Ready狀態;

(4)發送CDM16,設置數據長度為512Bytes。

圖3 FPGA與SD卡連接圖

讀步驟

(1)發送CMD17(單塊)或CMD18(多塊)讀命令,返回0x00;

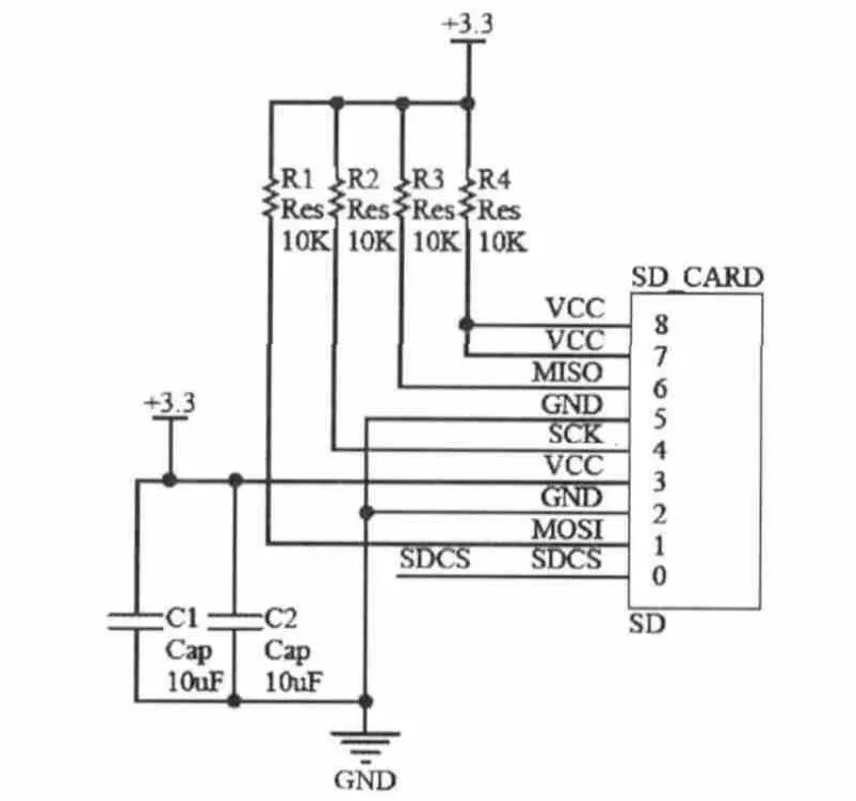

(2)接收數據開始令牌0xfe+正式數據512Bytes+CRC校驗2Bytes。如圖4所示。

圖4 讀取SD卡中數據

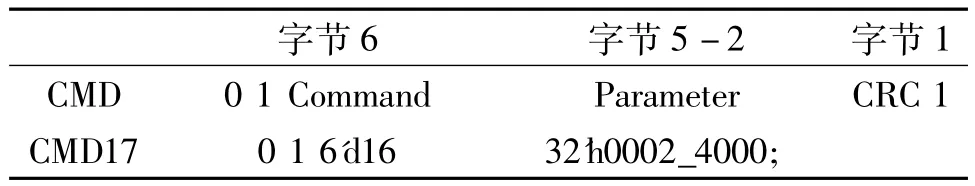

SPI模式下一組命令占6字節,命令格式如表1所示。

表1 SPI模式下命令格式

5 SRAM數據緩存

由于SD卡的數據傳輸速度與DAC的高工作頻率之間不協調,需添加一塊SRAM作為緩存。單個波形數據文件先從SD卡中讀出并寫入SRAM中,由DDS模塊中的相位控制字決定讀取SRAM時的首地址,再由頻率控制字K和相位累加器取得讀取地址,從SRAM中讀取波形文件,送入DAC中。

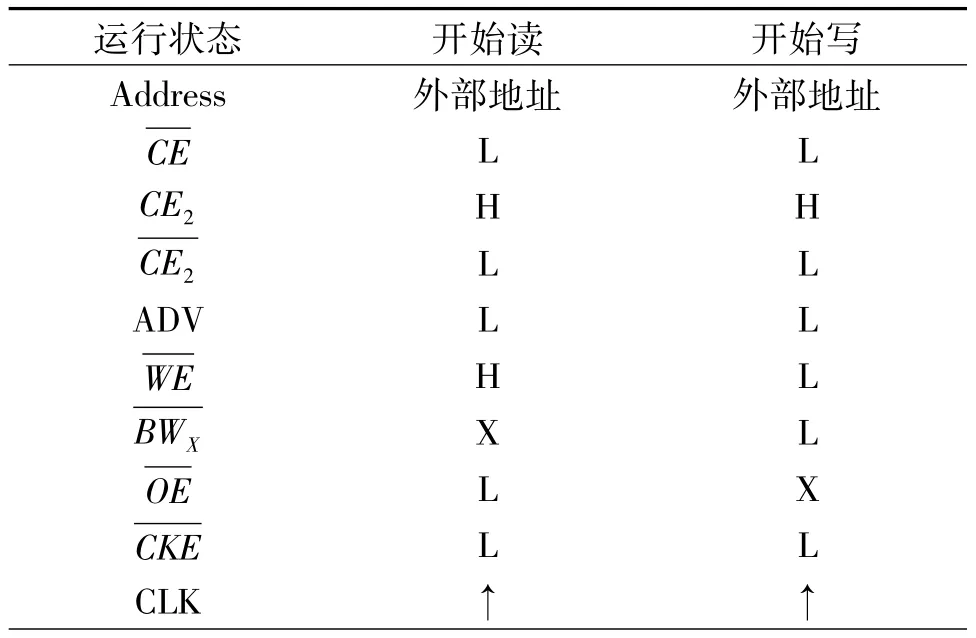

ZBT SRAM分為兩種,pipelined ZBT SRAM和flow-through ZBT SRAM。設計選用 ISIS公司IS61NLP102418芯片,Pipeline型,存儲容量為1Mb×18bit,最大工作頻率為250MHz,pipelined ZBT SRAM讀命令發出兩個時鐘周期之后,可得到讀取的數據,寫命令發出兩個時鐘周期之后,可以寫數據。

表2為ZBT SRAM的讀寫真值表[5]。接口信號主要由時鐘信號、控制總線、地址總線和數據總線等組成,所有控制信號、地址信號和數據信號都在時鐘信號(CLK)的上升沿被采樣。若符合真值表,當為低時對地址線上指定的地址單元進行寫操作,為高時則對地址線上指定的地址單元進行讀操作[6]。

表2 ZBT SRAM讀寫真值表

6 數模轉換

由于從DDS模塊中讀出的是波形的量化值,數字量,故需要DA進行數模轉換。選擇數、模轉換器DAC時需綜合考慮其轉換速度、分辨率、SNR、接口和輸出形式等。經分析選擇MAXIM公司的MX7541A作為DAC。它是一款高速DA芯片,12位,電平建立時間0.6μs,并行接口,雙極性模式下原理圖如圖5所示[7]。

圖5 MX7541A原理圖

如圖5所示,可通過R1調整Vref,C1做反饋電壓的相位延時調整,R2做反饋電壓調整電阻。由AD7541a輸出的是微弱電流信號,因此需要放大信號。在此選用AD8041高速運算放大器,采用±5V供電,從圖6中可以看出它在0-30MHz具有小于0.1db的增益平坦度。當數字信號不斷送入時,輸入輸出電壓關系如表3所示。

表3 輸入輸出真值表

圖6 頻率增益圖

7 濾波電路與放大電路

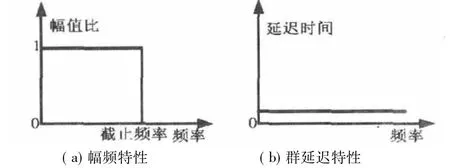

低通濾波器的設計是整個系統的關鍵點與難點。離散數字信號經過DAC轉換為模擬信號時帶來了頻譜分量復雜,雜波多等缺點,需要針對不同信號設計低通濾波器來保持有效分量并抑制雜波。理想的低通濾波器的幅頻特性和群延遲特性如圖7所示[8]。

圖7 理想低通濾波器幅頻特性和群延遲特性

實際上這種理想的濾波器是不存在的,只有去無限接近其特性曲線。同時若針對某一波形設計適合的模擬濾波器,則將不能隨輸出波形的改變而改變其截止頻率,況且模擬濾波器具有一定的設計難度和較大的公差,制造困難。故選擇了MAXIM公司的集成濾波器作為解決方案。

Maxim公司的 MAX293,是一款集成式8階、Elliptic、低通開關電容式濾波器,-5V~+5V供電,十分適合應用于反鋸齒波的設計中。其拐角頻率范圍 0.1Hz~25KHz。濾波比為1.5提供 -80DB的緩減帶。它的控制簡單,只需設定時鐘頻率去控制拐角頻率,時鐘與拐角頻率的比值為100:1[9]。圖8是它的引腳連接示意圖。

圖8 MAX293引腳連接示意圖

只需要控制引腳1(CLOCK)就可以改變其拐角頻率。根據DDS原理得知,波形頻率公式如下:

0.6 μs為DAC器件的電平建立時間,故Tref=1.667MHz。通過公式可知波形頻率可通過K來改變,若K為1則,fout=6.36Hz(頻率分辨率)。

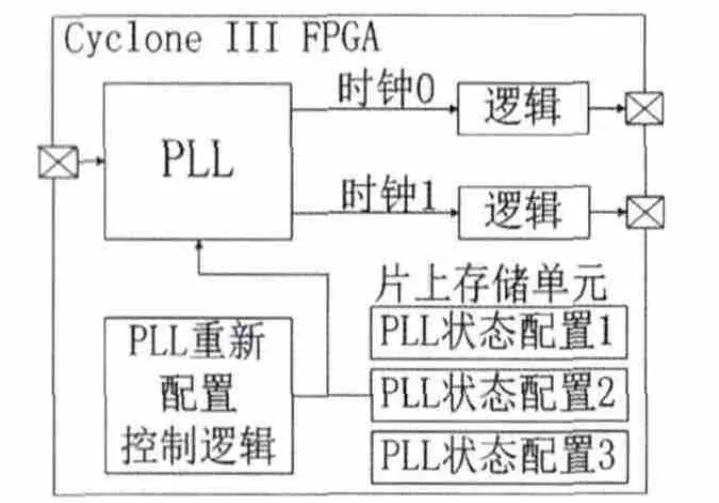

針對不同輸出信號頻率,需要給予時鐘信號控制濾波器的拐角頻率。綜合考慮到開關時鐘的相位抖動而產生的不同程度失真,故采用CYCLONE III中的PLL時鐘合成器來產生精確的時鐘信號。Quatus II提供相應的IP核來配置PLL。值得一提的是,Cyclone III PLL的重新配置功能,能夠在器件工作時動態改變PLL狀態。可以在片內存儲器中存儲多個PLL狀態配置,根據系統建立的觸發條件而動態進行加載。圖9所示為這種系統的一個例子,根據一組固定輸入或者用戶建立的觸發條件而采用了3種不同的頻率模式。一個Cyclone III PLL便能夠支持所有3種模式,每一模式對應一種PLL狀態配置,可以實時進行動態加載。ALTERA提供了相關IP支持重新配置,為頻率控制字K來決定PLL的配置方案提供了可能。

圖9 PLL參數動態加載系統實例

圖10為 PGA206增益與頻率響應對照圖[10]。該可編程增益放大器在100KHz以下具有良好的線性特征。

幅度增益部分則采用TI公司的PGA206來實現,其提供可編程增益,1、2、4、8t V/V。

圖10 PGA206增益與頻率響應對照圖

8 結 束 語

針對任意波形發生器的便攜性和通用性提出了使用SD卡來完成數據存儲功能。又通過分析DDS理論提出了使用頻率控制字來確定濾波器的拐角頻率,可以根據用戶需求設置低通濾波器的截止頻率,從而節省了設計多個濾波電路的成本,減少了電路復雜性。

[1]張嚴,洪遠泉.基于FPGA的任意波形發生器設計與研究[J].現代電子技術,2011,34(10):157 -159.

[2]彭龍.200MSPS任意波形發生器數字電路設計[D].成都:電子科技大學,2012.

[3]張洪濤,莫文承,李兵兵.基于SPI協議的SD卡讀寫機制與實現方法[J].電子元器件應用,2008,10(3):42-43.

[4]林英撐,童曉華,劉向宇.FPGA嵌入式系統設計與開發指南[M].北京:中國電力出版社,2012.

[5]ZBT SRAM Controller Reference Design For Stratix&Stratix GXDevices[EB/OL].www.altera.com,2004,4.

[6]王小蓉,田書林,劉科.一種ZBT SRAM接口控制器的設計[J].電子測試,2010(12):47-50.

[7]Data sheet of MX7541a[EB/OL].china.maximintegrated.com,1998,6.

[8]劉志宇.基于FPGA的DDS雙通道波形發生器[D].哈爾濱:哈爾濱理工大學,2008.

[9]Data sheet of MAX293[EB/OL].china.maximintegrated.com,2006,08.

[10]High-Speed Programmable Gain Instrumentation Amplifier[EB/OL].www.ti.com.cn/product/cn/pga206,1995,05.