EDA設(shè)計(jì)中的層次化設(shè)計(jì)方法

胡 青,黃 勤,唐 丹,王延川

(重慶大學(xué) 自動(dòng)化學(xué)院信息工程與自動(dòng)化系,重慶 400030)

隨著電子技術(shù)的飛速發(fā)展,EDA技術(shù)借助硬件描述語(yǔ)言對(duì)FPGA和CPLD芯片進(jìn)行了編程,徹底改變了數(shù)字系統(tǒng)的設(shè)計(jì)實(shí)現(xiàn)方法[1-3]。國(guó)內(nèi)多所高校開(kāi)設(shè)了EDA設(shè)計(jì)的相關(guān)課程,在教學(xué)實(shí)踐過(guò)程中發(fā)現(xiàn)了一些問(wèn)題,見(jiàn)參考文獻(xiàn)[4-7]。EDA技術(shù)以FPGA或CPLD芯片為編程對(duì)象,應(yīng)用Quartus等開(kāi)發(fā)軟件,采用層次化設(shè)計(jì)方法完成數(shù)字系統(tǒng)設(shè)計(jì)[8-10]。本文以Quartus II為開(kāi)發(fā)軟件,詳細(xì)說(shuō)明層次化設(shè)計(jì)步驟和實(shí)現(xiàn)方法,并以秒表設(shè)計(jì)為例,演示了層次化設(shè)計(jì)方法的應(yīng)用。

1 層次化設(shè)計(jì)的重要性

層次化設(shè)計(jì)將整個(gè)設(shè)計(jì)任務(wù)按功能劃分為多個(gè)子模塊分別實(shí)現(xiàn)和驗(yàn)證,大大降低了設(shè)計(jì)和仿真驗(yàn)證的難度[11]。更重要的是,只有掌握了層次化設(shè)計(jì)方法才能將一些常用的基本功能,如定時(shí)器、鎖存器、多路開(kāi)關(guān)等設(shè)計(jì)為基本元件,建立自己的元件庫(kù)。這樣在以后的設(shè)計(jì)開(kāi)發(fā)中就可以直接調(diào)用元件庫(kù)中的元件。豐富實(shí)用的元件庫(kù)將大大縮短開(kāi)發(fā)進(jìn)程,提高開(kāi)發(fā)效率。

此外,有些硬件功能必須通過(guò)宏功能模塊才能使用,如ROM存儲(chǔ)器、LPM加法器等。Quartus提供了MegaWizard Plug-in Manager工具,幫助用戶(hù)根據(jù)自己的需求新建和編輯宏功能模塊的設(shè)計(jì)文件,但用戶(hù)必須掌握了層次化設(shè)計(jì)實(shí)現(xiàn)方法,才能在自己的設(shè)計(jì)文件中調(diào)用宏功能模塊。

2 EDA的層次化設(shè)計(jì)方法

2.1 層次化設(shè)計(jì)思想

傳統(tǒng)的硬件設(shè)計(jì)就是選擇合適的元件,在印制電路板上將多個(gè)元件連接起來(lái),實(shí)現(xiàn)某個(gè)具體的功能。這種設(shè)計(jì)思想在EDA技術(shù)中依然適用,并且更加靈活。層次化設(shè)計(jì)方法是將具體的設(shè)計(jì)任務(wù)按功能分成多個(gè)獨(dú)立的模塊,分別實(shí)現(xiàn),經(jīng)過(guò)時(shí)序仿真驗(yàn)證無(wú)誤后,再以這些模塊為基本元件,完成整個(gè)設(shè)計(jì)任務(wù)。隨著設(shè)計(jì)經(jīng)驗(yàn)的增加,元件庫(kù)也越來(lái)越豐富,這是設(shè)計(jì)者的寶貴財(cái)富,可以大大縮短開(kāi)發(fā)周期,降低開(kāi)發(fā)難度。

層次化設(shè)計(jì)方法在設(shè)計(jì)任務(wù)時(shí)自頂向下進(jìn)行分析設(shè)計(jì),將任務(wù)劃分為多個(gè)獨(dú)立的子模塊,而實(shí)現(xiàn)時(shí)則是自底向上逐層實(shí)現(xiàn)。

2.2 EDA設(shè)計(jì)的輸入方法

EDA設(shè)計(jì)的輸入方式主要分為兩種:原理圖方式和硬件描述語(yǔ)言方式。

(1)原理圖設(shè)計(jì)輸入是在畫(huà)布上放置元件,用導(dǎo)線將元件引腳連接起來(lái),添加輸入輸出引腳,最終完成設(shè)計(jì)。原理圖設(shè)計(jì)方法比較簡(jiǎn)單、直觀,缺點(diǎn)是Quartus應(yīng)用軟件提供的元件庫(kù)中只有一些常用的基礎(chǔ)元件,完全符合需求的元件比較難找。

(2)硬件描述語(yǔ)言將設(shè)計(jì)者從具體的硬件設(shè)計(jì)細(xì)節(jié)中解脫出來(lái),設(shè)計(jì)者不需要深入了解具體的硬件設(shè)計(jì),只需要用指令描述元件的邏輯功能就能完成功能設(shè)計(jì)。硬件描述語(yǔ)言的出現(xiàn)大大降低了硬件設(shè)計(jì)的難度,用硬件描述語(yǔ)言完成電路設(shè)計(jì)是EDA技術(shù)的核心內(nèi)容,雖然有多種不同的硬件描述語(yǔ)言,但它們沒(méi)有本質(zhì)區(qū)別,都是編寫(xiě)代碼、綜合適配成相應(yīng)的硬件電路。VHDL和Verilog HDL是使用較多的兩種硬件描述語(yǔ)言。本文的設(shè)計(jì)實(shí)例采用的是VHDL描述語(yǔ)言方式。

2.3 層次化設(shè)計(jì)的實(shí)現(xiàn)方法

應(yīng)用層次化設(shè)計(jì)方法完成具體的設(shè)計(jì)任務(wù)時(shí),應(yīng)自底向上逐層實(shí)現(xiàn),以下層設(shè)計(jì)為基礎(chǔ)元件完成上層設(shè)計(jì)。每一層次的設(shè)計(jì)都可以采用原理圖輸入或硬件描述語(yǔ)言輸入。

(1)采用原理圖輸入方式。此時(shí)需要先將下層設(shè)計(jì)包裝成元件,方便在原理圖中調(diào)用。具體步驟:先打開(kāi)下層設(shè)計(jì)文件(原理圖或VHDL),選擇File選單(菜單)—Create/Update子 選 單 (子 菜單)—Create Symbol Files for Current File選項(xiàng),將下層設(shè)計(jì)文件生成對(duì)應(yīng)的元件;然后再新建原理圖設(shè)計(jì)文件完成上層設(shè)計(jì),此時(shí)元件對(duì)話框中在Project文件夾下會(huì)多出剛才生成的元件,調(diào)用它們即完成了上層設(shè)計(jì)。

(2)采用VHDL輸入方式。此時(shí)只需在VHDL文件中用COMPONENT語(yǔ)句聲明要使用的基本元件,然后就可以根據(jù)需要定義多個(gè)元件實(shí)例,并用PORT MAP語(yǔ)句完成端口映射連接即可。元件聲明的作用是說(shuō)明要使用的元件類(lèi)型;元件實(shí)例則等同于在畫(huà)布上放置所需的元件芯片,根據(jù)設(shè)計(jì)需要,同一類(lèi)型的元件可以有多個(gè)實(shí)例;端口映射等同于在畫(huà)布上用導(dǎo)線連接芯片的引腳。

3 層次化設(shè)計(jì)實(shí)例——秒表

以一個(gè)簡(jiǎn)單的秒表設(shè)計(jì)任務(wù)為例說(shuō)明層次化設(shè)計(jì)方法的思路和實(shí)現(xiàn)。秒表可以啟動(dòng)/暫停計(jì)時(shí),復(fù)位則重新開(kāi)始計(jì)時(shí),時(shí)分秒以“X-XX-XX”的形式在7位LED上顯示出來(lái)。7位LED的位選信號(hào)通過(guò)插孔ds1~ds7引出,而段選信號(hào)連在一起,通過(guò)插孔a—h引出,2個(gè)開(kāi)關(guān)分別用作復(fù)位鍵和啟停鍵。對(duì)FPGA芯片編程可以實(shí)現(xiàn)秒表功能,并控制LED顯示。

3.1 秒表的層次化設(shè)計(jì)分析

首先分析設(shè)計(jì)任務(wù),將其劃分為多個(gè)獨(dú)立的子模塊。按功能劃分,這個(gè)設(shè)計(jì)任務(wù)明顯可分為兩大模塊:秒表模塊和LED顯示控制模塊。而在秒表模塊中的時(shí)、分、秒都是計(jì)數(shù)器,為了方便LED顯示,可以用分、秒的十位和個(gè)位分別實(shí)現(xiàn),這樣只需要用3個(gè)計(jì)數(shù)值為0~9的mod 10計(jì)數(shù)器和2個(gè)計(jì)數(shù)值為0~5的mod 6計(jì)數(shù)器,就可以完成秒表功能。圖1為層次設(shè)計(jì)框圖。

圖1 秒表的層次設(shè)計(jì)框圖

3.2 秒表的層次化設(shè)計(jì)實(shí)現(xiàn)

實(shí)現(xiàn)時(shí)應(yīng)該自底向上,先實(shí)現(xiàn)下層模塊,再調(diào)用下層設(shè)計(jì)完成上層設(shè)計(jì)。

3.2.1 最底層的計(jì)數(shù)器設(shè)計(jì)

用VHDL編程分別實(shí)現(xiàn)mod 6和mod 10定時(shí)器設(shè)計(jì),文件名分別為mod6.vhd和mod10.vhd。

3.2.2 第2層的秒表模塊設(shè)計(jì)

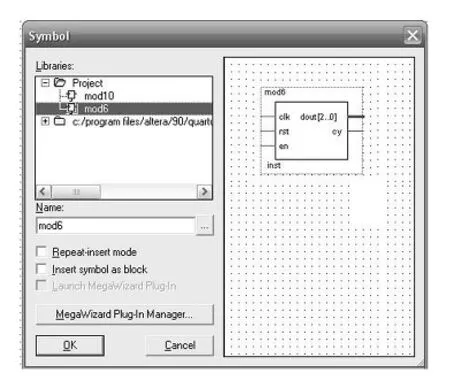

(1)用原理圖輸入方式完成。先打開(kāi)mod6.vhd文件,點(diǎn)擊選單生成相應(yīng)的symbol文件;再打開(kāi)mod10.vhd文件,同樣點(diǎn)擊選單生成symbol文件;最后新建原理圖文件timer.bdf,此時(shí)雙擊畫(huà)布的空白區(qū)域,彈出的Symbol窗口,在Project文件夾下就多了mod6和mod102個(gè)元件,如圖2所示。

在畫(huà)布上放置3個(gè)mod10元件,2個(gè)mod6元件,添加輸入輸出接口,并將它們用導(dǎo)線連接,就完成了秒表模塊的設(shè)計(jì)。

(2)用VHDL完成。新建VHDL文件,文件名為timer.vhd。只需要在結(jié)構(gòu)體中給出mod 6和mod 10的元件聲明,然后根據(jù)需要定義2個(gè)mod 6和3個(gè)mod 10的實(shí)例,參考程序如下。

圖2 生成計(jì)數(shù)器元件后的Symbol窗口

此外Quartus可以自動(dòng)生成元件聲明語(yǔ)句,只需打開(kāi)元件的設(shè)計(jì)文件,選擇File選單——Create/Update子選單——Create VHDL Component Declaration File for Current File選項(xiàng),就會(huì)在項(xiàng)目文件夾下生成與設(shè)計(jì)文件同名、后綴為.cmp的文件;打開(kāi)該文件,將內(nèi)容復(fù)制粘貼到當(dāng)前層次設(shè)計(jì)的VHDL文件中即可。

3.2.3 實(shí)現(xiàn)7位LED控制器設(shè)計(jì)

用VHDL完成LED顯示控制模塊,文件名為ledctrl.vhd。由于篇幅限制,省略具體代碼,只給出LED控制器的實(shí)體定義。

輸入引腳en控制LED是否顯示;輸入時(shí)鐘信號(hào)clk的周期控制每一位LED的顯示時(shí)間,7位LED每次只有一位顯示,具體顯示的數(shù)值由din1~din7決定;輸出引腳ds和seg分別控制LED的位選和段選。

din1~din7端口輸入的數(shù)據(jù)分別顯示在從右到左的第1位~第7位LED上。若輸入數(shù)據(jù)在”0000”~“1001”之間LED則顯示對(duì)應(yīng)的字形;輸入為”1010”LED則顯示“—”;若為其他數(shù)據(jù)LED不顯示。當(dāng)clk信號(hào)頻率在1kHz左右時(shí),視覺(jué)暫停效果使得看上去7位LED同時(shí)顯示不同的數(shù)值。

3.2.4 實(shí)現(xiàn)最頂層的秒表設(shè)計(jì)

以timer和ledctrl為基礎(chǔ)元件完成整個(gè)秒表設(shè)計(jì)和顯示,需要將timer元件的輸出端口與ledctrl元件的輸入端口相連,而timer元件的輸出secH、minH為3位總線,ledctrl元件的din1~din7均為4位總線,2個(gè)總線位數(shù)不一致時(shí)不能直接連接。第6位和第3位LED始終顯示“—”,即din6和din3的輸入始終為“1010”,需要向端口輸入常數(shù)。

(1)原理圖中的總線、分線和常數(shù)。原理圖中需要分別連接某總線端口的各位信號(hào)線時(shí),可以將元件端口用總線引出并命名,例如將ledctrl元件中的din2用總線引出并命名為d2[3..0]。d2為總線的名稱(chēng),[3..0]說(shuō)明該總線為4位;然后就可以用d2[3]、d2[2]、d2[1]和d2[0]分別表示d2總線中的各位信號(hào)線。

電路圖中的常數(shù)意味著信號(hào)固定接地(GND)或接電源(VCC),在Symbol對(duì)話框中輸入 GND或VCC,就能在原理圖上放置地或電源,再用導(dǎo)線連接即可。

圖3將timer元件中3位的secH與ledctrl元件中din2的低3位相連,din2的最高位接地。為突出連接,將相關(guān)部分用紅色框出。

(2)VHDL中的總線、分線和常數(shù)。用VHDL實(shí)現(xiàn)最頂層秒表設(shè)計(jì)的部分程序段如下,相關(guān)代碼用紅色框出。

圖3 3位總線與4位總線之間的連接

4 結(jié)束語(yǔ)

EDA技術(shù)徹底改變了數(shù)字系統(tǒng)的設(shè)計(jì)實(shí)現(xiàn)方法,硬件編程語(yǔ)言降低了硬件設(shè)計(jì)的難度和復(fù)雜度,而層次化設(shè)計(jì)方法自頂向下將設(shè)計(jì)任務(wù)分解為獨(dú)立的功能模塊分別實(shí)現(xiàn)和仿真驗(yàn)證,用戶(hù)可建立自己的元件庫(kù),重復(fù)利用以往的設(shè)計(jì)成果,大大提高了設(shè)計(jì)的靈活性和效率,縮短了設(shè)計(jì)周期。

(References)

[1]趙輝.基于EDA技術(shù)的數(shù)字系統(tǒng)設(shè)計(jì)[J].電子設(shè)計(jì)工程,2012,20(2):34-37,41.

[2]趙剛,何志敏,陳利學(xué).基于FPGA的EDA綜合實(shí)驗(yàn)系統(tǒng)設(shè)計(jì)[J].微計(jì)算機(jī)信息,2012,28(1):49-51.

[3]潘松,黃繼業(yè).EDA技術(shù)實(shí)用教程[M].北京:科技出版社,2006.

[4]牛軍浩,胡聰,殷賢華.EDA分層教育方法改革[J].電氣電子教學(xué)學(xué)報(bào),2011,33(6):115-116,119.

[5]任國(guó)鳳.項(xiàng)目式教學(xué)法應(yīng)用于EDA本科教學(xué)的探索[J].太原師范學(xué)院學(xué)報(bào):自然科學(xué)版,2011,10(4):158-160.

[6]張惠國(guó),潘啟勇,華強(qiáng),等.EDA課程層入式教學(xué)及實(shí)驗(yàn)平臺(tái)建設(shè)[J].常熟理工學(xué)院學(xué)報(bào):2011(12):107-109.

[7]張艷,靳孝峰.對(duì)EDA技術(shù)課程教學(xué)改革的探討[J].教育與職業(yè),2011(21):143-144.

[8]張艷春.數(shù)字電子系統(tǒng)的EDA設(shè)計(jì)方法研究[[J].現(xiàn)代電子技術(shù):2009,32(17):188-190.

[9]王曉峰.可編程邏輯器件及硬件描述語(yǔ)言的EDA方法[J].長(zhǎng)春大學(xué)學(xué)報(bào),2005,15(4):14-16.

[10]孟中.基于EDA層次化設(shè)計(jì)方法的出租車(chē)計(jì)費(fèi)器設(shè)計(jì)[J].現(xiàn)代電子技術(shù),2011,34(16):23-24,30.

[11]王戎丞,陳可中,明鑫.基于VHDL的數(shù)字頻率計(jì)的設(shè)計(jì)與實(shí)現(xiàn)[J].現(xiàn)代電子技術(shù),2005,28(15):102-104.