基于FPGA 的I2C SLAVE 模式總線的設計

魏騰飛

(西安電子科技大學,西安,710000)

0 引言

由于在嵌入式系統開發中越來越多的應用到FPGA,而一些嵌入式CPU,比如STM32 為了降低成本,減小封裝尺寸,沒有外接專門的CPU 讀寫總線,而只提供了一些如SPI 和I2C 的接口。而且在應用中經常有數據要配置到FPGA 中,如FPGA 中的應用配置寄存器,和配置表項等,都需要CPU 配置。這些數據的數據量不大,速度也不要求很高,很適合用I2C 總線來配置。I2C 總線是Philips 公司設計的一種控制和配置內部IC 雙向兩線的串行總線。主要特點是接口信號線較少,但是其數據的傳送速率不是很高,其高速模式下為3.4Mb/s。應用于配置FPGA 比較適合。在通常的應用中嵌入式CPU 作為MASTER 模式的主器件,FPGA 作為SLAVE 模式的從器件。通過使用I2C 總線,減少了CPU 和FPGA 的連線,而且嵌入式CPU 一般有內含I2C總線控制器,使得CPU 和FPGA 間的通訊硬件電路簡化。

1 I2C SLAVE 模式整體結構的分析設計

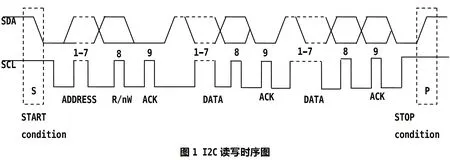

I2C 總線要求兩條信號線,一條串行數據線 SDA,一條串行時鐘線 SCL。通過串行方式傳送數據。它是一個多主器件的總線,如果兩個或更多主器件同時傳輸數據,可以沖突檢測和仲裁。為簡化設計和滿足應用要求,該設計實現一個標準I2C總線的子集。完成1 字節的單次讀寫和連續讀寫功能。所以這就要求應用中的I2C 總線上只能有一個主器件,而FPGA 邏輯則只能當成從器件。I2C 總線的兩條信號線都是開漏的,必須外接上拉電阻,以保證總線空閑時,總線都處于高電平。I2C的讀寫時序圖如圖1。

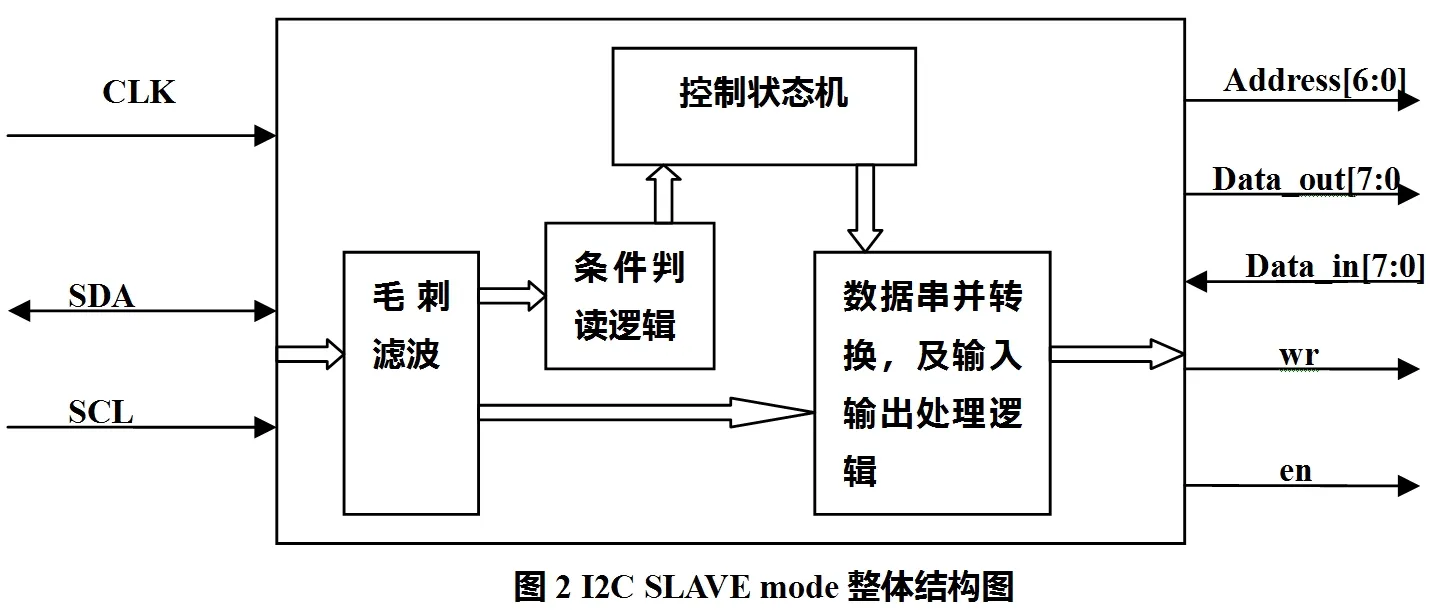

從圖1 中可以看出,總線的起始條件為在SCL 為高電平時,SDA 拉低產生一個下降沿。而總線的停止條件為在SCL 為高電平時,SDA 釋放由上拉電阻產生一個上升沿。在快速模式下,SCL 時鐘頻率最大值為400KHz,SCL 時鐘的低電平周期最小為1.3μs,SCL 時鐘的高電平周期最小為0.6μs。在輸入端,輸入濾波器必須抑制的毛刺脈寬最大值為50ns。由于SCL是由主器件CPU 的內置I2C 模塊產生的,所以SCL 的時序肯定符合要求。而FPGA 要采樣SCL 和SDA 信號,那么FPGA 的采樣時鐘頻率至少要為SCL 頻率的2 倍以上。再加上抑制的毛刺脈寬最大值為50ns。當FPGA 的系統時鐘為100MHz 時,端口以100MHz 的頻率采樣信號,遠遠大于快速模式下SCl 的400KHz,抑制的毛刺也將在5個時鐘周期內處理。而且FPGA內部邏輯一般都工作在100MHz 以上,所以I2C 模塊的系統時鐘可以直接使用FPGA 的系統時鐘,可以省去時鐘轉化模塊,簡化處理。當I2C 總線讀FPGA 時,總線主器件在發送完第一個字節,FPGA 回復ACK 后,緊接著就要FPGA 輸出相應的數據,所以在FPGA 邏輯發出ACK 的同時就要開始,FPGA 的內部尋址和讀取相應的數據,在SCL 時鐘頻率最大值為400KHz 時,FPGA 的系統時鐘為100MHz,那么FPGA 的內部邏輯有約250個時鐘周期的尋址時間,這個時間是完全夠用的。I2C SLAVE mode 整體結構圖如圖2。接口信號的說明如表1。

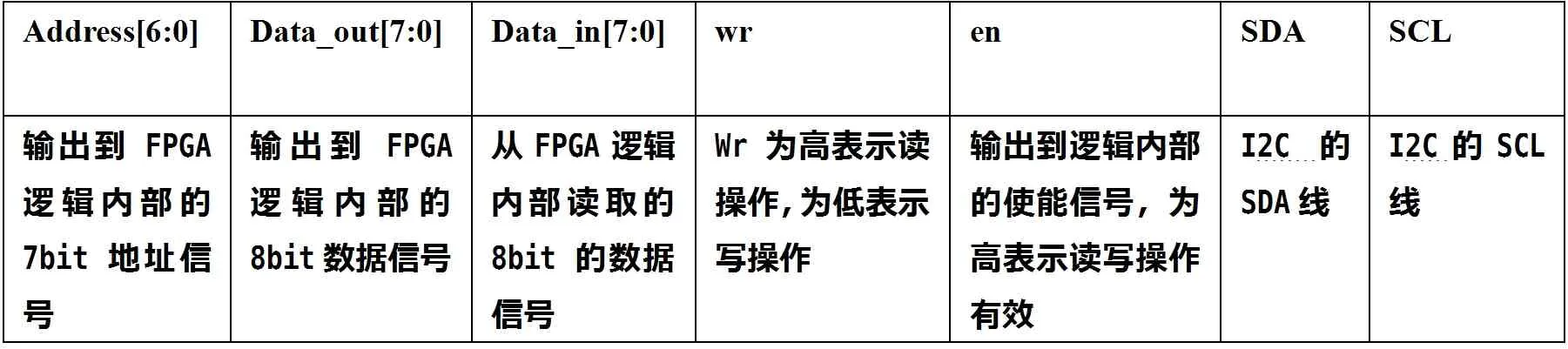

表1 I2C SLAVE 模塊接口信號說明

2 I2C SLAVE 模式控制器的設計與實現

2.1 I2C SLAVE 控制器的接口實現

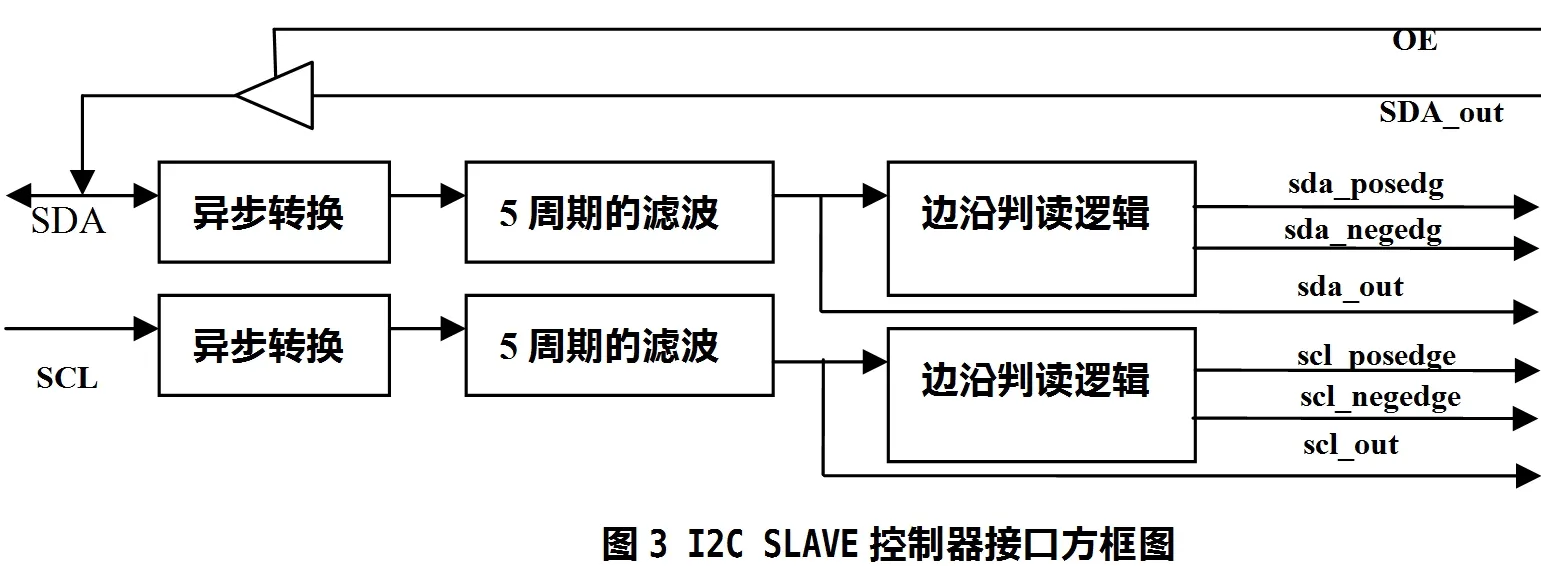

I2C SLAVE 控制器的接口部分主要包括,信號異步時鐘域的轉換。輸入濾波器,用來抑制毛刺。及SDA 線的雙向轉換。由于SDA 的PIN 是雙向的,所以一定要分配在FPGA 的IO BLOCK塊中,只有IO BLOCK 中有雙向的硬件結構。因為SDA 和SCL信號的相位相對于FPGA 邏輯的系統時鐘的相位關系是不確定的。所以一定要進行異步時鐘域的轉換,以防止輸入的寄存器出現亞穩態,它會使邏輯處在某個不確定的狀態。此外FPGA的系統時鐘頻率比較高,對輸入的毛刺比較敏感,故輸入端要加入濾波器。接口部分的框圖如圖3

異步時鐘域的轉換,采用兩級寄存器的結構。輸入濾波器采用5 級寄存器的結構。當采樣到連續5個高電平時,輸出才為高電平,否則為低電平。接口部分的寄存器全都用FPGA 的系統時鐘驅動。

2.2 I2C SLAVE 控制邏輯的實現

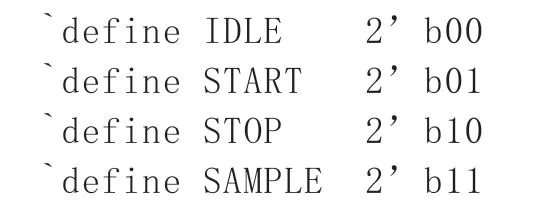

I2C SLAVE 控制邏輯狀態機是整個模塊的核心,所有I2C 總線相應的控制都由其完成。狀態機有四個狀態:IDLE,START,SAMPLE 和STOP 組成。Verilog 的定義如下:

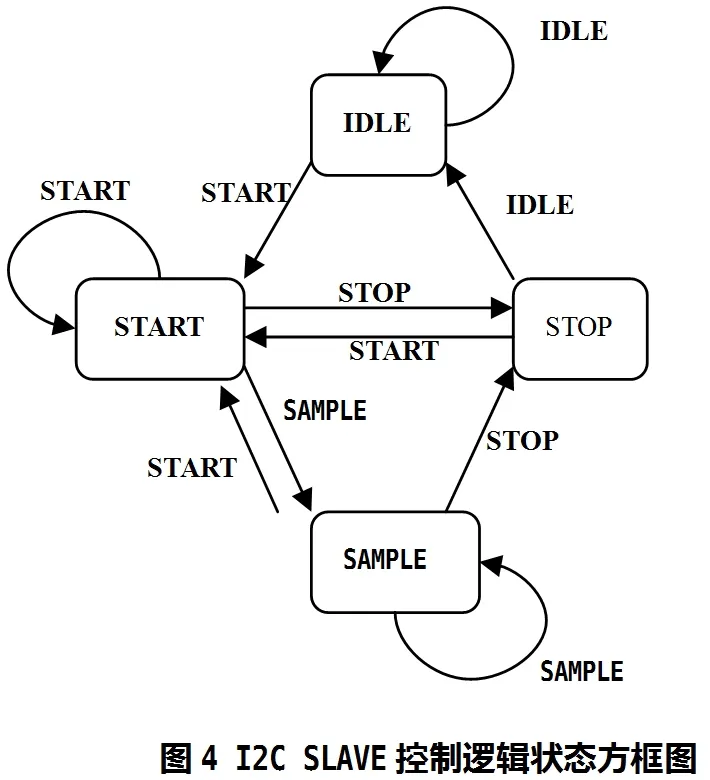

下面介紹各個狀態的功能。當I2C 總線無任何操作時控制器在IDLE 狀態下,并保持。當接口邏輯判斷到START 條件時,控制器跳轉到START 狀態下,并做好接受第一個字節的準備,包括初始化bit 計數器。接著開始接受第一個字節包含7bit的地址和1bit 的讀寫狀態位。當采集完第一個字節后,控制器跳到SAMPLE 狀態下,開始執行數據字節的接受或發送。是接受或發送的狀態由前一字節的最后1bit 的讀寫狀態位決定。當讀寫狀態位為高時,表示I2C 總線的讀操作,FPGA 邏輯發送數據。讀寫狀態位為低時,表示I2C 總線的寫讀操作,FPGA邏輯接受數據。接著FPGA 邏輯發出一個ACK 信號后,表示可以進行讀寫操作。那么就進入到SAMPLE 狀態下,正常讀或寫一個字節(也可以連續的讀寫多個字節,對此沒有限制)。在完成8bit 數據讀寫后,I2C 的主器件會發出一個STOP 條件操作。fpga 邏輯收到后,就跳轉到STOP 狀態,并在幾個時鐘周期后,自動跳轉到IDLE 狀態下。從而完成一個完整的I2C 總線的讀或寫操作。

當然也包括一些異常處理,以防止狀態機處在一個不確定的狀態下。在SAMPLE 狀態下如果遇到意外的START 條件時,即上次的總線操作沒有完成就開始了下次的操作,則控制狀態機會跳轉到START 狀態下,而開始接受這次新的總線操作,而上次的操作為無效。由如在SAMPLE 狀態下,但是又收到一個START 條件。還有如在STOP 狀態收到一個START 條件,處理也和上面一樣。下圖4 介紹了I2C SLAVE 控制邏輯狀態機的狀態跳轉圖。

如上圖所示,在 SAMPLE 狀態下,可以連續的讀寫數據,而地址是在讀寫完一個字節后由FPGA 邏輯自動加1 的。這樣做使得I2C 總線的一次操作就可以連續對多個字節讀或寫。提高的總線的使用效率。

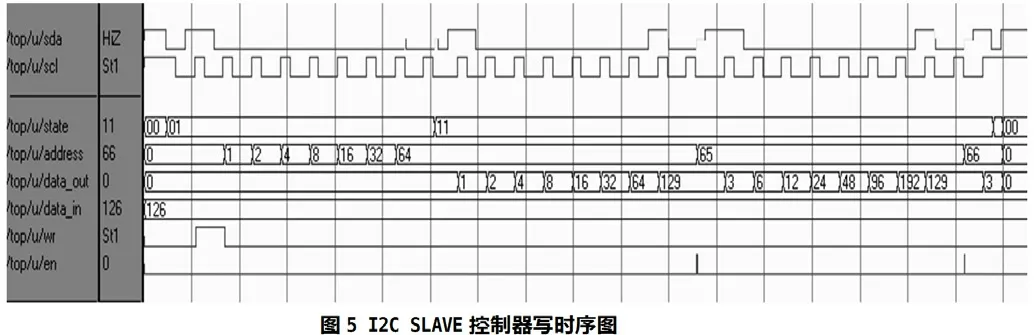

以下是在modelsim6.0 下進行的行為級仿真的時序圖。由自行編制的I2C 總線主器件BFM 驅動進行測試。圖5 I2C SLAVE 控制器寫時序圖。圖6 I2C SLAVE 控制器讀時序圖。

3 結論

在Altera 的Cyclone II 系列中用Quartus II 12.0生成的模塊時鐘頻率可達到180MHz,占用的資源Total combinational functions 為83個,Total registers 為41個。而實際應用在100MHz 左右。在項目應用中,操作簡便,效果不錯。加快了項目的進度。

[1]Altera.Cyclone II Device Handbook,2010.

[2]Altera.Quartus II 12.0 手冊,2012.

[3]Philips Semiconductors.The I2C-bus Specification Version2.1,2000.