一種DDR SDRAM控制器的設計

金新強,白雪飛 ,張 璠

(1.中國科學技術大學 電子科學與技術系,安徽 合肥230027;2.中國科學技術大學 信息科學實驗中心,安徽 合肥230027)

雙倍數據速率同步動態隨機存儲器DDR SDRAM(Double Data Rate SDRAM)以其大容量、高速率和良好的兼容性在通用計算機系統和嵌入式系統領域得到了廣泛應用,越來越多的片上系統(SoC)中集成了DDR SDRAM控制器。

DDR SDRAM是電子設備工程聯合委員會JEDEC制定的內存技術標準[1],采用差分時鐘技術,具有兩倍數據預讀取,在時鐘的上升沿和下降沿各傳輸一次數據,數據傳輸速率為系統時鐘的兩倍,從而大大提高了數據傳輸速率。

1 DDR SDRAM控制器的關鍵技術

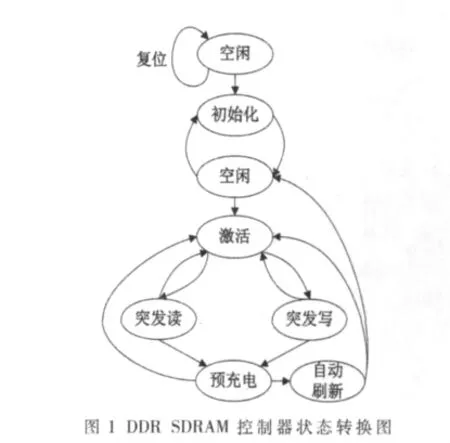

本文設計的DDR SDRAM控制器支持以下操作:空操作(Nop)、激 活 操 作(Active)、突 發 寫(Burst Write)、突 發 讀(Burst Read)、自動刷新(Auto Refresh)、預充電(Precharge)、模式寄存器配置(Mode Register Set)等。所有的操作命令都通過信號線ras_n、cas_n和we_n共同控制[2]。DDR SDRAM 控制器狀態轉換圖如圖1所示。

初始化完成之后,控制器通過 ras_n、cas_n和 we_n發送Bank激活命令,然后片選和Bank尋址,同時地址線發送行地址選通行。等待tRCD后,發送突發讀寫命令,同時地址線發送起始列地址,其中A10為帶自動預充電使能位,如果自動預充電使能位有效,則在突發傳輸結束后自動預充電,否則不進行自動預充電。預充電用來關閉某個打開的行或者所有打開的行。被預充電的行可以在tRP之后重新被訪問[3]。

刷新操作分為兩種:自動刷新(Auto Refresh)與自刷新(Self Refresh)。自動刷新命令用來周期性地刷新DDR SDRAM,以保持其內部的數據不丟失。由于刷新是基于行進行的,64 ms之后再次對同一行進行刷新,如此周而復始進行循環刷新。自刷新主要用于休眠模式低功耗狀態下的數據保存,在發出自刷新命令時,將時鐘使能cke置于無效狀態進入自刷新模式,此時不再依靠系統時鐘工作,而是根據內部的時鐘進行刷新操作[4]。

2 DDR SDRAM控制器的設計

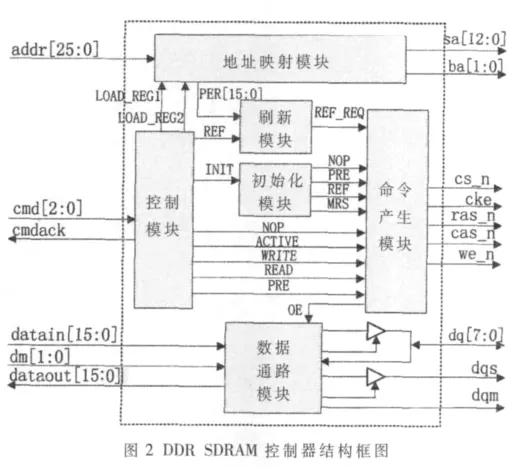

DDR SDRAM控制器的功能包括:初始化DDR SDRAM,簡化DDR SDRAM復雜的讀寫時序,在DDR SDRAM接口的時鐘雙邊沿觸發數據和時鐘單邊沿觸發數據之間轉換,產生周期性的刷新命令來維持DDR SDRAM內的數據不丟失。本文設計的DDR SDRAM控制器包含以下幾個模塊:控制模塊、刷新模塊、初始化模塊、命令產生模塊、數據通路模塊和地址映射模塊。DDR SDRAM控制器的結構框圖如圖2所示。

2.1 控制模塊

控制模塊寄存從主機系統發來的命令并解碼,發送解 碼 過 的 NOP(空 操 作)、ACTIVE(激 活)、WRITE(突 發寫)、READ(突發讀)、PRE(預充電)命令給命令產生模塊,發送解碼過的REF(自動刷新)給刷新模塊,發送解碼過的 INIT(初始化)命令給初始化模塊,而 LOAD_REG1和LOAD_REG2命令則在解碼后發送給地址映射模塊。

2.2 刷新模塊

刷新模塊用于生成周期性的自動刷新命令請求給命令產生模塊。刷新模塊包含一個16 bit的刷新計數器和控制電路,刷新計數器是一個16 bit的減法計數器,發送LOAD_REG2命令時,在地址映射模塊中通過ADDR的相應位加載到寄存器REG2中,然后通過信號PER[15:0]發送給刷新計數器。 PER[15:0]中是一個 16 bit的數值,表示控制器發出相鄰兩個自動刷新命令之間的時間間隔,即刷新周期。刷新計數器向下計數,當計數到0時,刷新請求信號REF_REQ被置為有效并保持直到命令產生模塊響應刷新請求為止。之后,刷新計數器重新載入刷新周期PER[15:0],開始新一輪的計數。

2.3 初始化模塊

初始化模塊采用初始化狀態機實現DDR SDRAM的初始化過程,初始化操作按照DDR SDRAM初始化的步驟進行。采用一個由100 MHz系統時鐘控制的16 bit初始化計數器來控制初始化狀態機中各個狀態的執行時間,首先等待 200 μs,設置初始化計數器為20 000(200 μs=20 000×1/100 MHz),然后將 cke置高,同時初始化狀態機進入了NOP(空操作)狀態,發送PRE(預充電)命令預充電所有Bank;經過tRP的預充電時間后發出兩次MRS(模式寄存器配置)命令分別設置模式寄存器和擴展模式寄存器,等待tMRD的時間后發送PRE(預充電)對所有Bank進行預充電;經過tRP的時間后至少發送兩次REF(自動刷新)命令進行自動刷新,之后發送MRS(模式寄存器配置)命令對模式寄存器進行配置,至此完成初始化過程。

2.4 命令產生模塊

命令產生模塊包含命令仲裁邏輯和命令解碼邏輯。命令仲裁邏輯用來仲裁控制模塊發送的解碼后的命令、初始化模塊發送的初始化過程所需要的命令以及刷新模塊發送的刷新請求。刷新模塊發來的刷新請求具有最高優先級,其次是初始化模塊發送的命令請求,控制模塊發送的命令具有最低優先級。如果在初始化模塊或者控制模塊發送的命令執行過程中接收到自動刷新命令,則這個自動刷新命令保持不被執行直到初始化模塊或者控制模塊發送的命令操作結束。

命令解碼邏輯將經過命令仲裁邏輯仲裁后的命令解碼成DDR SDRAM能識別的操作命令。發送這些操作命令時,時鐘使能信號cke置為高電平,片選信號cs_n置為低電平有效,具體的操作命令由信號線cas_n、ras_n和we_n來共同解碼。

2.5 數據通路模塊

數據通路模塊為DDR SDRAM突發讀寫操作提供數據接口的時鐘域和位寬轉換。讀數據通路中,從DDR SDRAM發送的數據信號 dq[7:0]的采樣時鐘為200 MHz,經過二級寄存器后分為兩路數據進入100 MHz時鐘域,一路在時鐘的上升沿采樣,一路在時鐘的下降沿采樣,再經過一級寄存后同步經過數據選擇器,調整數據順序,最后經過兩級緩存輸出給 dataout[15:0]。

寫數據通路中,輸入數據 datain[15:0]和數據屏蔽輸入信號dm[1:0]的采樣時鐘為 100 MHz,先后經過兩級緩存寄存器和數據選擇器將一倍時鐘域的數據轉換到二倍時鐘域,再經過兩級緩存輸出到數據輸出信號dq[7:0]和數據屏蔽輸出信號dqm。

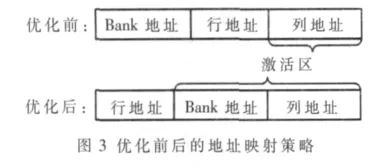

2.6 地址映射模塊及地址映射的優化

控制器對DDR SDRAM的訪問尋址傳統上采用順序的地址映射方式,即Bank地址、行地址、列地址分別從高地址到低地址排列[5]。由于DDR SRAM的數據存儲具有很強的局部性,主機系統對DDR SDRAM的連續突發訪問通常集中在相近的一塊存儲區域,當采用順序的地址映射方式時,先訪問某個Bank的一行,然后訪問該Bank中的下一行,就需要預充電關閉當前行并激活下一行,才能突發訪問下一行,因此內存訪問效率很低。

DDR SDRAM可以同時激活多個Bank,將連續的訪存操作映射到不同的Bank中,避免對同一Bank突發訪問而出現行沖突,利用多個Bank提供的行緩沖區來提高訪存性能。基于這種思想,本設計采用行地址、Bank地址、列地址分別從高地址到低地址排列的映射方式,如圖3所示。當訪問下一行時,由于該行在新的Bank中,不需要將原來的行關閉,只需要激活新的行;當再次訪問上一行時,因為該行仍然處于激活狀態,只需要直接發送突發讀寫命令。

將DDR SDRAM中已經激活可以直接訪問的最大存儲區域稱為激活區,激活區越大,DDR SDRAM的局部性突發訪問的效率越高。假設Bank地址為b bit,列地址為 c bit,數據線為 d bit,則優化前采用順序地址映射方式的激活區大小為d×2c(bit),優化后的激活區達到d×2b+c(bit),從而大大提高了突發訪問的效率。

3 設計實現結果

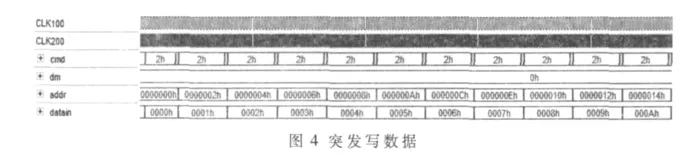

本設計經過邏輯綜合和布局布線之后,采用0.18 μm CMOS工藝流片。在PCB板上,使用Altera公司Stratix II系列FPGA發出測試激勵給DDR SDRAM控制器,連接Micron公司型號為MT46V64M8的512 Mbit的DDR SDRAM內存芯片,對DDR SDRAM控制器芯片進行測試。

DDR SDRAM控制器測試工作時鐘達到200 MHz,使用FPGA內置邏輯分析儀SignalTap II截取突發寫數據,如圖 4所示。命令信號cmd[2:0]輸入 0x2,表示突發寫命令,地址信號 addr[25:0]為 0x0000000,0x0000002,0x0000004,0x0000006,0x0000008,0x000000A,0x000000C,0x000000E,0x0000010,0x0000012,0x0000014依次遞增。此時突發寫入的數據信號datain[15:0]依次為0x0000,0x0001,0x0002,0x0003,0x0004,0x0005,0x0006,0x0007,0x0008,0x0009,0x000A。

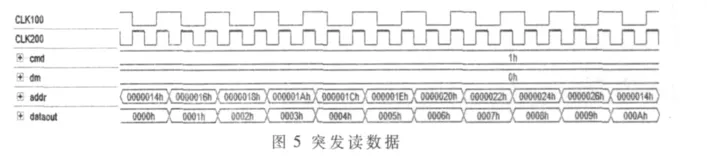

使用FPGA內置邏輯分析儀SignalTap II截取突發讀數據,如圖 5所示。命令信號 cmd[2:0]輸入 0x1,表示突發讀命令,地址信號 addr[25:0]為0x0000000,0x0000002,0x0000004,0x0000006,0x0000008,0x000000A,0x000000C,0x000000E,0x0000010,0x0000012,0x0000014 依次遞增。addr[25:0]信 號 經 過 地 址 映 射 后 輸 出 sa[12:0]和 ba[1:0]給 DDR SDRAM,經過 tRCD和 CL的延時后,突發讀出的數據信號 dataout[15:0]依次為 0x0000,0x0001,0x0002,0x0003,0x0004,0x0005,0x0006,0x0007,0x0008,0x0009,0x000A。

本文給出了一種DDR SDRAM控制器芯片的設計方法,采用一種優化的地址映射策略提高了突發訪問的效率,且流片實現后測試其功能良好,工作頻率達到200 MHz,支持的DDR SDRAM數據信號位寬為8 bit,連續突發讀寫數據傳輸速率為1.6 Gb/s,能滿足系統帶寬要求。

[1]JEDEC Standard.DDR SDRAM specification[DB/OL].(2005-xx-xx)[2013-01-13].http://www.jedec.org.

[2]Micron Technology Inc.DDR SDRAM MT46V64M8 datasheet[DB/OL].(2002-xx-xx)[2013-01-13].http://www.micron.com.

[3]Elpida Memory Inc.How to use DDR SDRAM[DB/OL].(2007-xx-xx)[2013-01-13].http://www.elpida.com.

[4]Micron Technology Inc.General DDR SDRAM functionality[DB/OL].(2001-xx-xx)[2013-01-13].http://www.micron.com.

[5]韋喜波.DDR SDRAM 控制器的設計與驗證[D].哈爾濱:哈爾濱工業大學,2009.