CameraLink接口的高速電子存儲系統設計*

(1.海軍駐鄭州地區軍事代表室 鄭州 450047)(2.中國電子科技集團公司第二十七研究所 鄭州 450047)

1 引言

隨著圖像傳感器制造工藝的不斷提高,數字攝相機的分辨率和幀頻也不斷提高、這使得數字攝相機輸出的數據率也隨之提高,數字攝相機和圖像采集設備之間的通信速率變得非常重要。

在某項目中,前端數字相機分辨率為1024×1024 像素,幀頻高達120幀/秒,8/10/12 位Base CameraLink 輸出,要求將數字相機的圖像采集下來并進行存儲,并具備網絡讀取數據的接口。由此,可以計算出如果攝相機輸出為12位的話,其數據將達到1.44Gbps,對存儲設備的數據通信速率、存儲容量和管理都提出了較高的要求;針對上述要求,筆者設計了基于Nand Flash電子存儲芯片的大容量電子存儲系統,該存儲系統存儲容量達到3.84TB,具有與數字攝像機相連的Base CameraLink通訊接口,同時,具有攝像機視頻數據的管理功能,并具有網絡接口,以FTP 服務器的方式,提供視頻數據文件的下載。

2 存儲系統總體設計構思

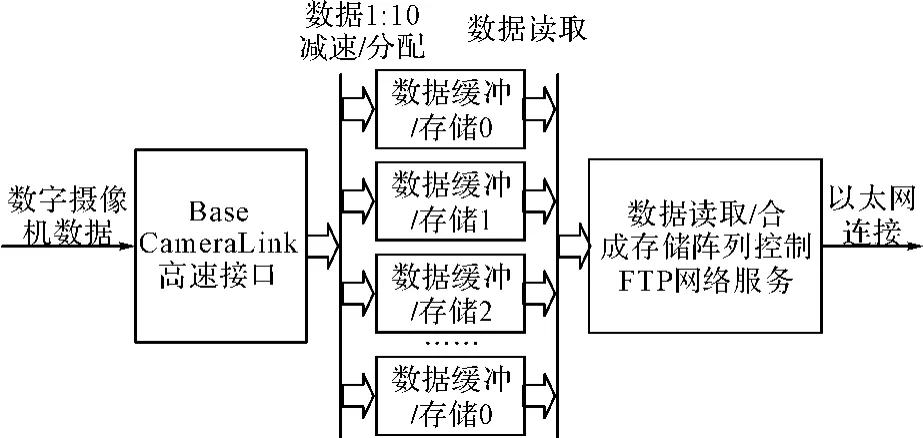

如圖1所示,高速電子存儲系統由Base CameraLink高速接口、控制單元、存儲陣列單元組成。

高速電子存儲系統的Base CameraLink高速接口提供與數字攝像機的高速數據通道,同時完成高速數據的降速分配;讀取/控制單元是高速電子存儲系統的管理核心,完成存儲數據的讀取/合成、存儲陣列控制以及FTP 網絡服務功能;存儲陣列單元是由10塊存儲板組成,單個存儲板設計容量為384GB,高速電子存儲系統總存儲容量達到10×384GB =3.84TB的大小。

圖1 高速電子存儲系統的組成

3 Base CameraLink高速接口[8]

CameraLink協議是一個工業高速串口數據和連接協議,它是各公司達成的一種協議,由美國自動化工業協會AIA 制定、修改和發布,其目的是簡化圖像采集接口,方便高速圖像傳感器和采集系統的鏈接。

CameraLink接口有三種配置方式,即基本(Base)配置、中檔(Medium)配置、全速(Full)配置;主要是解決數據傳輸量的問題,這為不同速度的相機提供了合適的配置和連接方式;其中,基本(Base)配置的有效數據帶寬(時鐘75MHz時),可達1.8Gbps,完全可以滿足系統使用數字攝相機最大1.44Gbps數據量的需要,由此,高速電子存儲系統與攝相機連接的數據接口采用Base CameraLink的形式。

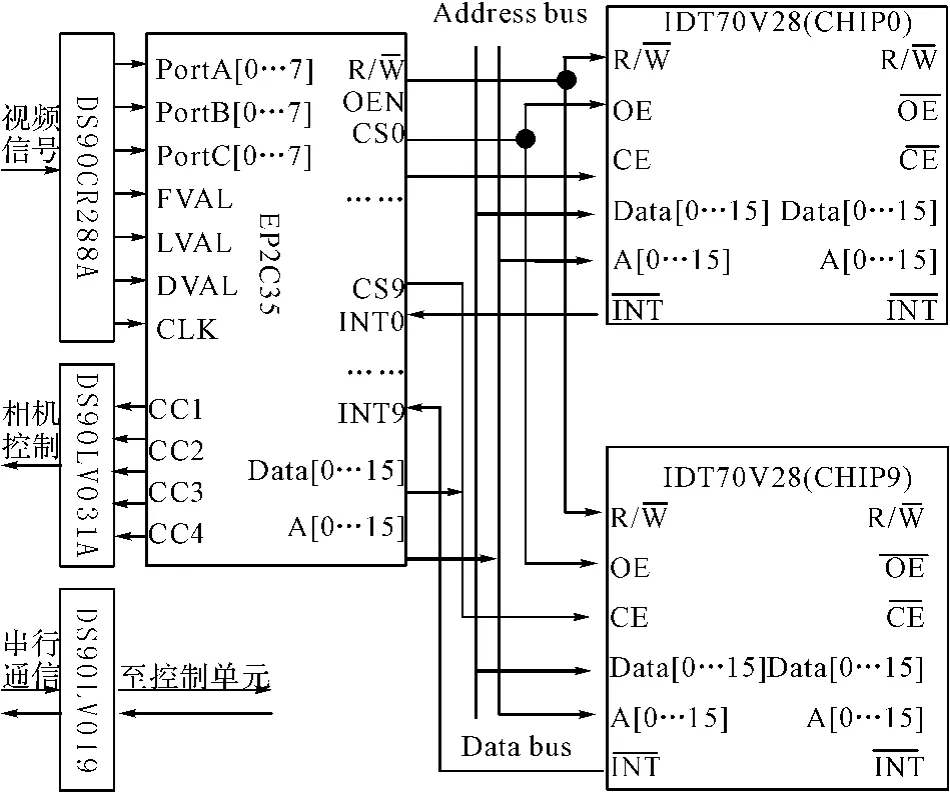

CameraLink接口是基于LVDS(Low Voltage Differential Signaling,低電壓差分信號)標準,在設計高速接口時,需要進行LVDS 電平和LVTTL 電平信號的轉換。系統中,電平信號的轉換采用 NI 公司的DS90CR288A、DS90LV031A 和DS90LV019來實現;其中,DS90CR288A芯片完成視頻信號的轉換,該芯片接收4 對差分信號和1對差分時鐘信號,轉換后輸出28位數據和1路時鐘信號,直接輸出到FPGA 中;DS90LV031A芯片完成FPGA 輸出到攝相機的CC1~CC4 共4 組控制信號的電平轉換;DS90LV019芯片完成攝像機的異步串行通訊接口的電平轉換。

高速電子存儲陣列中Base CameraLink 高速接口的FPGA 芯片完成控制采集時序、數據1∶10減速/分配的功能,把1.44Gbps的高速數據按照圖像幀順序依次進行抽取,平均分為10組后,分別寫入到10片雙口RAM 中,由存儲單元的0~9號存儲板讀取后進行存儲。系統中,FPGA芯片的選取綜合考慮了速度、I/O 管腳數量、片內數據存儲容量等綜合因素,采用了ALTERA 公司的CycloneⅡ系列芯片EP2C35;該芯片擁有35000個邏輯單元、672個引腳、475個用戶自定義I/O 接口、35個嵌入式乘法器和4個鎖相環,是一款集成度極高和功能強大的FPGA 芯片[2]。高達1.44Gbps的高速數據經FPGA 減速/分組后,速率變為144Mbps,通過FPGA 寫入到對應的雙口RAM 中;雙口RAM 是實現在系統間交換數據的一種簡便有效的方法,并且可以避免在大數據量下可能造成數據處理時間延長、實時性差、甚至出現數據擁塞的現象;雙口RAM 選用IDT 公司的64K×16b雙口芯片IDT70V28,在這里,選用較大容量的雙口RAM 芯片,可以有效簡化FPGA 和存儲單元DSP芯片之間的寫入/讀取時序的設計復雜度。高速電子存儲陣列的Base CameraLink 高速接口的設計原理如圖2所示。

圖2 高速接口設計原理圖

4 存儲陣列單元

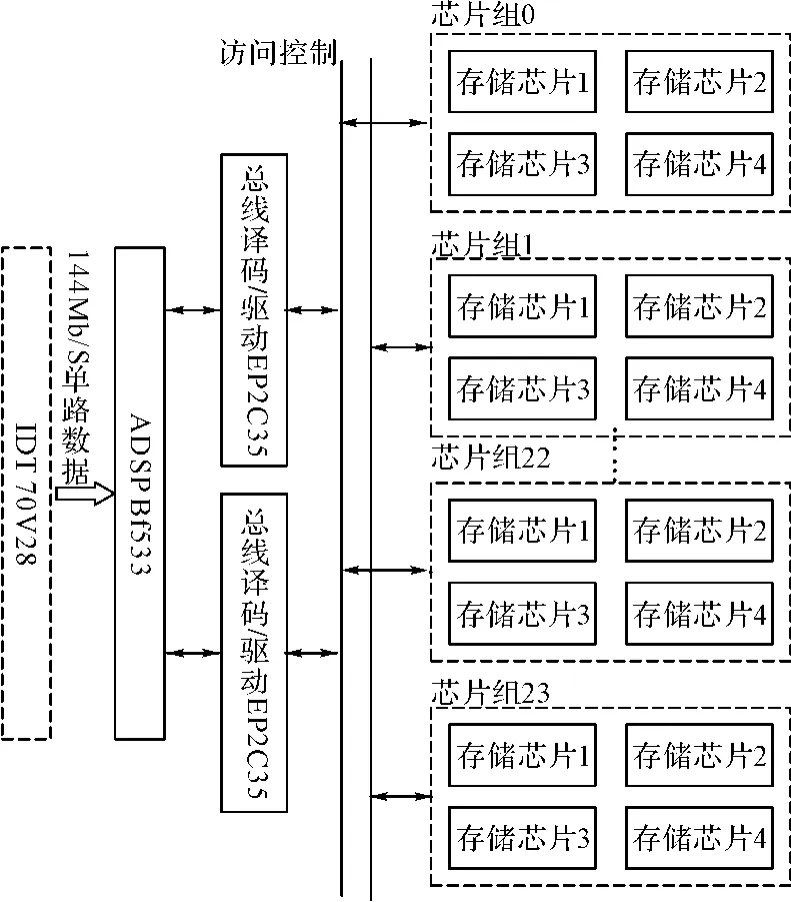

高速電子存儲系統的存儲陣列單元的設計思路是以Nand Flash芯片作為存儲介質,通過高性能DSP和大規模FPGA 完成Nand Flash芯片的讀寫時序的控制,從而構成單個的存儲板,再由10塊相同的存儲板共同組成存儲陣列單元。單塊存儲板的結構框圖如圖3所示。

圖3 存儲板結構框圖

存儲陣列單元的Nand Flash芯片是其核心,每塊存儲板上共有96片Nand Flash存儲芯片分組互聯而成構成,Nand Flash 芯 片 采 用Samsung 公 司 的K9WBG08UIM 芯片,容量為4GB,數據寬度為8位,每頁大小為4KB,可以實現單塊存儲板384GB的存儲容量[3]。

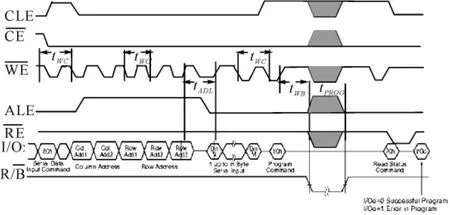

圖4 K9WBG08UIM 芯片頁寫入時序

單塊存儲板上的96片Nand Flash芯片每4片分為一組,共分為24 組,同組的4 片芯片并聯成32 為的數據寬度,這樣做一是可以有效提高Nand Flash 芯片寫入的帶寬,解決Nand Flash芯片寫入/讀取速度較慢的問題,二是可以與DSP控制芯片的32 位數據寬度相匹配,提高數據的讀寫效率。

由圖4可以看出,Nand Flash芯片的tWC最小為25ns,tADL最小為75ns,tWB為100ns,tPROG典型時間為200μs,芯片寫入按照頁進行操作,典型的持續寫入速率為5MB/s,4片并行寫入的速率為20MB/s(160Mbit/s),滿足144Mbps數據源的速率要求。

存儲板上的Nand Flash芯片的訪問控制接口采用了兩片ALTERA 公司的CycloneⅡ系列芯片EP2C35 來實現,Nand Flash芯片采用4個一組,共用一套EP2C35的I/O 引腳驅動,以保證足夠的驅動能力,避免因I/O 引腳上負載過大而造成無法工作;在必要時,兩片FPGA 芯片還可以采用乒乓結構操作,同時進行數據的寫入,把存儲板設計的寫入帶寬提高一倍,使整個存儲系統的數據寫入帶寬達到3.2Gbps。

存儲板的數據收發通過DSP 來實現,這里選用的是ADI公司的ADSP-BF533處理器芯片,ADSP-BF533是較為常用的一款嵌入式多媒體處理器,擁有運算速度高達600MHz的DSP內核,采用ADI與Intel共同開發的MSA體系結構兩個16位乘法器和兩個40位ALU,專門的視頻處理硬件單元和視頻處理指令,豐富的DMA 通道,內嵌大容量高速SDRAM,支持動態電源管理[4]。

存儲板在執行存儲操作時,BF533 將從雙口RAM 中的數據讀取出來,并將數據緩存到SDRAM 中,再通過FPGA 按照Nand Flash芯片的寫入時序,完成存儲數據的寫入存儲。在執行讀取操作時,BF533則通過FPGA 向Nand Flash芯片發送讀操作指令,以讀取指定區域的數據并緩存到SDRAM 存儲器中,然后通過輸入/輸出總線(PPI)發送到存儲/讀取控制單元。

5 讀取/控制單元

高速電子存儲系統的存儲陣列的讀取/控制單元完成陣列內存儲數據的讀取/合成、存儲陣列內數據的文件管理功能以及FTP網絡服務功能。設計時考慮到芯片選用的系列性,讀取/控制單元采用ADSP-BF537處理器為單元的核心,基于Blackfin處理器的BF537處理器具有接口豐富(集成有100MB網絡接口),性能優良等特點,并具有強大的多媒體數據處理能力[5]。ADI公司DSP 處理器的集成開發環境Visual DSP++中嵌入了實時操作系統內核VDK,適合于多任務多線程的嵌入式操作;此外,還提供了一個用于Blackfin系列嵌入式處理器的LwIP協議棧端口,利用它可以快速建立一個嵌入式網絡連接應用。

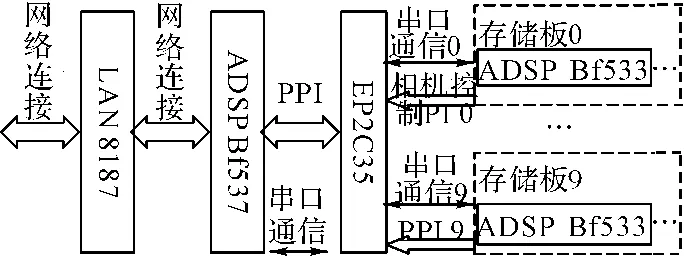

圖5給出了BF537通過網絡芯片LAN8187實現網絡通信和利用處理器自身的PPI接口和串行通信接口實現與存儲板之間的通信和管理。

圖5 BF537與存儲板的通信接口圖

ADI公司的Blackfin系列DSP處理之間的通信,最簡單的方式是采用DSP芯片自帶的PPI接口完成;PPI接口的全稱為 并行外圍接 口(Parallel peripheral Inter-face),是數據高速傳輸專用的半雙工雙向通道,該接口包括16位的數據傳輸線、3個同步信號和一個時鐘信號;速度可以達到66MB/s。

通過PPI接口,高速電子存儲系統實現了讀取/控制單元對存儲板存儲數據的讀取,這里設計中需要面對的難點是需要實現讀取/控制單元1片BF537處理器與存儲板的10片BF533的PPI通信,設計中采用分時復用的方法,訪問控制接口由1 片ALTERA 公司的CycloneⅡ系列芯片EP2C35來實現,為了保證分時復用時的數據傳輸的穩定性,PPI通訊接口設置成單工模式,其時鐘信號和同步信號由BF537來統一設定。讀取控制信息通過SPORTs串口通信口來實現,同樣是通過EP2C35 完成BF537 的SPORTs串口分時復用控制。BF537芯片內部集成了一個以太網的MAC 接口,通過外部擴展以太網物理層接口LAN8187后,可以實現高速電子存儲系統的100/10Mb網絡接口。

6 數據管理

高速電子存儲系統的存儲深度達3.84TB,而前端攝像機的圖像數據是以數據形式存儲的,因此,構建一個適合管理Nand Flash存儲器的文件系統。由于Nand Flash存儲器的擦除次數是有限的(一般是1百萬次),如采用普通的FAT 文件系統,則會出現存儲FAT 系統FAT 表和FRT表的區域過度擦寫而引起失效導致文件系統崩潰的情況;由此,需要通過改進FAT 表和FRT 表的存儲方式,延長存儲器的使用壽命,提高系統存儲的穩定性。

改進設計的FAT 文件系統把FAT 表和FRT 表作為可移動的數據放在某一個區塊內,在Flash的系統信息區中記錄著FAT 表的首地址,并用指針指向它。每次FAT表存儲的位置發生變化時,只需將新位置的首地址添加到系統信息區的空白區域中,再調整指針的指向。這樣避免了FAT 表和FRT 表始終在一個區塊中反復擦寫,導致該區塊被過度使用,縮短存儲器的壽命。

高速電子存儲系統改進的FAT 文件系統包括文件創建、打開等操作函數,用于滿足基本的文件管理操作,可以完成如刪除、拷貝、剪切、下載、陣列格式化等管理功能,這些操作功能可以通過網絡接口實現。

7 FTP服務

高速電子存儲系統可以作為一個FTP的服務器,把所存儲的攝像機視頻數據以文件的形式提供給需要的用戶下載使用。FTP(File Transfer Protocol)作為internet上最早提供的服務之一,至今仍然被廣泛使用,FTP是實現文件傳輸服務的最主要的規范。

FTP協議則采用兩個TCP連接來實現文件的傳輸,這兩個TCP連接一個用來完成文件傳輸的控制命令的傳輸,另外一個用來實現文件的傳輸;然而,有些嵌入式系統的開發環境并不支持FTP協議(如本文所使用的ADSP的集成開發環境Visual DSP++),在此情況下,只能按照FTP協議的約定,利用已有的LwIP 堆棧中的一些基礎函數來構建一個適用于BF537嵌入式處理器的FTP服務器。

設計FTP服務器時,可以根據不同的需求,選擇不同的FTP服務器模式。因為FTP服務器模式決定著設計結構,而不同的設計結構又很大程度地影響著FTP服務器的性能。FTP服務器的模式主要有循環服務器和并發服務器。

循環服務器只適應于最簡單的應用協議,采用客戶輪流等待的工作方式;高速電子存儲系統考慮到嵌入式處理器硬件芯片本身的特點,即在文件下載時,BF537與存儲板的通信只能通過同一套PPI總線進行數據傳輸,因此,設計的FTP服務器的方式是一次只接受一個用戶的下載請求;采用循環服務器模式。

8 結語

CameraLink接口的高速電子存儲系統的設計,成功解決了普通存儲陣列使用時攝像機接口的設計問題,具有高速、體積小、重量輕、抗沖擊、振動性能好的特點,可以實現較為惡劣環境下的應用,如果能提高數據管理和網絡通訊能力,將具有良好的使用前景。

[1]陳鋒.Blackfin系列DSP原理與系統設計[M].北京:電子工業出版社,2004.

[2]Cyclone Device Handbook[EB].Altera Corporation,2003Cyclone系列芯片手冊[EB].Altera公司,2003.

[3]K9XXG08XXM Flash Memory[EB].SUMSUNG ELECTRONICS,2007.3K9XXG08XXM 系列Flash存儲器[EB].三星電子,2003.

[4]ADSP-BF533Blakfin Processor Hardware Reference[EB].Analog Devices.Inc 2006.7ADSP-BF533Blakfin處理器硬件參考手冊[EB].ADI公司,2006,7.

[5]ADSP-BF537Blakfin Processor Hardware Reference[EB].Analog Devices.Inc 2005.1(ADSP-BF537Blakfin 處理器硬件參考手冊[EB].ADI公司,2005,1.

[6]李寧,汪駿發.基于Camera Link的高速數據采集系統[J].紅外,2005,26(7):31-37.

[7]任泰明.TCP/IP協議與網絡編程[M].西安:西安電子科技大學出版社,2004.

[8]沈鴿,王美嬌,嵇曉強.基于CameraLink的視頻圖像采集與傳輸系統[J].微計算機信息,2011(8):108-109.

[9]陳偉,宋燕星.基于LVDS技術的高速數字圖像傳輸系統[J].電子測量技術,2008(11):172-174.

[10]黃曉敏.LVDS驅動器電路設計及硬件實現[D].武漢:華中科技大學,2004.

[11]楊夷梅,楊玉軍.一種基于LDC混沌理論與RSA 的圖像傳輸算法[J].計算機與數字工程,2009,37(2).

[12]王麗華,何利娟,田文英.淺析FTP工作原理及應用技術[J].石家莊職業技術學院學報,2007(8):28-29.