基于FPGA的AD轉換控制器設計

辛鳳艷 孫曉曄

1.河北省科學院應用數學研究所,石家莊 050081;2.石家莊開發區冀科雙實科技有限公司

基于FPGA的AD轉換控制器設計

辛鳳艷1孫曉曄2

1.河北省科學院應用數學研究所,石家莊 050081;2.石家莊開發區冀科雙實科技有限公司

采用FPGA 器件EP1C12實現了對A/D轉換芯片AD7822的實時采樣控制,并將采集的數據暫存到SRAM中以備后續處理。整個設計在QuartusⅡ環境下,采用Verilog HDL語言描述,給出了硬件電路連接、硬件內部邏輯設計以及測試波形,可用于模擬信號的高速實時采集。

FPGA;Verilog HDL;A/D 轉換;采樣控制

FPGA;Verilog HDL;A/D convertion;Sampling control

引 言

隨著現代電子技術的應用和發展,越來越多的電子應用由模擬系統向數字系統轉變,而A/D轉換器作為模擬系統和數字系統的界面,承擔著將模擬信號轉變為數字信號的任務,在一些多路信號采集系統和實時數字信號處理系統中,A/D轉換的多路擴展、高精度、低成本、實時性顯得越來越重要。在一般的信號采集系統中,往往由單片機對A/D轉換器進行控制,增加了CPU的負擔,降低了CPU的工作效率,大大影響信號采集的實時性。

FPGA的高集成度和高速的特性,使之相對于單片機,更適合于對A/D轉換的高速控制,而且還可以把采樣數據實時存儲。基于此,設計了一種基于FPGA的A/D轉換控制器,利用 FPGA 直接控制AD7822芯片對模擬信號進行采樣,采集速度可達1MB/s,然后將轉換好的8位二進制數據迅速存儲到SRAM中,從而提高了采樣的實時性、減輕了主CPU的運行負擔。

1 AD7822介紹

AD7822是Analog Devices公司推出的一種8-bit A/D轉換器。單極性輸入,采樣分辨率8Bit,并行輸出;內含取樣保持電路,以及可選擇使用內部或外部參考電壓源,具有轉換后自動Power-Down的模式,電流消耗可降低至5μA以下。轉換時間最大為420ns,SNR可達48dB,INL及DNL都在±0.75 LSB以墻。可應用在數據采樣、DSP系統及移動通信等場合。

1.1 AD7822的引腳功能VIN1:模擬信號輸入端;Vref:參考電壓輸入輸出端,可使用片上參考電壓,也可外接參考電壓;

CS:片選端,低電平有效;

DB0-DB7:并行數據輸出端,一般處于高阻態,當RD和CS變低有效時,數據才被放到數據總線上;

CONVST:邏輯輸入信號,在該信號的下降沿(至少保持20ns低電平)啟動8-bit模數轉換,進入hold模式,轉換開始后120ns再次進入track模式。轉換結束時檢測CONVST信號的狀態,若為低,則芯片將power down。

EOC:邏輯輸出。該信號表明轉換什么時候完成,可在轉換完成時用于微控制器的中斷信號或將數據鎖存到門陣列。

PD:邏輯輸入,將該信號拉低可使AD7822處于Power-Down模式,當PD變成高電平時ADC上電。

RD:邏輯輸入信號,該信號用于使輸出緩沖器退出高阻狀態,并驅動數據到數據總線上。只有RD和CS都為邏輯低時數據總線方可使用。

VDD:電源輸入端,3V+10%或5V+10%;AGND:模擬地;

DGND:數字地。

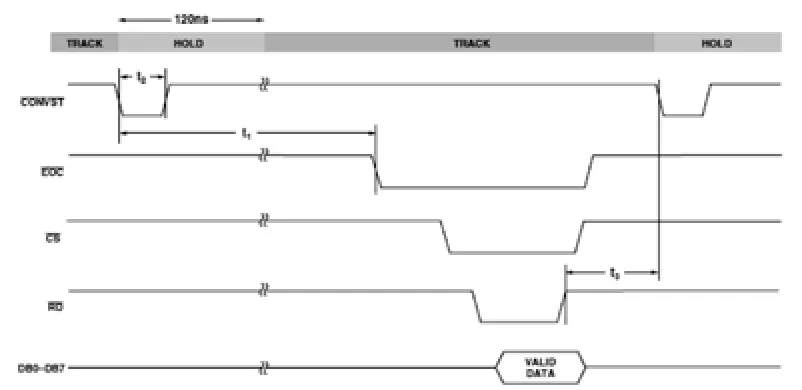

1.2 AD7822的操作模式及轉換時序

AD7822有兩種可能的操作模式:高速采樣模式和自動Power-Down模式。在高速采樣模式下,兩次轉換之間AD7822不會power-down,因此可以達到較高的吞吐率;而在自動Power-Down模式下,轉換結束后AD7822會自動power down,這對于功耗敏感的應用比較有利。設計中采用高速采樣模式,基本時序如圖1所示。

圖1 高速采樣模式的時序

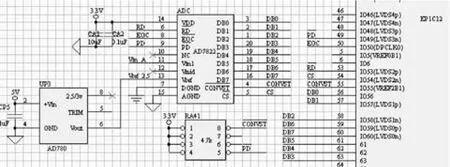

1.3 AD7822與FPGA的硬件電路圖

圖2 AD7822與FPGA的電路連接圖

如圖2所示,在本系統中,AD7822的VDD采用3V電源供電,這樣數據總線可以直接與FPGA(FPGA引腳的邏輯電平為3V)連接,無需電平轉換。參考電壓源Vref為+2.5V,由AD780產生。偏置電壓輸入引腳Vmid懸空,即Vmid 缺省為1V。這種情況下,AD7822可以處理的模擬信號范圍為0~2V,即模擬輸入信號經運放處理,轉換到0~2V范圍內之后,再輸入AD7822的VIN1引腳。本文利用Tektronix公司的AWG5012B任意波形發生器產生0~2V的波形信號作為信號源。為避免AD7822因外界干擾進入非法狀態或Power down,將AD7822的控制引腳CONVST和PD上拉。

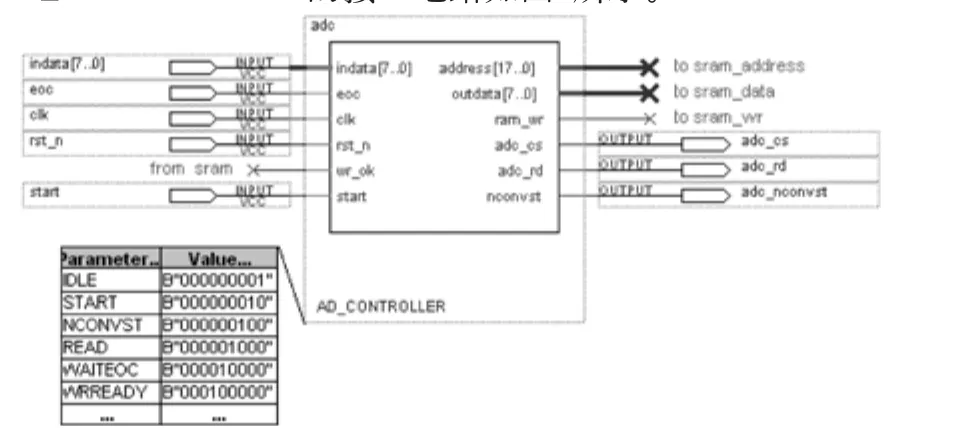

2 AD7822控制器的設計

本設計采用FPGA芯片EP1C12來對AD7822進行采樣控制,并將轉換得到的數據存儲到SRAM中去。用FPGA設計的采樣控制器AD_CONTROLLER的接口電路如圖3所示。

圖3 采樣控制器AD_CONTROLLER接口電路圖

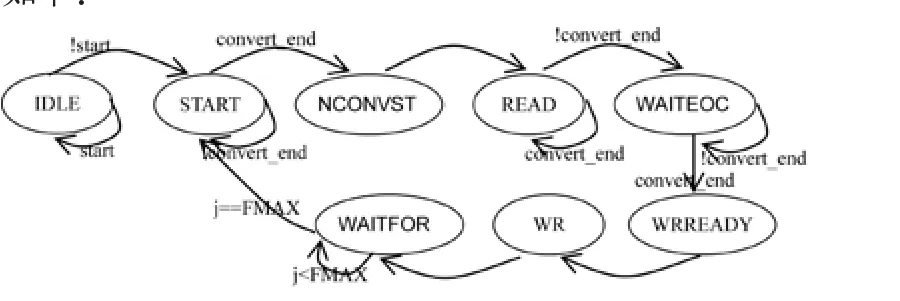

AD_CONTROLLER的輸入時鐘clk取50 MHz,在該時鐘的作用下,利用有限狀態機,控制nconvst、adc_cs、adc_rd信號的狀態,從而完成A/D轉換及轉換結果的存儲。start為AD_ CONTROLLER的啟動信號,外接按鍵,當按鍵PB0按下(start為0)時,AD_CONTROLLER開始工作。indata[7.0]為AD7822的轉換結果,當轉換完成時,eoc由高電平變為低電平并持續70~110ns,因此,狀態機的控制時鐘必須小于70ns,否則可能檢測不到eoc信號,這里取20ns。要連續采集數據就要不斷地用時鐘信號觸發AD7822的CONVST腳,而FPGA根據AD7822送來的EOC信號不斷地讀取并將結果送往SRAM存儲。A/D轉換過程的狀態遷移圖如下:

圖4 狀態遷移圖

IDLE狀態:空閑狀態,如果收到來自外部啟動A/D轉換的信號,則進入START狀態。

START狀態:控制A/D開始轉換,將nconvst置低電平,nconvst為低電平至少保持20ns,才能啟動A/D轉換。

NCONVST狀態:A/D轉換保持階段,nconvst為低電平1個時鐘(20ns)之后恢復高電平。

READ狀態: convert_end變為低電平(表示A/D轉換完成)后,將adc_cs和adc_rd控制信號拉低,讀取A/D轉換結果。

WAITEOC狀態:等待convert_end變高,才將adc_cs和adc_rd拉高,以滿足adc_rd為低電平最少保持30ns的時序要求。

WRREADY狀態:建立地址和數據信號,準備寫SRAM。

WR狀態:產生片選和寫脈沖。

WAITFOR狀態:用于延時。在該狀態,用變量j記錄時鐘數,與參數FMAX共同控制采樣頻率,保證1us采樣一次(參數FMAX取18,即延時18個時鐘,該值從調試過程中得到)。

注意:判斷A/D轉換是否完成取決于信號eoc的狀態,但是在圖4中,都是通過信號convert_end來判斷的。這是由于直接用clk的上升沿對eoc判斷決定某些操作是否運行時,會因為clk和eoc兩個信號的跳變沿相隔太近而令狀態機不能正常工作,因此利用clk的下降沿建立convert_end信號與eoc同步,相位相差180°,然后用clk的上升沿和convert_end信號來判斷操作是否進行。

3 仿真

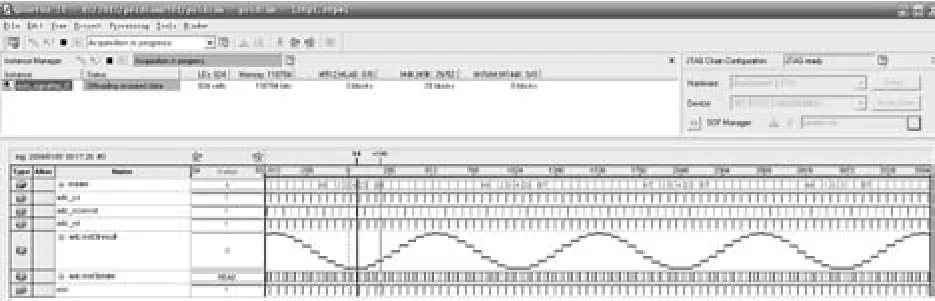

本文利用Tektronix公司的AWG5012B任意波形發生器產生0~2V的波形信號作為信號源,通過BNC接口輸出直接與AD7822的模擬信號輸入引腳連接,通過Quartus II軟件集成的Signal Tap II 嵌入式邏輯分析儀軟件對該A/D轉換控制模塊進行仿真,波形如圖5所示,輸入信號為50KHz的正弦波。

圖5 50KHz的正弦波波形采集仿真

通過波形可觀察到,該模塊的設計達到了預期目的,可以實現對模擬信號的1us實時采樣和模數轉換。

4 結語

采用FPGA作為控制器,針對AD7822完成了模擬信號的實時采集與轉換處理,充分利用了FPGA高速高效的優勢。經仿真,驗證該設計運行正常,可以滿足信號1us實時采集的需求,并且可以很方便地擴展為更多路的數據采集,能根據不同的應用進行擴展,大大增強了系統應用的靈活性。

[1]夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008

[2]戶國強,房建東,郭春蘭.基于FPGA的A/D轉換采樣控制模塊的設計[J].微計算機信息,2008(7):229~230

[3]黃容蘭,萬德煥.基于FPGA 的A/D 轉換采集控制模塊設計[J].數據采集與處理,2009(10):237~240

[4]韋存剛,金星.基于FPGA的多路數據采集和控制模塊設計[J].微計算機信息,2008(6):231~232.

[5]AD7822 datasheet [EB/OL]. Analog Devices, Inc, 2001

[6]Cyclone Device Handbook [EB/OL]. Altera Corporation, 2008

[7]AD780 datasheet [EB/OL]. Analog Devices, Inc, 2004

A Design of the A/D Convertion Control Module Based on FPGA

Xin Fengyan1Sun Xiaoye21.Applied Mathematics Institute, HeBei Academy of Science, Shijiazhuang 050081; 2.Shijiazhuang Development Zone Jikeshuangshi Science & Technology Co, Ltd

FPGA device EP1C12 controls AD7822 to collect analog signal and convert into digital signal, then saves the data to SRAM. The whole design is under the Quartus Ⅱ platform, described in the Verilog HDL. The hardware circuit, internal logic design and waveforms are given. It can be used for high-speed real-time acquisition of analog signal.

TP30

A

10.3969/j.issn.1001-8972.2012.05.040