基于有限狀態機的QPSK調制系統發送模塊FPGA實現

賀 剛,柏 鵬,彭衛東,王明芳,韓立峰,趙學軍,高升強

(1.空軍工程大學 科研部 信息中心,西安 710051;2.空軍工程大學 導彈學院,陜西 三原 713800;3.西安陸軍學院,西安 710108)

1 引 言

當前,以硬件描述語言為工具、邏輯器件為載體的系統設計越來越廣泛。在設計中,狀態機是最典型、應用最廣泛的電路模塊,其在運行速度的高效、執行時間的確定性和高可靠性方面都顯現出強大的優勢[1]。

狀態機的設計思想已經在各個領域均有廣泛的應用,文獻[2]在離子注入機設計中采用狀態機設計方法。文獻[2,3]提出了引入狀態機設計主要有3個方面的原因:實現快速建模、提高代碼復用率和管理大量并發控制流程。有限狀態機(Finite State Machine,FSM)是根據當前狀態以及觸發條件進行狀態轉換的一種機制,包含一組狀態集(state)、一個起始狀態(start state)、一組輸入符號集(alphabet)、一個映射輸入符號和當前狀態到下一狀態的輸換函數(transition function)的計算模型[2,3]。

本文對QPSK調制發送系統的幀格式的特征進行了分析,結合有限狀態機的模型特征,調制系統的各部分組成數據(同步頭數據、標志位數據、相位校正數據、正文數據)對應于有限狀態機模型中的狀態集,根據觸發條件,相應地將所需數據塊依次發送。由于有限狀態機是一種具有離散輸入輸出系統的模型,由有限的狀態和相互之間的轉移條件構成,在任何時候都只能處于給定數目狀態中的一個,因此采用這種設計方法能穩定可靠地按需求將各數據塊進行發送。

2 QPSK調制發送系統的幀結構分析

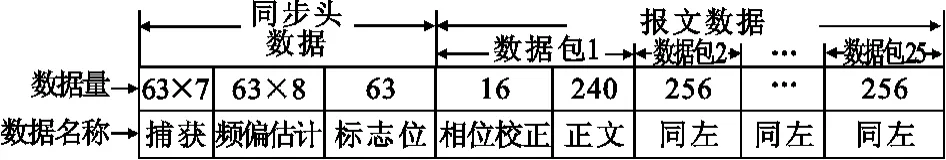

所設計的QPSK調制系統[4-6]中,發送的數據幀格式如圖1所示。

圖1 幀格式Fig.1 Frame format

由圖1可知,本通信系統一幀數據由同步頭數據和正文數據組成,其中同步頭數據為16個63位的m偽碼序列,由捕獲、頻偏估計和標志位三部分組成,其中捕獲占7個63位的m序列,頻偏估計占8個63位的m序列,標志位占1個63位的m序列;正文數據由25個數據包組成,每個數據包由256 bit組成,其中16 bit用于相位校正,240 bit為數據正文。

在QPSK調制器設計中,在發信機端需按順序將同步頭數據、標志位數據、相位校正數據、正文數據依次發送,在接收端才能根據數據格式將數據正確進行接收解調。因此,根據有限狀態機能有效管理各個事件順序執行的功能,在本設計的發送模塊中采用有限狀態機的設計方法,通過有限狀態機描述的邏輯可以有效地分配各數據模塊的發送順序,以符合通信系統要求的數據幀格式。

3 組幀結構有限狀態機設計模型

沒有采用FSM設計的傳統的發送系統因為沒有對系統要進入的下一狀態進入嚴格的約束,系統發送數據的各狀態間不能達到無縫鏈接,可能會導致狀態的紊亂。而采用FSM設計方法,系統在任何時候都只能處于給定數目狀態中的一個,因此能保證系統能穩定可靠地工作。以下對狀態機的具體設計進行分析。

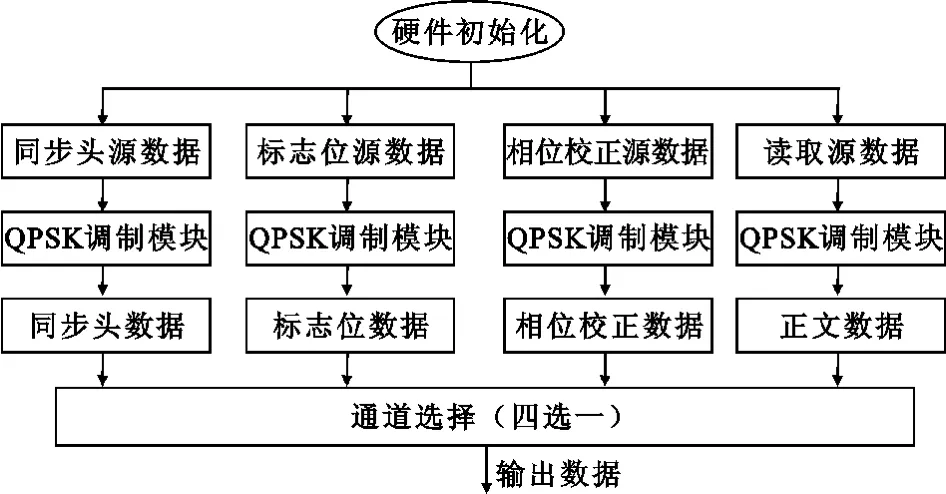

根據系統硬件設計需求,系統時鐘采用12MHz。發送模塊組成結構如圖2所示。

圖2 系統結構圖Fig.2 Structure of system

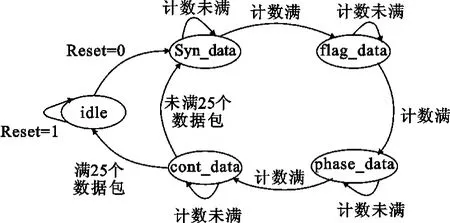

根據圖2中系統的組成結構,采用了FSM的設計方法。FSM可以用有向圖來表示,用節點表示某個特定的狀態,用一條有向線表示狀態的轉移,線上的字母代表的是狀態的轉移條件,本系統設計中發送的狀態轉移圖如圖3所示。

圖3 系統狀態轉移圖Fig.3 State shift of system

圖中,狀態1“idle”為系統起始狀態,表示系統空閑,其工作流程描述如下:

(1)當系統復位開關“reset=1”時,系統復位,各值置零,系統進入空閑狀態;

(2)當“reset=0”時,系統由空閑狀態轉入發送數據狀態,首先進入同步頭數據模塊,開始發送同步頭數據,當計數滿則進入標志位數據模塊,否則繼續發送同步頭數據;

(3)進入標志位數據發送模塊后,若計數滿則進入相位校正數據模塊,否則繼續發送標志位數據;

(4)進入相位校正數據發送模塊以后,若計數滿則進入正文數據發送模塊,否則繼續發送相位校正數據;

(5)進入正文數據發送以后,若計數滿則進入第二輪數據發送,即轉到標志位數據發送模塊,否則繼續發送正文數據;

(6)按上述順序,依次發送數據滿25輪即發送完25個數據包之后,系統重新開始進入空閑狀態。

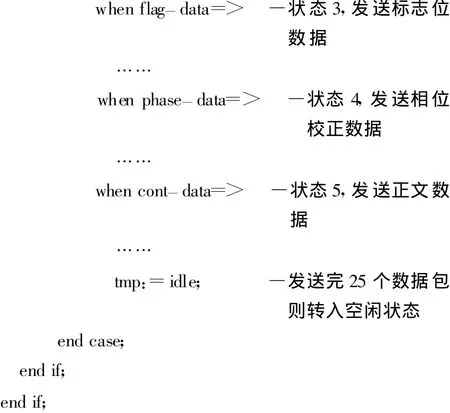

根據系統發送框圖設計的主控程序狀態機實現的VHDL核心代碼[7,8]如下:

4 FPGA實現效能分析

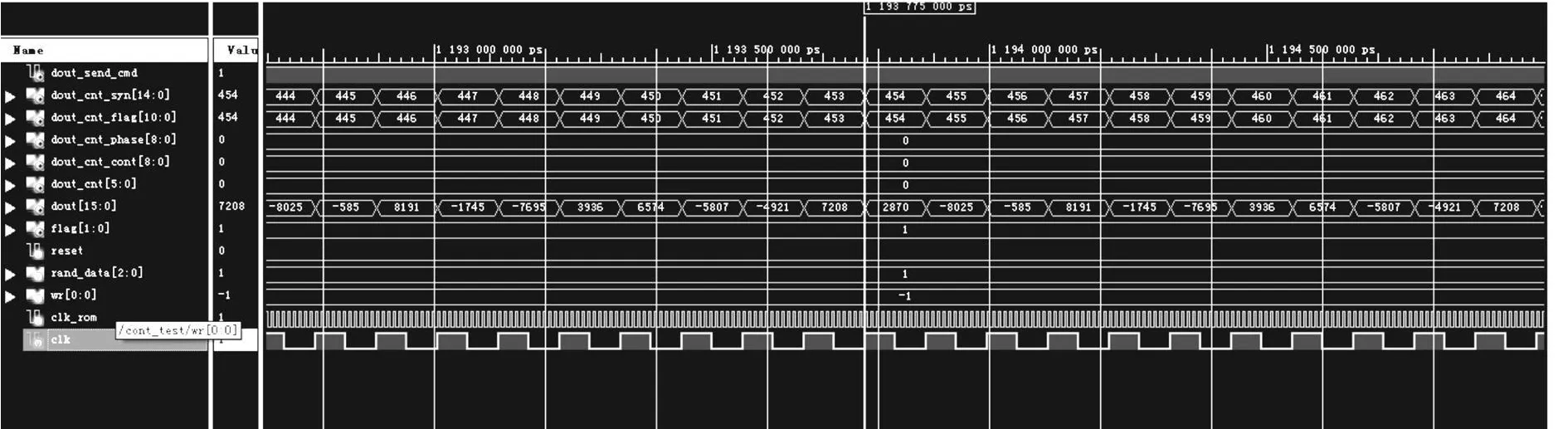

系統實現在FPGA內完成,選用的開發工具為Xilinx公司的 ISE11平臺,器件為 virtex5系列xc5vsx95t-2ff1136,實現的結果如圖4所示,其中,clk為系統時鐘,reset為系統復位信號,dout-cntsyn、dout-cnt-flag、dout-cnt-phase 和 dout-cnt-cont分別表示同步頭數據、標志位數據、相位較正數據和正文數據,dout為將各部分數據按順序發送的結果。

圖4 FPGA實現結果圖Fig.4 Implementation result with FPGA

以FSM作為系統主控程序的編程模型[9,10],實現了軟件單元的功能定義和控制邏輯分離,提高了系統重構的柔性,描述了具有邏輯順序的事件,有效地管理同步頭數據、標志位數據、相位校正數據、正文數據執行的步驟。

5 結 語

本文論述了有限狀態機設計思想的基本原理,分析了QPSK調制系統中發送數據的幀格式,研究了如何使發送系統各組成模塊的數據有序進行發送,達到模塊間的無縫鏈接,提出了采用有限狀態機的設計方法,最后在Xininx公司的FGPA芯片上實現了發送模塊中同步頭數據、標志位數據、相位校正數據、正文數據的有序發送。這樣的設計使系統發送模塊工作穩定可靠,完全滿足通信中數據發送的的需求。該設計思想非常適用于管理大量并發控制流程的系統設計。

[1]王巍,高德遠.有限狀態機設計策略[J].計算機工程與應用,1999(7):54-55.WANG Wei,GAO De-yuan.DesignStrategy for Finite State Machine[J].Computer Engineering and Applications,1999(7):54-55.(in Chinese)

[2]羅宏洋.狀態機在離子注入機中的應用[J].電子工業專用設備,2009,38(9):49-53.LUO Hong-yang.Application of FSM in Ion Implanter[J].Equipment for Electronic Products Marufacturing,2009,38(9):49-53.(in Chinese)

[3]馬潔海,高光來.可復用的狀態模式設計[J].內蒙古大學學報(自然科學版),2004,35(5):576-582.MA Jie-hai,GAO Guang-lai..A Reusable Design of State Patten[J].Acta Scientiarum Naturalium Universitatis Neimongol(Natural Science Edition),2004,35(5):576-582.(in Chinese)

[4]Erich Gamma.設計模式[M].李英軍,馬曉星,蔡敏,等,譯.北京:機械工業出版社,2000:78-80.Erich Gamma.Design Mode[M].Translated by LI Yingjun,MA Xiao-xing,CAI Min,et al.Beijing:Press of Engine Industry,2000:78-80.(in Chinese)

[5]Beek J D,Ove Edfors,MagnusSandell.On channel Estimation inOFDM Systems[C]//Proceedings of 1995IEEE 45th Vehicular Technology Conference.Chicago:IEEE,1995:815-819.

[6]Li Y.Pilot-symbol-aided channel estimation for OFD M in wireless systems[C]//Proceedings of 1995 IEEE 49th Vehicular Technology Conference.Houston,TX,USA:IEEE:1131-1135.

[7]高雪平,官伯然,汪海勇.QPSK調制解調的系統仿真實驗[J].杭州電子科技大學學報,2006,26(5):52-55.GAO Xue-ping,GUAN Bo-ran,WANG Hai-yong.The Experiment of QPSK Modulation and Demodulation Simulation[J].Journal of Hangzhou Dianzi University,2006,26(5):52-55.(in Chinese)

[8]羅力凡,常春藤.基于VHDL的FPGA開發快速入門.技巧.實例[M].北京:人民郵電出版社,2009:105-109.LUO Li-fan,CHANG Chun-teng.Rudimental,Skill and Example of FPGA Design Based VHDL[M].Beijing:People′s Posts and Telecommunications Press,2009:105-109.(in Chinese)

[9]SYNARIO.VHDL Reference Manual[M].Redmond:Microsoft Corporation,1997:2-9.

[10]劉凌,胡永生.數字信號處理的FPGA實現[M].北京:清華大學出版社,2003:272-278.LIU Ling,HU Yong-sheng.Implement of Digital Signals Process with FPGA[M].Beijing:Tsinghua University Press,2003:272-278.(in Chinese)