基于軟件無線電的嵌入式系統總線研究及應用

李燕斌,覃 超,黃揚洲,劉偉敏

(中國西南電子技術研究所,成都610036)

1 引 言

軟件無線電是一種新型的無線電體系結構,它通過硬件和軟件的結合使無線網絡和用戶終端具有可重配置能力。軟件無線電提供了一種建立多模式、多頻段、多功能無線設備的有效而且相當經濟的解決方案,可以通過軟件升級實現功能提高[1]。軟件無線電的基本思想是以開放性、可擴展、結構精簡的硬件為通用平臺,把盡可能多的無線電功能用可重構、可升級的構件化軟件來實現。為了便于硬件模塊的升級和擴展,軟件無線電系統需采用標準的、高性能的開放式總線結構,內部各功能模塊間通過標準嵌入式總線相連。

作為系統內部各模塊間數據傳輸和交換的通道,總線是系統的血管和經絡,對整個無線電系統而言,其重要性不言而喻。過去的軟件無線電系統一般采用VME、PCI等并行總線結構,隨著高速總線技術的發展,現在軟件無線電系統主要基于高速串行總線結構來設計,未來全光數據交換結構將是發展方向。

2 傳統的并行總線傳輸方式

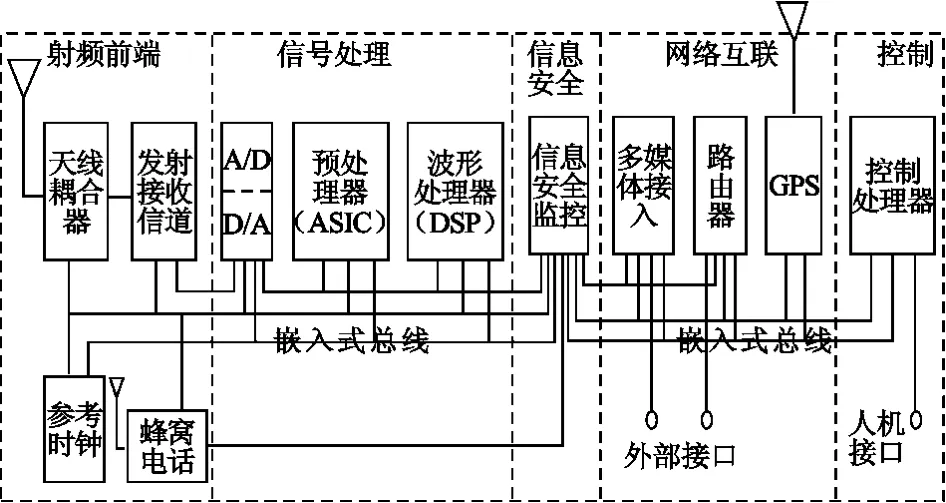

圖1所示為典型的軟件無線電系統結構。軟件無線電系統傳統的總線方式大都采用并行架構,VME和CPCI是2種最常用的嵌入式總線方式,其結構形式參見圖2。

圖1 典型的軟件無線電系統結構Fig.1 Typical system frame of SDR

圖2 傳統的軟件無線電嵌入式系統結構Fig.2 Traditional embedded system frame of SDR

CPCI總線實現的是一種Big Pipe的數據傳輸模式,其采用一組并行線掛接多個功能模塊,最高負載模塊數量不超過8個(CPCI),可支持較小的電子系統;傳輸位寬支持 32/64,最高傳輸速率為528 Mbyte/s,其帶寬較寬、速率高,適合作為高速處理和計算平臺的接口標準,機械結構和尺寸能勝任惡劣環境下應用。

VME總線相對于CPCI總線來說負載能力更強,其最高負載模塊數量達21個,可支持較大的電子系統;但其帶寬較窄、速率較低,不適合作為高速處理和計算平臺的接口標準,需要增加專用數據傳輸通道實現實時高速數據傳輸;機械結構和尺寸能勝任惡劣環境下應用。

隨著軟件無線電通信系統對帶寬需求的增長,VME和CPCI等多負載并行總線技術已很難適應新一代系統的需求。為滿足高速率并行傳輸,其重點已集中在源同步標準并行總線上。典型的源同步并行總線標準有CSIX、SPI-4.2(Double)等,由于其總線時鐘頻率系統同步并行,傳輸能力有很大提高,但其要求數據和源同步時鐘信號是同步傳輸的。隨著頻率的提高,控制時鐘和數據信號之間的物理/電氣特性偏移也越來越困難,信號質量會受到總線長度限制、信號失真、電路板布線處理通道畸變、抖動等多方面的影響,并行總線結構的局限性日漸顯現。通信技術在不斷地發展,總線技術相應也在不斷地更新,而串行總線結構在高數據交換速率、多模塊和具有高速內部交換網絡的高端系統上其優勢性日益顯現。

3 串行總線架構的優勢

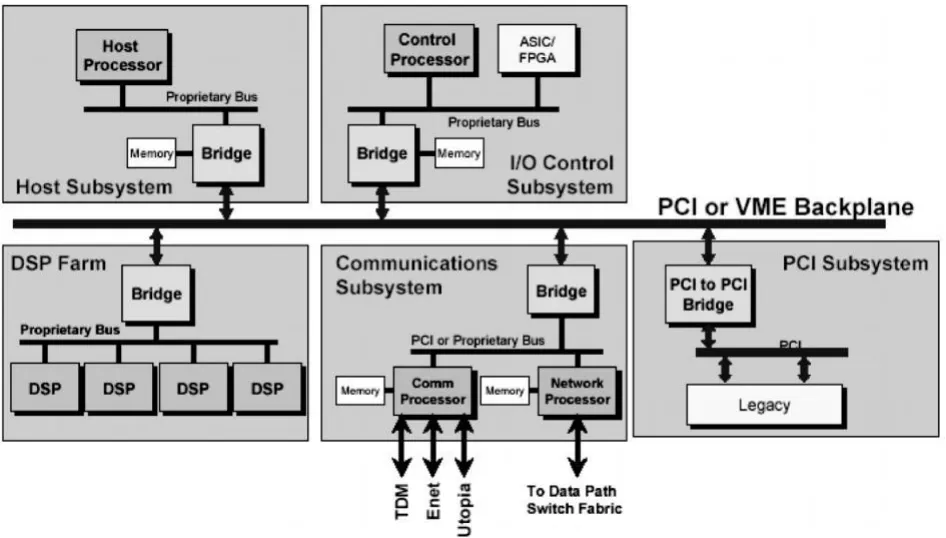

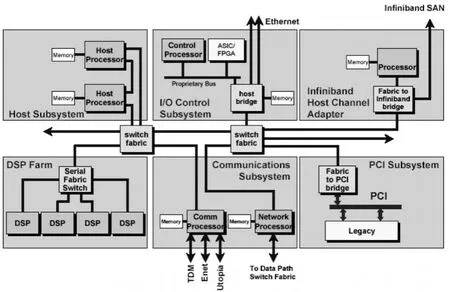

隨著通信技術和總線技術的發展,新型軟件無線電系統嵌入式總線架構以串行替代并行,以Pointto-Point方式替代Big Pipe方式,以包交換替代電路交換,以Switch Fabric替代共享總線已成為必然。新型的軟件無線電系統嵌入式結構如圖3所示。

圖3 基于串行總線的嵌入式體系架構Fig.3 Embedded system frame based on serial bus

串行總線主要有以下幾大優點:

(1)串行傳輸可以最大限度地減少芯片管腳數,減小背板的尺寸和系統設計造價,提供更多的傳輸鏈路,現有的技術已經能夠實現千兆級的傳輸率;

(2)點到點通信方式最大程度地減小了通信鏈路的負載,有利于進一步提高時鐘頻率/數據率,同時系統負載模塊數量可以大大增加,可滿足各種電子系統需求;

(3)由于避免了VME和CPCI等并行總線架構的總線仲裁問題,因此基于串行總線的嵌入式系統模塊間可以實現很高的傳輸效率;

(4)Switch Fabric是利用新一代開關器件結合分組交換技術實現的一種交叉開關網絡,系統中多個點到點的通信鏈路被組織在一起,最終能夠實現所有芯片/模塊間的任意互連和并發傳輸。

目前可以支持千兆級的常用串行傳輸總線包括RapidIO 、PCI Express等。

4 多種高速總線性能比較

可用于軟件無線電系統的嵌入式高速串行總線種類很多,目前最為通用的是RapidIO、PCI Express、StarFabric、千兆以太網等,它們都可以提供高速、可靠的點對點互聯。

千兆以太網技術是百兆以太網技術的升級,支持10/100/1 000Mbit/s全雙工數據傳輸,最初用于局域網內和廣域網內的互聯,是非常可靠的互聯選擇。但千兆以太網技術較RapidIO、PCI Express等技術效率稍低,而且系統延時較大,不適合實時嵌入式系統內部的互聯,是系統外部總線接口的良好選擇。

RapidIO總線基本規范于2001年完成,2003年該互聯規范被國際標準總線和國際電工委員會(IEC)一致通過,這使RapidIO(ISO)成為互連技術方面得到授權的唯一一個系統[2]。串行RapidIO技術是專門為嵌入式系統互聯而設計的,只要有足夠多的交換機,就可以實現任意結構的拓撲。其傳輸帶寬高,最高可達64 Gbit/s。

PCI Express技術是著眼于最大的兼容PCI總線技術而設計,為了能夠兼容傳統的PCI總線技術,PCI Express的拓撲結構只能是樹形結構。這種結構在PC機和服務器內非常適用,如果合適的話,也能用在嵌入式系統內。但在PCI Express的結構中除了要有交換機,還需要有一個模塊來做統一的管理,這增加了硬件的開銷。

StarFabric是一種高速、點對點的串行交換總線技術,主要面向實時應用的嵌入式領域的系統級互聯,每一鏈路支持的帶寬支撐的帶寬達2.5 Gbit/s[3],這些鏈路可以熱插拔。該技術由Star-Gen公司發起推廣,目前比起PCI-E和RapidIO總線來說傳輸速率和效率稍低,應用也沒有那么廣泛。

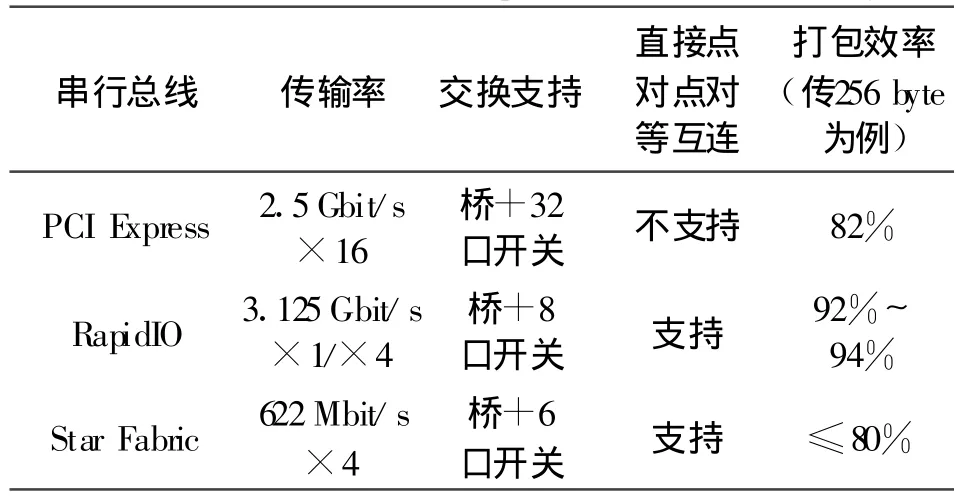

表1給出了幾種常用嵌入式串行總線的性能。通過以上幾種高速串行總線技術比較可以看出,串行RapidIO技術各方面性能都較好,同時 FPGA、DSP、CPU和很多專用芯片都支持這種標準,是目前軟件無線電嵌入式系統內實現互聯的最佳選擇,其他各類串行或并行總線可以做為子系統或模塊內部的數據交換總線。

表1 幾種常用的嵌入式串行總線性能Table 1Several common serial bus performance in embedded system

5 在工程中的應用

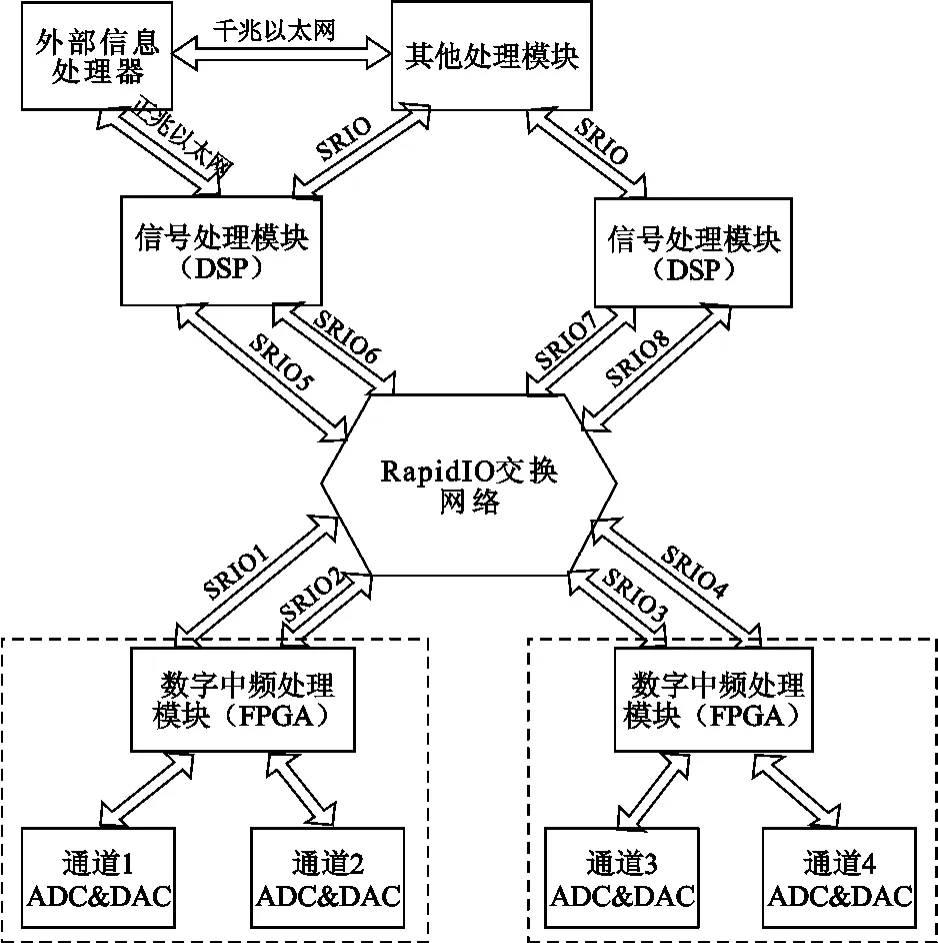

在基于軟件無線電設計思路的某項目中,其架構為4路收發通道,為了支持系統動態可重構能力,在各路中頻信號數字化后通過RapidIO總線和交換網絡建立了一個基本的點對點網絡(如圖4)。信號處理模塊可以根據需要從網絡中選取不同信道的采樣信號,或向不同的信道發送調制信號,信號處理模塊本身根據不同的通道和工作模式實現軟件動態加載。信號處理模塊和其他模塊間通過RapidIO總線實現數據信息交互。

圖4 四路點對點網絡結構Fig.4 4-gateway point-to-point network frame

數字中頻處理模塊將來自接收通道的中頻信號ADC采樣后送給FPGA,FPGA經數字下變頻等信號預處理后,通過RapidIO高速串行總線送往開關交換網絡,再經交換判決送到對應的信號處理模塊。另一方面,數字中頻處理模塊FPGA接收來自信號處理模塊經開關網絡送來的高速串行數據,通過解串處理后送DAC進行數模轉換,最后輸出發中頻信號送往信道發送端。

數字中頻處理模塊選用Xilinx V5系列FPGA。用FPGA開發RapidIO具有以下優點:

(1)FPGA集成了RapidIO收發器[4],可以支持多達8路串行RapidIO同時傳輸;

(2)支持RapidIO 2.0標準,提供高達12.5 GHz的帶寬,支持標準的1x/4x模式;

(3)實現了RapidIO的三層協議:邏輯層、傳輸層和物理層;

(4)支持命令、流數據和突發數據的傳輸;

(5)為應用層提供統一的接口,使軟件開發人員可以專注于應用開發。

為了對內數據交換和對外協議處理的方便,本平臺的信號處理模塊選用TI的DSP芯片TMS320C6455[5]來實現RapidIO總線和千兆以太網接口。TMS320C6455內嵌了SRIO模塊,擁有4個全雙工的port(端口),支持SRIO 1x/4x串行協議。每個 port支持1.25 Gbit/s、2.5 Gbit/s、3.125 Gbit/s的波特率,每個port可以單獨構成1x模式,也可以4個port共同構成4x模式[6]。

本系統平臺4個信號收發處理通道,具有8個RapidIO節點,通過專用交換芯片構成交換網絡,可實現任意信號處理通道和任意信道收發通道之間高速數據交換,交換芯片數據包延遲小于2 μ s。

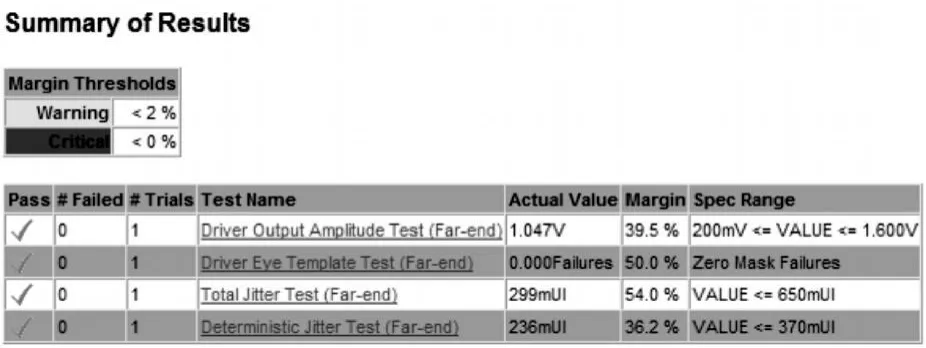

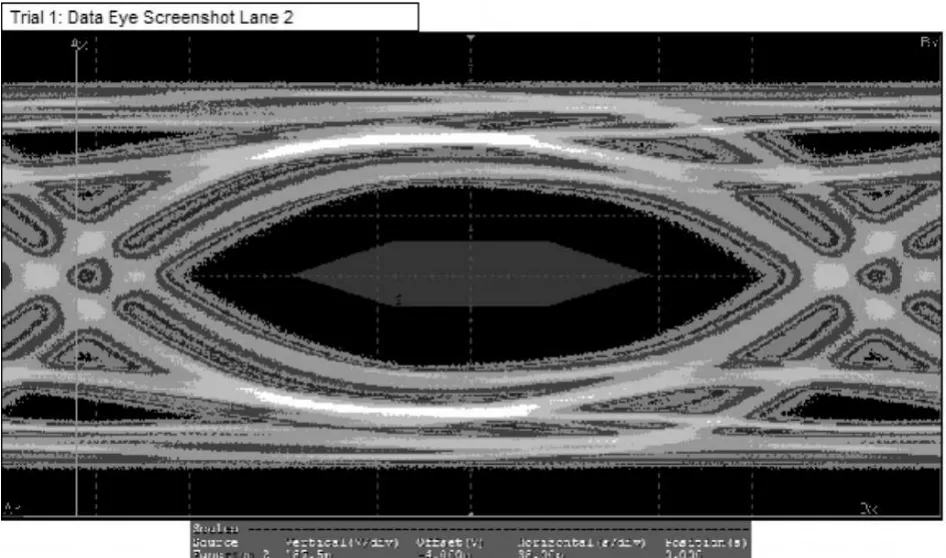

圖5是用高速信號分析儀對串行RapidIO鏈路層電壓驅動幅值、抖動總量測試、確定性抖動測試的分析結果,圖6是眼圖分析結果。通過分析結果可以看出各項指標都還有較大的裕量,從眼圖來看,眼睛張開幅度較大,眼圖較穩定,交叉點在幅值的中間,由綜合測試結果可知RapidIO鏈路工作穩定,性能良好。

圖5 SRIO電氣性能測試結果Fig.5 Test result of SDIO electric performance

圖6 SRIO測試眼圖Fig.6 SRIO test eye-fig

6 結束語

基于軟件無線電嵌入式新一代互聯技術已經將系統由“bus and board”推向“fabric and blade”。多負載并行總線技術的確已經沒有太多的發展空間。新一代互連技術、串行傳輸、Switch Fabric已經是大勢所趨,其中的傳輸可靠性(包括模塊和背板高速信號完整性設計等)、低成本測試性[7]和系統高速數據交換穩定性等是嵌入式系統良好運行的關鍵因素。

本文通過多種通用并行和串行總線的比較,論證了RapidIO串行總線是當前軟件無線電嵌入式系統的優選總線。同時在基于RapidIO總線交換網絡實的某應用項目中,實現了數據的高速實時傳輸與交換,具備了硬件平臺良好的開放性和可擴展性以及軟件良好的可重構和可升級性,為RapidIO作為軟件無線電嵌入式總線進行了有效的實踐。當然,要實現一個良好的軟件無線電系統,在嵌入式總線高速組網、高穩定性、高可靠性、可測試性和高效傳輸等很多方面還有很多技術難題,還需要花很大精力去不斷完善。

[1]楊小牛,樓才義,徐建良.軟件無線電技術與應用[M].北京:北京理工大學出版社,2010.YANG Xiao-niu,LOU Cai-yi,XU Jian-liang.SDR Technology and Application[M].Beijing:Beijing Institute of Technology Press,2010.(in Chinese)

[2]徐俊毅.高速總線競爭日趨白熱化[J].電子與電腦,2007(11):37-40.XU Jun-yi.The Competition of High Speed Bus is more and more intense[J].Compotech China,2007(11):37-40.(in Chinese)

[3]黃亞雯,黎想,劉海清,等.基于StarFabric高速總線技術的研究與應用[J].計算機工程,2009(1):221-223.HUANG Ya-wen,LI Xiang,LIU Hai-qing,et al.Research on and Application of High-speed BusTechnology Based on StarFabric[J].Computer Engineering,2009(1):221-223.(in Chinese)

[4]張靜.數字信號處理模塊中的串行RapidIO設計[J].火控雷達技術,2011,40(1):64-75.ZHANG Jing.Design of Serial RapidIO in Digital Signal Processing Module[J].Fire Control Radar Technology,2011,40(1):64-75.(in Chinese)

[5]黃克武,吳海洲.基于TMS320C6455的高速SRIO接口設計[J].電子測量技術,2008,31(9):143-192.HUANG Ke-wu,WU Hai-zhou.Design of high-speed SRIO interface based on TMS320C6455[J].Electronic Measurement Technology,2008,31(9):143-192.(in Chinese)

[6]Texas Instruments Incorporated.TMS320C645x DSP serial RapidIO user′s guide[EB/OL].[2010-05-12].http://www.ti.com.

[7]Mike Kondrat.PCI高速總線測試挑戰[J].半導體技術,2004(4):38-39.MikeKondrat.PCI High-speed Bus Test Challenge[J].Semiconductor Technology,2004(4):38-39.(in Chinese)