基于FPGA的水聲信號(hào)檢測(cè)系統(tǒng)設(shè)計(jì)

劉毅 程錦房 肖大為 何光進(jìn)

(海軍工程大學(xué)兵器工程系,武漢 430033)

1 引言

對(duì)于需要在水下長(zhǎng)時(shí)間工作的聲信號(hào)檢測(cè)系統(tǒng),通常采用電池供電,因而往往要求元器件具有較低功耗,以延長(zhǎng)系統(tǒng)的運(yùn)行時(shí)間。在 FPGA芯片、DSP芯片、單片機(jī)中,F(xiàn)PGA芯片具有低功耗和高運(yùn)算速度的特性,因而更適合用于水下系統(tǒng)。

MUSIC算法是一個(gè)可用于波達(dá)方向(DOA)估計(jì)的經(jīng)典算法,其中包含一些不規(guī)則運(yùn)算步驟,它們?cè)贔PGA中不易實(shí)現(xiàn),鑒于此,本文將在基于FPGA系統(tǒng)中運(yùn)用實(shí)用改進(jìn)化的MUSIC算法判斷水聲信號(hào)源的方位。

2 FPGA簡(jiǎn)介

現(xiàn)場(chǎng)可編程門陣列(Field-Programmable Gate Array, FPGA)是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物,具有更高的集成度、更強(qiáng)的邏輯實(shí)現(xiàn)能力和更好的設(shè)計(jì)靈活性[1]。FPGA是由許多可編程邏輯塊組成的數(shù)字集成電路,這些邏輯塊之間用可配置的互連資源連接,用戶可以通過(guò)編程將這些邏輯塊連接起來(lái)實(shí)現(xiàn)不同的設(shè)計(jì),它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)[2]。

作為一種高密度可編程邏輯器件,F(xiàn)PGA具有低功耗、功能強(qiáng)大、開(kāi)發(fā)周期短、投資小、便于修改及開(kāi)發(fā)工具智能化等特點(diǎn),目前已被廣泛應(yīng)用于通信、航天、醫(yī)療電子、汽車電子、工業(yè)控制等領(lǐng)域[3]。

3 系統(tǒng)設(shè)計(jì)

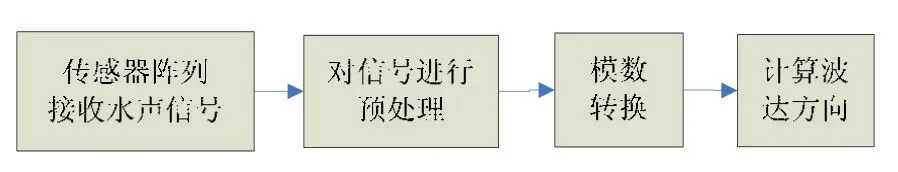

系統(tǒng)的功能框圖如圖 1所示。傳感器陣列的每一個(gè)傳感器對(duì)應(yīng)一路數(shù)據(jù),同步接收聲信號(hào)后,送預(yù)處理板對(duì)信號(hào)進(jìn)行放大、濾波,提高接收信號(hào)的信噪比。模數(shù)轉(zhuǎn)換模塊對(duì)預(yù)處理板輸出的每一路模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),再將輸出結(jié)果送FPGA芯片運(yùn)行DOA算法,計(jì)算得到信號(hào)的聲源方位。

圖1 系統(tǒng)的功能框圖

3.1 傳感器陣列

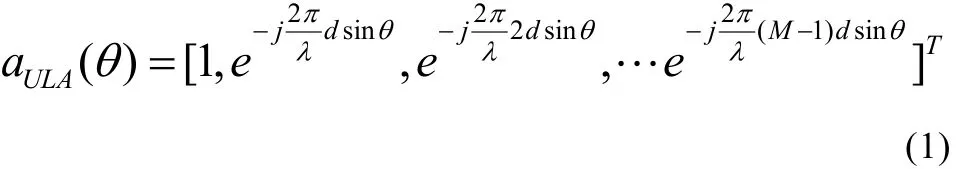

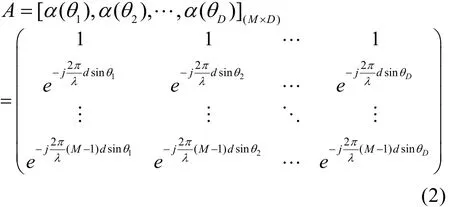

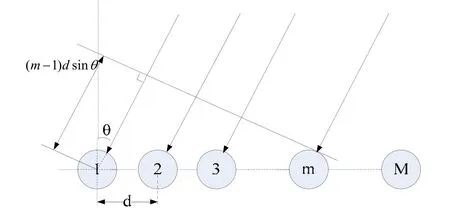

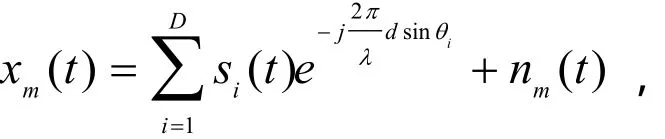

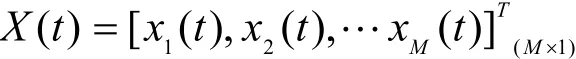

本系統(tǒng)采用M元均勻線列陣,各個(gè)陣元間距為d,以第1個(gè)陣元為坐標(biāo)原點(diǎn),陣列所在直線為x軸建立直角坐標(biāo)系,設(shè)信號(hào)源入射方向與陣列法線的夾角為θ,對(duì)于三維空間,θ是方位角,其幾何模型如圖2所示。λ為入射波波長(zhǎng),第m個(gè)陣元與第 1個(gè)陣元間的波程差為 Δdm=(m-1)dsinθ,則陣列流型為:

設(shè)有D個(gè)非相干窄帶源S1、S2、…SD入射,其方位角分別為1θ、2θ、…Dθ ,則陣列流形為:

圖2 均勻線列陣幾何模型

其中 si(t)為第 i個(gè)信號(hào)源的復(fù)包絡(luò),nm(t)為第 m個(gè)陣元上的零均值白噪聲,由于入射信號(hào)源為非相干窄帶的信號(hào),故X(t)可近似表示為:

式中:表示D個(gè)信號(hào)源,A為陣列流形,N(t)表示噪聲。

3.2 A/D轉(zhuǎn)換模塊

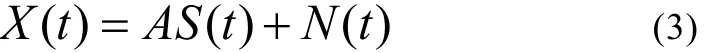

數(shù)據(jù)經(jīng)傳感器陣列采集后,送A/D轉(zhuǎn)換模塊,其中每一路數(shù)據(jù)由一片ADS5102芯片進(jìn)行模數(shù)轉(zhuǎn)換。ADS5102是一種低功耗 CMOS工藝的10位模數(shù)轉(zhuǎn)換芯片,要求差分輸入,轉(zhuǎn)換速率可達(dá)60 Ms/s,它具有靈敏的供電系統(tǒng),提供了斷電模式,在此模式下功耗僅為336μW[4]。本例利用 THS4501差分放大器驅(qū)動(dòng)模擬輸入的電路如圖3所示。

圖3 差分放大器驅(qū)動(dòng)ADS5102模擬輸入電路

模數(shù)轉(zhuǎn)換模塊由M個(gè)上述電路并聯(lián)組成,通過(guò)多路同步采集獲得各個(gè)陣元的實(shí)時(shí)數(shù)據(jù),生成數(shù)字信號(hào)。

3.3 DOA計(jì)算模塊

在所有利用空間譜估計(jì)技術(shù)來(lái)實(shí)現(xiàn)對(duì)波達(dá)方向(DOA)估計(jì)的方法中,MUSIC算法在對(duì)非相干信號(hào)源分辨測(cè)向方面具有高精度和高分辨率特性,被廣泛地應(yīng)用于測(cè)向、通信、雷達(dá)等領(lǐng)域[5]。因此,本系統(tǒng)以MUSIC算法作為實(shí)用化改進(jìn)的基礎(chǔ)方案,構(gòu)建波達(dá)方向(DOA)計(jì)算的處理過(guò)程。

標(biāo)準(zhǔn)的 MUSIC算法包括三個(gè)主要步驟:(a)對(duì)陣列接收到的信號(hào)向量X(t)求其自相關(guān)矩陣R;(b)對(duì)R進(jìn)行特征值分解,構(gòu)造信號(hào)(噪聲)子空間,得到空間譜函數(shù) Pmusic(θ);(c)對(duì)Pmusic(θ)進(jìn)行譜峰搜索[6]。這三個(gè)步驟中,第一步和第三步屬于加乘規(guī)則運(yùn)算,易于用FPGA實(shí)現(xiàn),而第二步是不規(guī)則運(yùn)算,很難用FPGA實(shí)現(xiàn),故還需對(duì)第二步進(jìn)行實(shí)用化改進(jìn)。

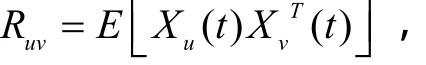

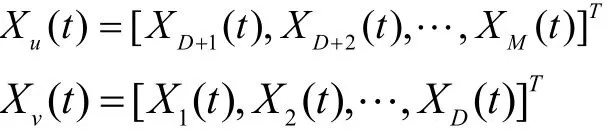

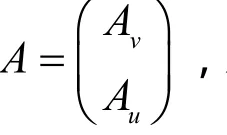

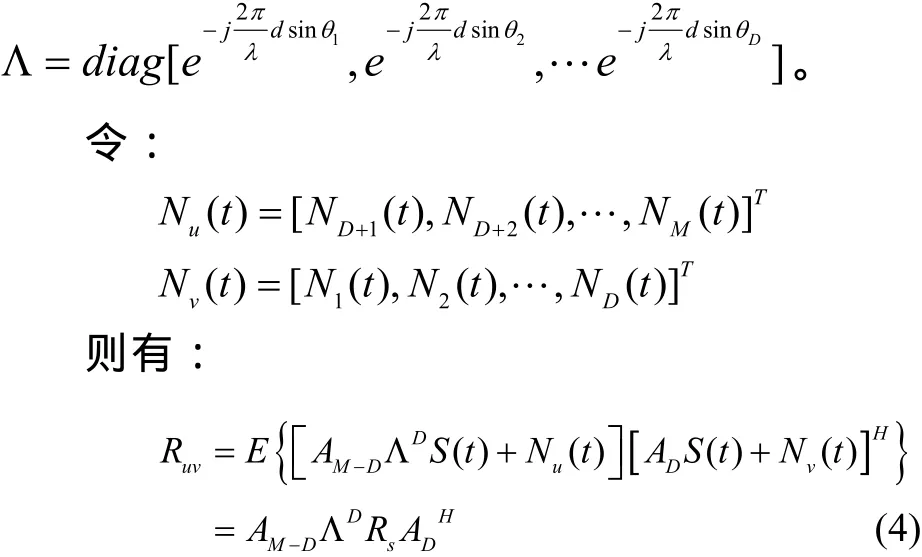

式中:

式(4)表示Ruv的列向量組能由AM-D的列向量組線性表示,當(dāng)D<M-D時(shí),只要D個(gè)信號(hào)分別從不同方向入射,則有的秩為D,而rank()=rank(Rs)=D,故Ruv的列向量組和AM-D的列向量組張成同一子空間,該空間是由M-D維的信號(hào)向量張成的信號(hào)子空間[7]。

故經(jīng)實(shí)用化改進(jìn)后的 MUSIC算法步驟為:(1)計(jì)算采樣自相關(guān)矩陣的(M-D)×D 階子矩陣Ruv;(2)對(duì)Ruv的列向量標(biāo)準(zhǔn)正交化,所得列向量構(gòu)成的矩陣記為U;(3)對(duì)空間譜函數(shù)(θ)進(jìn)行譜峰搜索,對(duì)波達(dá)方向θ作出估計(jì)。

4 系統(tǒng)的軟件設(shè)計(jì)

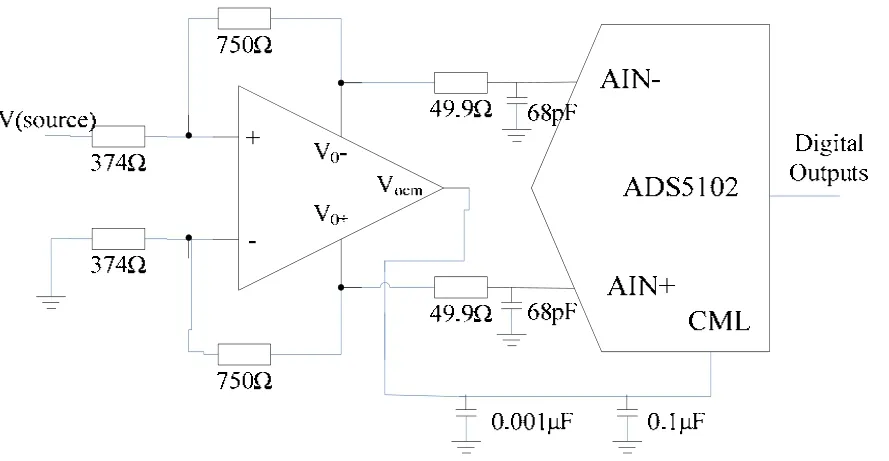

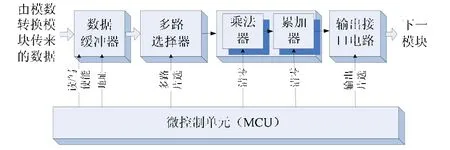

依據(jù)經(jīng)實(shí)用化改進(jìn)后的 MUSIC算法,信號(hào)處理模塊便可細(xì)分為三個(gè)小模塊,分別對(duì)應(yīng)算法的三個(gè)步驟,以第一個(gè)小模塊“計(jì)算采樣自相關(guān)矩陣的(M-D)×D階子矩陣Ruv”為例說(shuō)明程序流程,圖4是其硬件框圖。

在微控制單元的控制下,經(jīng)模數(shù)轉(zhuǎn)換模塊送來(lái)的數(shù)據(jù)首先進(jìn)行數(shù)據(jù)緩沖存儲(chǔ),然后由多路選擇器選擇相應(yīng)的待運(yùn)算數(shù)據(jù)送至數(shù)據(jù)處理單元,各數(shù)據(jù)處理單元計(jì)算得到的結(jié)果匯總至輸出接口電路,然后將結(jié)果數(shù)據(jù)輸出到下一個(gè)程序模塊。需要說(shuō)明的是,圖中乘法器與累加器組成的數(shù)據(jù)處理單元僅是多個(gè)并行處理單元中的一個(gè)代表,其余單元沒(méi)有畫出,其數(shù)量可根據(jù)對(duì)處理時(shí)間的需求來(lái)設(shè)置,理論上來(lái)講數(shù)量越多,程序的并行化程度越高,計(jì)算速度越快。

圖4 采樣自相關(guān)矩陣子矩陣硬件框圖

5 結(jié)束語(yǔ)

本文在空間譜估計(jì)理論的基礎(chǔ)上設(shè)計(jì)了一套基于FPGA的水聲信號(hào)檢測(cè)系統(tǒng),用于DOA估計(jì)數(shù)據(jù)處理,該系統(tǒng)采用了模塊化的設(shè)計(jì)方法,具有可擴(kuò)展性。文章描述了系統(tǒng)模型、框架結(jié)構(gòu)和模塊劃分,特別針對(duì) MUSIC算法進(jìn)行了實(shí)用化改進(jìn),使其能順利應(yīng)用于FPGA芯片中。本系統(tǒng)對(duì)長(zhǎng)期工作于水下的信號(hào)檢測(cè)系統(tǒng)設(shè)計(jì)有一定參考價(jià)值。

[1]U.Meyer-Baese. Digital Signal Processing with Field Programmable Gate Arrays, Third Edition.Springer, 2007.

[2]Clive “Max” Maxfield. The Design Warrior’s Guide to FPGAs Devices, Tools and Flows.Elsevier(Singapore) Pte Ltd, 2007.

[3]王彥. 基于 FPGA 的工程設(shè)計(jì)與應(yīng)用. 西安: 西安電子科技大學(xué)出版社,2007. 1986.

[4]劉延飛, 郭鎖利, 王曉戎等. 基于 Altera FPGA/CPLD的電子系統(tǒng)設(shè)計(jì)及工程實(shí)踐. 北京:人民郵電出版社, 2009.

[5]孟憲元, 錢偉康. FPGA嵌入式系統(tǒng)設(shè)計(jì). 北京:電子工業(yè)出版社, 2007.

[6]周陬. 基于空間譜估計(jì)的無(wú)源測(cè)向技術(shù)研究. 博士論文, 華中科技大學(xué), 2007.

[7]余繼周, 陳定昌.一種 DOA估計(jì)的快速子空間算法[J].北京:現(xiàn)代電子技術(shù), 2005(12): 90-92.