一種基于FPGA的并入并檢AOS幀同步檢測方法

潘成勝,韓 睿,劉春玲

(大連大學遼寧省高校通信與信號處理重點實驗室,遼寧大連 116622)

隨著航天技術的不斷發展,航天器在整個空間鏈路之間傳輸的數據類型越來越復雜,數傳速率越來越高。AOS(高級在軌系統)是CCSDS(空間數據系統咨詢委員會)提出的一種數據通信和傳輸體制,它滿足了高速率、大容量的數據處理和傳輸要求[1]。

幀同步技術是實現大容量數據傳輸的關鍵技術之一,該技術主要采用在接收端重新定位識別發送端發送的特定碼組來解決幀的界限問題,是接收端后續數據處理的前提和基礎,直接影響著通信系統的性能[2]。

傳統的幀同步檢測,數據輸入和處理方式都是串行的[3-4],但某些情況下,幀同步檢測能力受限:一是高速串行碼流的幀同步檢測,采用串檢方法對芯片處理速度提出較高要求;二是在某些數字系統中需對并行碼流進行幀同步檢測,需要進行并串轉換后才能采用串檢方法,方法繁瑣且處理時延提高。文獻[5]解決了同步狀態判斷時間過短的問題,但該方法針對串行碼流且會帶來幀同步碼的相位變化。文獻[6]解決了高速數據吞吐率與芯片處理速度之間的矛盾,但該方法針對串行碼流且使用的芯片資源較多。因此,本文提出一種基于FPGA的并入并檢AOS幀同步檢測方法,并對其性能進行了仿真分析與測試,結果表明該方法實現了高速串行碼流或并行碼流的同步搜索,在處理時鐘頻率、誤鎖概率、平均同步時間和芯片資源使用方面的性能優于串行檢測。

1 AOS幀同步檢測過程

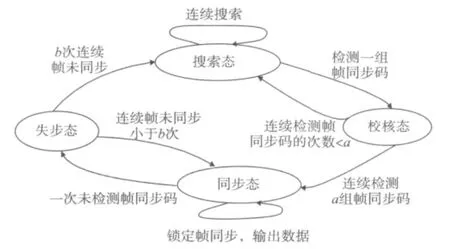

AOS幀同步檢測過程分為以下4種狀態,即搜索態、校核態、同步態和失步態,如圖1所示。數據接收的起始時刻或失步時刻,需進入搜索態。當檢測到一組ASM(幀同步碼)后,隨即進入校核態。在校核態中,為降低虛假同步,若連續檢測到ASM的次數等于后方保護時間a時,則進入同步態,否則重新回到搜索態,重復上述過程。同步態下,若在規定的字節數內仍能連續檢測到ASM,則一直保持同步態。此時,輸出去掉ASM的數據,并給出幀同步指示信號。失步態中,若連續未檢測到ASM的次數等于前方保護時間b時,則進入搜索態,否則當檢測到ASM時,重新回到同步態。

圖1 幀同步檢測過程狀態圖

衡量AOS幀同步系統的性能指標有很多,本文主要從漏檢概率、誤鎖概率、平均同步時間和平均同步保持時間等指標考慮[2]。

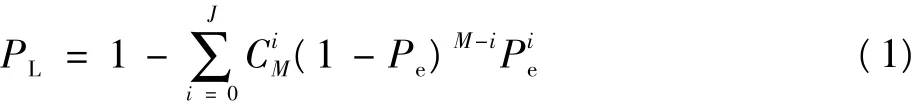

幀同步系統漏檢有誤碼的ASM稱為漏檢概率PL,記為

式中:J為誤碼容限;i為比特數;為M中取i的組合數;M為ASM的長度;Pe為信道誤碼率。

幀同步系統錯誤地識別一幀的開始稱為虛警概率PA,記為

幀同步系統在a幀內錯誤的進入同步態稱為誤鎖概率 Pws,記為

式中:L為幀長;a為后方保護時間。

幀同步系統開始工作到進入同步狀態所經歷的時間稱為平均同步時間Tw,忽略漏檢概率和虛警概率[7],記為

式中:CP為幀同步檢測處理時鐘。

幀同步系統從進入同步態到失步態所經歷的時間稱為平均同步保持時間,記為

式中:b為前方保護時間。

2 并行幀同步碼檢測器的設計

2.1 并入并檢AOS幀同步檢測方法

傳統的幀同步碼檢測是把接收到的串行碼流逐位送入串行移位寄存器,其中,移位寄存器的級數與給定的幀同步碼組的長度相等,當移位寄存器內存儲的碼組X與要檢測的幀同步碼組Y相等時,即認為檢測到一個幀同步碼組[3]。

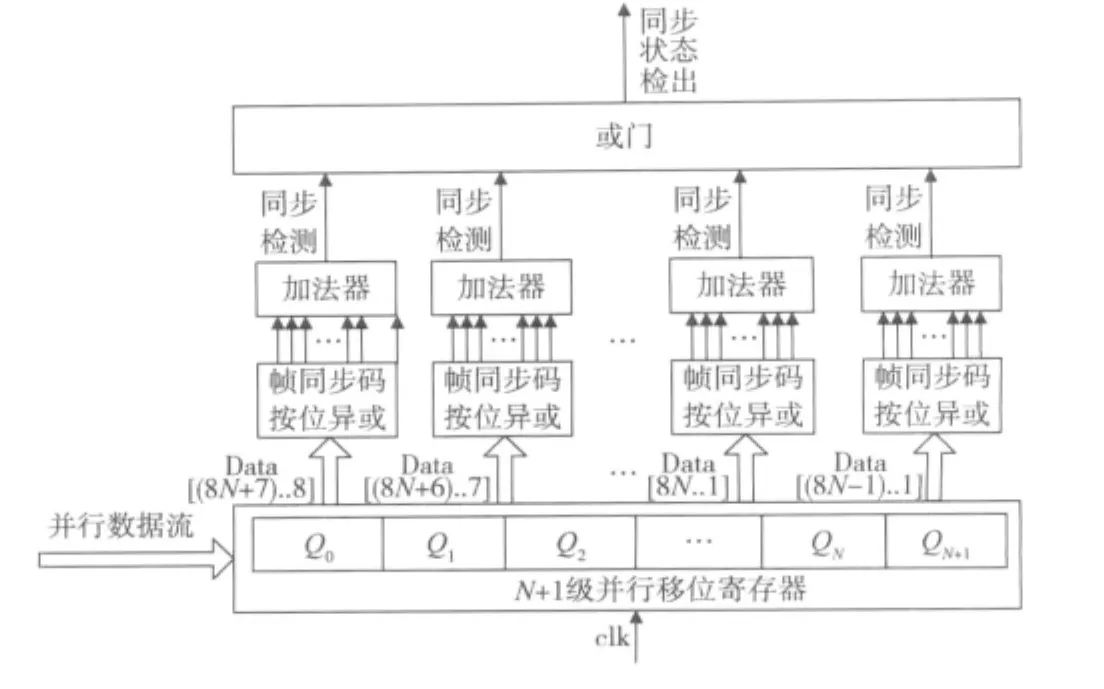

AOS協議中規定的ASM與交織深度有關,以ASM字節數N為例,并行幀同步碼檢測器需要N+1級并入并出移位寄存器。其目的在于允許待檢并行碼流有一個字節的滑動,這樣無須考慮數據串并轉換的開始,均可正確檢出ASM,調整數據輸出。并行碼流按時鐘節拍逐字節地送入并行幀同步碼檢測器,與此同時,在該時鐘頻率下,從存儲字節的高位依次滑動取出各路待檢ASM。每一路待檢ASM都與給定的ASM按位進行異或運算。運算后的結果累加求和,若小于預先設置的誤碼容錯范圍,即判定為一個有效的ASM。最后,將所有幀同步檢測的結果進行或運算,得到最終的同步狀態。并行幀同步檢測的原理框圖如圖2所示。

圖2 并入并檢幀同步檢測的原理框圖

2.2 設計方案

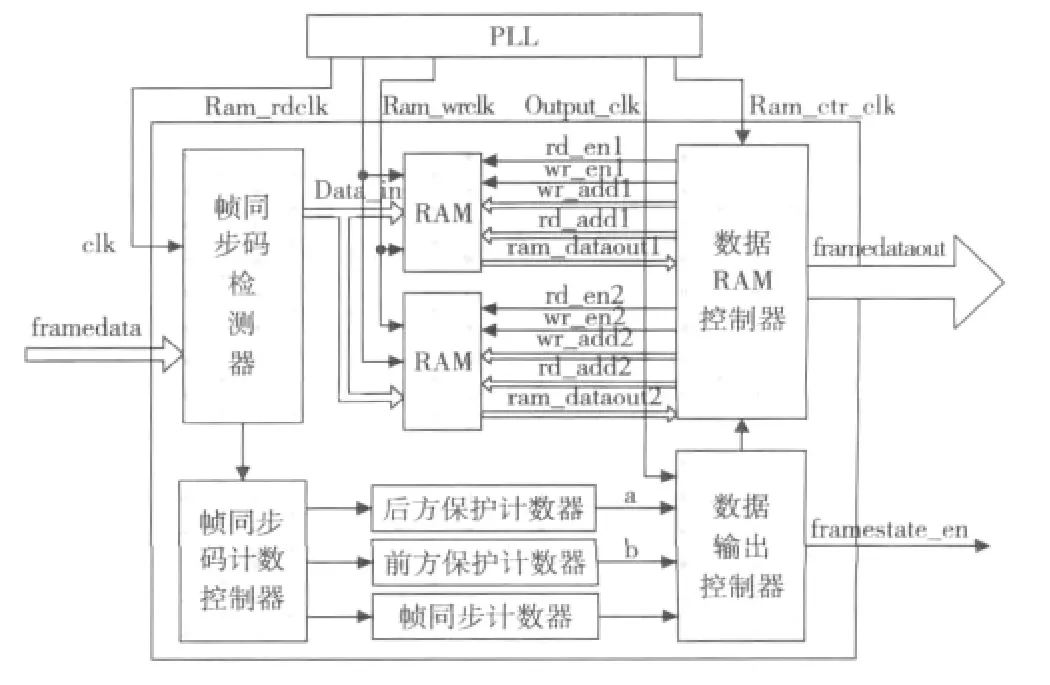

FPGA實現并行幀同步碼檢測的頂層原理圖如圖3所示。該系統是由PLL模塊,幀同步碼檢測器,幀同步碼計數控制器,前、后方保護計數器,幀同步計數器,數據RAM控制器,數據輸出控制器和雙RAM組成。

圖3 并行幀同步碼檢測的頂層原理圖

幀同步碼檢測器檢測數據中的ASM,若該ASM在誤碼容限范圍內,則向幀同步碼計數控制器輸出已檢測到ASM的使能信號。幀同步碼計數控制器接收已檢測到ASM的使能信號,將幀同步的狀態分成前方保護時間、后方保護時間和幀同步時間,分別送入與之相連接的計數器,數據輸出控制器根據上述計數器的不同數值來控制幀同步碼檢測后的數據輸出和幀同步狀態的使能輸出。整個處理過程,采用雙RAM進行數據的存儲。

3 仿真驗證與分析

并行幀同步檢測的功能驗證在ISE 12.2和Modelsim SE6.5的環境下完成,驗證所采用的芯片是Xilinx Virtex-5系列的XC5VSX50T。實驗測試在光纖系統中完成,其中光纖傳輸的碼速率為1.25 Gbit/s,物理層8B/10B解碼后的8 bit并行數據時鐘為125 MHz,FPGA芯片處理時鐘的最小值為125 MHz。

3.1 性能仿真

3.1.1 檢測速率

針對并行碼流,設其字節寬度為P(單位bit),那么采用并入并檢方法,其處理時鐘頻率是傳統方法的1/P。針對串行碼流,需在并行幀同步碼檢測器的前端增加串并轉換,這樣芯片只在串并轉換部分采用高速時鐘,剩余部分均采用低速時鐘,降低芯片的性能要求。

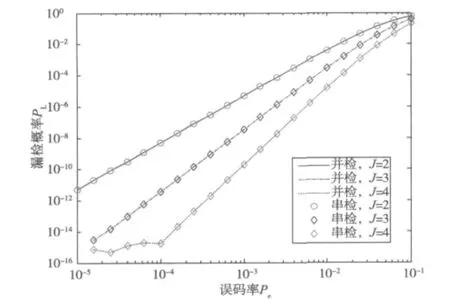

3.1.2 漏檢概率

仿真參數設置如下:M=32 bit;誤碼率Pe的范圍是10-5~10-1;誤碼容限J的范圍是2~4;字節寬度P=8 bit;幀同步檢測方式為并檢和串檢,仿真結果如圖4所示。從圖中分析可得,漏檢概率隨誤碼率的增加而增加,隨誤碼容限的增加而降低。在不同幀同步檢測方式下,誤碼率與漏檢概率的關系曲線重合,說明二者性能一致。

圖4 不同誤碼率下串檢和并檢的漏檢概率

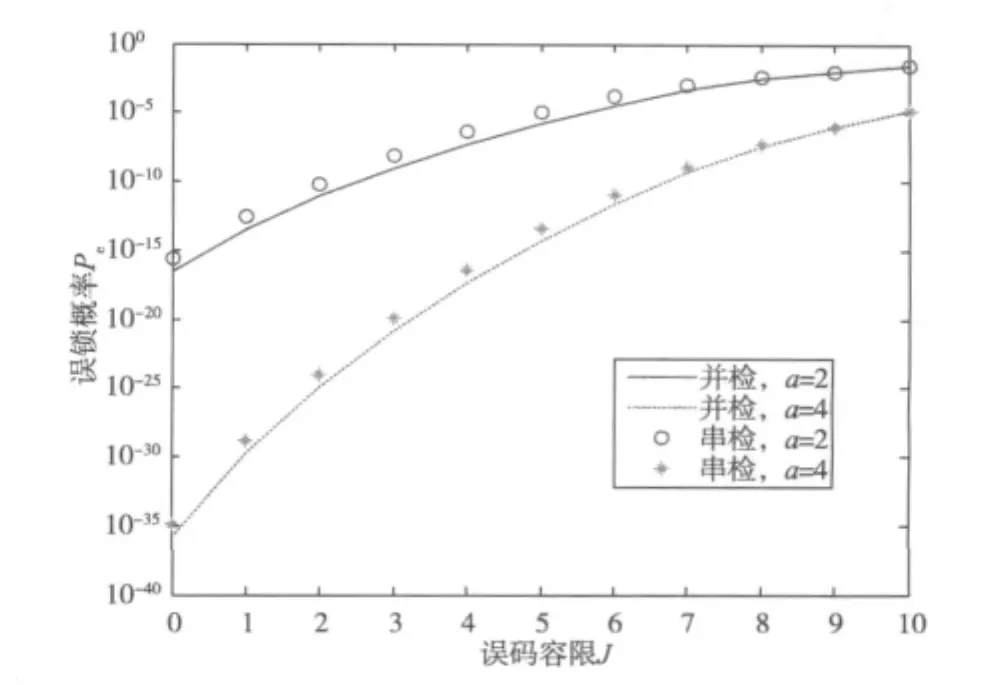

3.1.3 誤鎖概率

仿真參數設置如下:M=32 bit;幀長L=1 024 byte;誤碼容限J的范圍是0~10;誤碼率Pe的范圍是10-5~10-1;后方保護時間a的取值1~6;字節寬度P=8 bit;幀同步檢測方式為并檢和串檢。仿真結果只給出a=2和a=4兩種情況,如圖5所示。從圖中分析可得,誤鎖概率隨誤碼容限的增加而增加,隨后方保護時間的增加而減小。在J=2,a=2時,并行檢測的誤鎖概率Pws=7.766 9×10-12,而串行檢測的誤鎖概率Pws=6.212 2×10-11。說明在相同誤碼容限和后方保護時間的前提下,并檢方式比串檢方式的誤鎖概率小。

圖5 不同誤碼容限下串檢和并檢的誤鎖概率

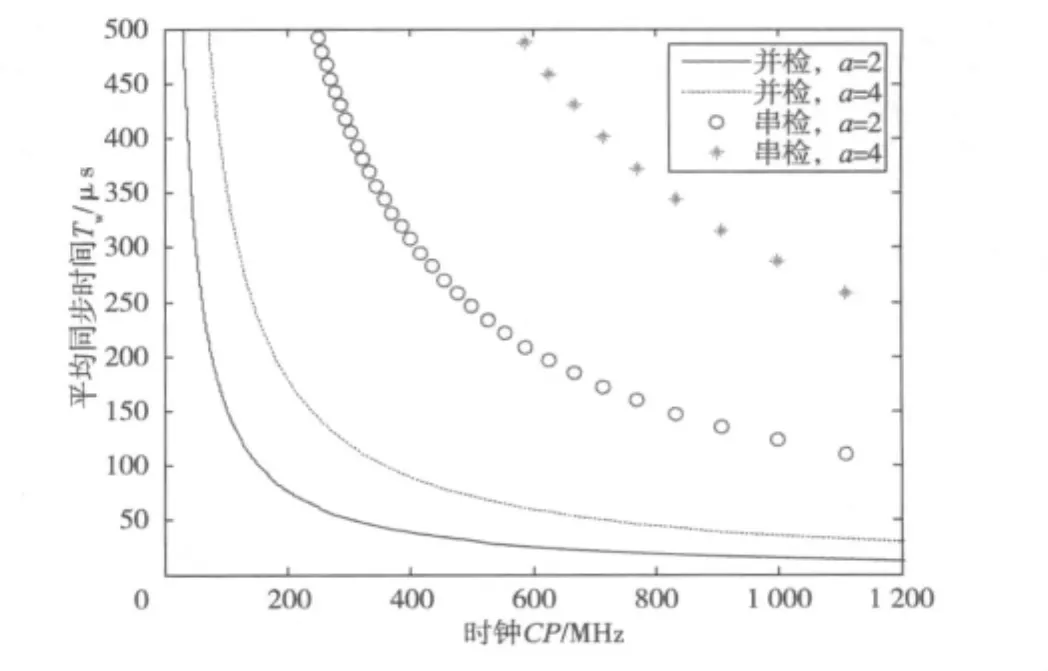

3.1.4 平均同步時間

仿真參數設置如下:M=32 bit;后方保護時間a的范圍是1~2,L=1 024 byte;字節寬度為P=8 bit;幀同步檢測方式為并檢和串檢,仿真結果如圖6所示。從圖6分析可得,平均同步時間隨CP的增加而減小,隨后方保護時間的增加而增加。在a=2時,CP=200 MHz,并行檢測的平均同步時間Tw=76.8 μs,而串行檢測的平均同步時間Tw=614.4 μs;CP=400 MHz,并行檢測的平均同步時間Tw=38.4 μs,而串行檢測的平均同步時間 Tw=307.2 μs。說明在相同的后方保護時間下,并檢方式比串檢方式的平均同步時間小。

圖6 不同時鐘頻率下串檢和并檢的平均同步時間

3.1.5 平均同步保持時間

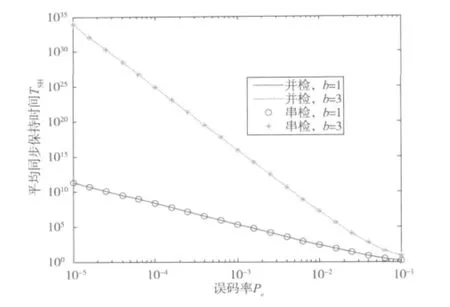

仿真參數設置如下:M=32 bit;誤碼容限J的范圍是2~4;誤碼率Pe的范圍是10-5~10-1;前方保護時間b的范圍是1~4;字節寬度P=8 bit;幀同步檢測方式為并檢和串檢。仿真結果只給出b=1和b=3兩種情況,如圖7所示。從圖中分析可得,平均同步保持時間隨誤碼率的增加而較小,隨前方保護時間的增加而增加。在不同幀同步檢測方式下,誤碼率與平均同步保持時間的關系曲線重合,說明二者性能一致。

圖7 不同誤碼率的平均同步保持時間

上述仿真,并行檢測的數據輸入均為并行碼流,而串行檢測的數據輸入均為串行碼流。

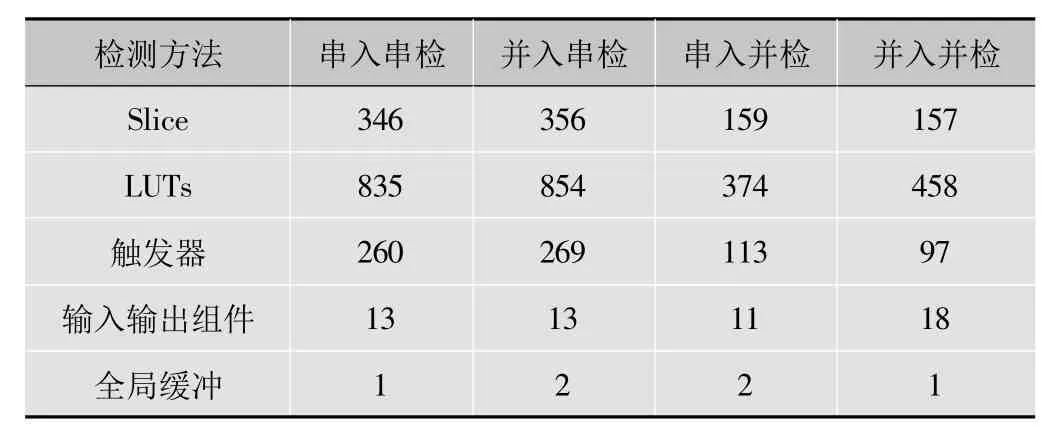

3.1.6 資源使用

本文分別對幀同步碼的串行檢測和并行檢測進行功能仿真,每種檢測的輸入又分為串行碼流和并行碼流兩種。考慮的芯片資源參數包括Slice數目、LUTs、觸發器、輸入輸出組件和全局緩沖5部分。從表1分析可得,并入并檢方法雖使用過多的輸入輸出組件和LUTs,但在重要資源的使用上,如Slice數目、觸發器和全局緩沖的使用最少。

表1 4種檢測方法的資源使用情況

3.2 結果分析

在選擇幀同步檢測方法及系統參數時,總是希望處理時鐘頻率越低越好,漏檢概率越小越好,誤鎖概率越小越好,平均同步時間越短越好,平均同步保持時間越長越好,使用芯片資源越少越好。綜上分析可得:并行檢測方法在漏檢概率和平均同步保持時間方面的性能與串行檢測一致;而在處理時鐘頻率、誤鎖概率、平均同步時間和芯片資源使用方面的性能優于串行檢測。

4 小結

并入并檢AOS幀同步檢測方法采用待檢數據并行輸入,幀同步檢測并行處理,解決了傳統的串行檢測方法的幀同步檢測能力受限問題,適用于高速串行碼流或并行碼流的同步搜索。從性能上分析,該方法在處理時鐘頻率、誤鎖概率、平均同步時間方面優于串行檢測。在芯片資源使用方面,雖使用了較多的輸入輸出組件,但重要資源的使用最少。

:

[1]Advanced orbiting systems,networks and data links:summary of concept,rationale,and performance[EB/OL].[2012-01-05].http://webapp1.dlib.indiana.edu/cgi-bin/virtcdlib/index.cgi/4278621/FID2/CCSDS/700X0G3.PDF.

[2]肖志東,李帥.AOS系統中的幀同步技術性能分析與仿真[J].沈陽理工大學學報,2010,29(3):20-25.

[3]王蘭勛,張鎖良.一種幀同步碼檢測方案及實現[J].河北大學學報:自然科學版,2004,24(2):180-183.

[4]范寒柏,谷力偉,趙冉.幀同步系統的FPGA設計與實現[J].電子設計工程,2009,17(8):36-38.

[5]單寶堂,王華,張健,等.一種并行幀同步設計方案的提出、設計與應用[J].電子技術應用,2005(6):61-64.

[6]陳燕.基于FPGA高速幀同步設計及性能分析[J].無線電工程,2010,40(5):25-26.

[7]孫玉.數字復接技術[M].北京:人民郵電出版社,1983.