數字ATE上內部示波器的實現

李 杰, 劉林生

(北京自動測試技術研究所, 北京 100088)

0 引言

內部示波器是ATE測試設備上的一個調試工具模塊,在大多數進口ATE設備上都配備了這個模塊。內部示波器的主要功能就是可以動態地顯示ATE被測芯片某個輸出管腳的實時波形,它極大豐富了ATE設備的調試手段、降低了測試成本、縮短了編程和調試的周期,是ATE測試設備進入中高端市場必備的一個模塊。

1 內部示波器

內部示波器從主要功能上看與我們現在使用的外部示波器沒有本質的區別,一些基本的示波器功能它都可以提供。但對于測試工程師來說,在編寫測試程序或者調試測試程序時,相對于外部示波器來說,內部示波器的優點是非常明顯的。首先,內部示波器相對外部示波器最大的優點在于采樣點的不同,外部示波器的采樣點一般都在芯片的管腳上,內部示波器的采樣點在管腳電路驅動/比較器的輸出端,這就決定了內部示波器能更精確地顯示輸出的波形;其次,外部示波器即使內阻再大在某些情況也是不能被忽視的,這就導致了測試準確度的下降,而內部示波器是不涉及內阻問題的;第三,在某些特殊場合,比如中測的時候,看不到被測的圓片,所以根本沒有條件使用外部示波器,這也是內部示波器的優勢;綜上所述,內部示波器對于中高端ATE設備來說是一個必不可少的模塊。

2 內部示波器的實現原理

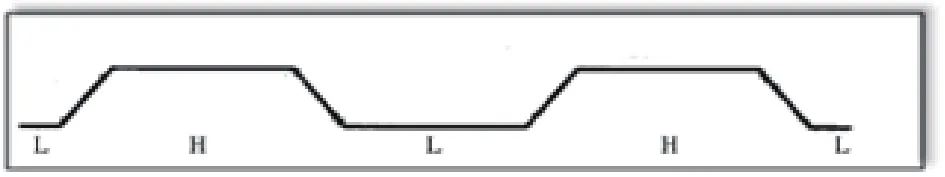

對于數字ATE設備來說,它沒有配備波形采集的模塊,那要如何實現對被測芯片輸出波形的采集呢?我們看圖1所示的一個波形,它看起來雖然是連續的,但我們同樣可以把它看成是由無數個點組成的,把這些點連起來就成了連續的圖形了。而數字ATE設備對輸出管腳的輸出電壓是可以采集到的,所以在一個測試周期內,每間隔一定的時間對輸出管腳采集一次輸出電壓,并把這些采集到的電壓值進行作圖處理,只要間隔時間足夠小,那么最終做出的就是該管腳的連續輸出波形了。

圖1 典型輸出波形

數字ATE設備采集輸出管腳電壓值有兩種常見的方法,一種方法是通過直流參數測試,對輸出管腳加流測壓測得輸出電壓值。這種方法顯然不適合用于此處,因為直流參數測試加流測壓的方法實際上是對輸出管腳加入負載的情況下測得的輸出電壓值,這個電壓值是和負載有關的,不能準確地反映輸出管腳的波形情況。另一種方法是功能測試得到管腳輸出電壓值,通過對輸出高/低電平比較電壓的設置,以及功能測試是否通過來得到管腳輸出電壓的值。這個電壓值是和負載無關的,能夠準確地反映輸出波形。

3 內部示波器在測試儀上的實現

下面以我所研制的BC3192V50數字集成電路測試系統為例,詳細說明內部示波器模塊的實現方法以及需要解決的一些技術難點。

首先來看一下如何用功能測試的方法來采集輸出管腳的輸出電壓。對于一個芯片的輸出管腳來說,輸出波形與功能測試的測試圖形是一一對應的,如圖2所示,測試圖形的每一拍對應輸出波形的一個周期,右圖所示的波形在測試圖形文件上顯示的就是“LHLHL”,功能測試實際上就是檢驗輸出管腳的輸出狀態是否正確。如果在測試圖形文件上某輸出管腳的內容是“LHLHL”,功能測試又顯示“通過”,則可判斷該管腳的輸出波形如圖2所示。ATE上的“H”和“L”是由輸出高/低比較電平(VOH/VOL)這兩個參數決定的,管腳輸出電壓大于VOH,ATE判定為“H”狀態,小于VOL判定為“L”狀態,這就不難看出,如果把VOH和VOL設定為同一個電壓值,并且從0V(或者VCC)開始以一個很小的1V遞增(或遞減),每次都進行功能測試,則在功能測試結果變化的那個點對應的VOH和VOL的電壓值就是輸出管腳此刻的輸出電壓值。

圖2 典型輸出波形詳解

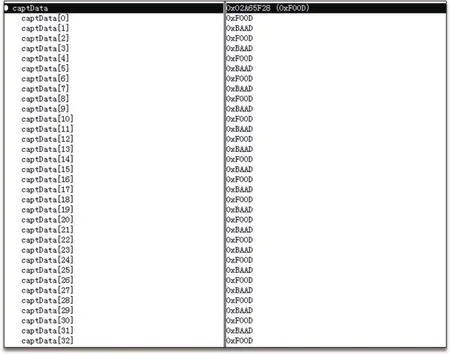

通過上面的介紹可以看出,要得出輸出電壓值,必須在功能測試結果變化的跳變點上才可以,那么問題又出現了,功能測試是對所有輸出管腳做判斷的,如何才能得到所需輸出管腳的功能跳變點呢?常規方法是對功能測試的測試圖形做屏蔽處理,也就是說將所有無關輸出管腳的測試圖形文件內容改為“X”(輸出不關心狀態),這就保證了只對關心的輸出管腳做功能測試。但這種方法既麻煩又費時,還容易產生錯誤,這里我們采用BC3192測試系統自帶的失效存儲器來完成這個操作。失效存儲器在每次功能測試結束后自動存儲,它存儲的內容是所有輸出管腳功能測試的結果,失效為“1”,通過為“0”,我們要判斷某個管腳在測試圖形某一拍的功能測試結果,只需讀出失效存儲器對應位的內容就可以了。圖3顯示了BC3192失效存儲器的內容,該測試圖形有8拍,前14拍是流水。

圖3 失效存儲器內容

通過BC3192測試系統的VOH和VOL電平的設定以及失效存儲器內容的讀取,我們現在可以采集到輸出管腳在時鐘周期某一點上的輸出電壓了,但如何在整個時鐘周期的不同點上采集輸出電壓呢?數字ATE設備上驅動/響應格式化器是必不可少的模塊,而響應格式化器的功能之一就是讓用戶自行決定在一個時鐘周期內何時進行功能比較,它一般提供兩種比較方——沿比較和窗口比較。窗口比較需要設定一個時間窗口,比如時鐘周期100 ns,窗口設定為【60 ns,80 ns】,則功能測試會在【60 ns,80 ns】這個窗口內對輸出電平進行比較,只要出現了正確的電平,就判斷功能測試通過。而沿比較只需要設定一個比較沿,比如時鐘周期100 ns,比較沿設定為80 ns,則功能測試會在80 ns時對輸出電平進行比較,80ns時的輸出電平正確功能測試才會判斷通過。BC3192測試系統響應沿的分辨率為1 ns,所以只需要使用沿比較的方式進行功能測試,每間隔1 ns采集一次輸出管腳的輸出電壓,就可以在整個時鐘周期內采集到足夠多的輸出電壓值了。

通過上面的分析,我們使用軟件編程,把周期數作為第一循環,采樣時間作為第二循環,VOH和VOL電壓值作為第三循環,對芯片進行功能測試,把得到的輸出電壓值作圖就可以得到輸出波形了。但這并不是實際的波形,它和實際波形還有一定的差距,下面我們來討論內部示波器實現中的一些難點和波形優化的問題。

首先我們不能忽視的一點是所關心輸出管腳的測試圖形文件上如果出現了“X”(輸出不關心)和“T”(輸出三態)這兩個狀態,在VOH和VOL相等的情況下,功能測試是不會出現跳變點的,這就導致輸出電平采集的失敗。為了避免這種狀態的產生,在電壓采集之前,對測試圖形文件還要進行一定的處理,將文件中的“X”和“T”狀態任意改為“H”或者“L”,以保證功能測試跳變點的出現,從而能順利地采集到輸出電壓值。

其次對于內部示波器模塊來說,采集時間是個敏感問題,從原理來看,3個循環嵌套,1 ns的分辨率,電壓步進值如果也很小的話,整個的采集時間是很長的,如何能優化這個采集時間也是一個難點。要對VOH和VOL電壓循環優化,我們可以首先先確定每個時鐘周期內輸出波形的預期值,這可以通過測試圖形文件得到,預期值為低,則循環從VCC開始,預期值為高,則循環從0V開始,這就能有效減少給循環的次數,同時還可以采取半值比較的方法,比如循環從VCC開始,下一個點檢測VCC/2,如跳變點沒產生,則檢測VCC/4,如產生了檢測3VCC/4,以此類推,可大大縮短VOH和VOL電壓循環的次數,減少采集時間。對采集時間循環的優化可根據測試周期決定,保持該循環最大循環100次較為適宜,也就是說周期大于100 ns的時候,可以相應增加采集時間間隔,保證循環次數不會太大。

對所得到的輸出管腳波形進行優化和平滑是必需的,最主要的原因就是該波形存在過沖問題。過沖一般會出現在輸出波形變化的時候,也就是波形從低變高或者從高變低的時候,過沖的電壓值一般都很高,有可能達到VCC,但它不是真實的,這主要是由采集時間接近0 ns的時候,功能測試結果不穩定造成的。根據這種情況,把采集的前5-10個點進行優化,可以得到比較真實的波形。波形的平滑也是必須的,因為即使是1 ns采集間隔,在作圖的時候間隔也是很大的,如果不進行平滑,做出的波形銳度會很大,看起來很不舒服。我們可以通過軟件的計算,在兩個間隔點之間再取100個點,每個點的增量為間隔的1%,這樣再畫出的波形就較為真實了。

4 結論

內部示波器 作為一個非常實用的調試模塊,越來越受到測試工程師的歡迎,國產設備配備該模塊是大勢所趨,也必然是國產設備進入中高端市場的必備軟件模塊。

[1]逄珊.ATE軟件系統測試方法研究[J].中國測試,2009,35(1).

[2]葉海明,周紹磊,徐俊彥.通用測試系統模型化技術研究[J].計算機測量與控制,2009,17(9).

[3]申莉,沈士團.通用自動測試系統模型化設計[J].北京航空航天大學學報,2009,35(7).

[4]逄珊.ATE軟件系統測試方法研究[J].中國測試,2009,35(1).

[5]成孝剛,劉國慶,姜華.ATE測控平臺的研究與應用[J].微計算機信息,2009,25(7).

[6]葉海明,周紹磊,徐俊彥.通用測試系統模型化技術研究[J].計算機測量與控制,2009,17(9).

[7]樊寅逸,何海光.AT45DB081B在數據采集系統中的應用[J].電子元器件應用,2007(3).

[8]岳麗華,韋鵬,鐘誠.一種自適應的復合多路flash存儲結構[J].中國科學技術大學學報,2008(7).