高階QAM載波恢復的FPGA設計實現★

徐步威

(電子科技大學電子工程學院, 成都 611731)

0 引言

QAM調制方式特別是高階QAM調制由于其較高的頻譜利用率得到了廣泛應用。隨著4G技術的研發和數字電視的普及,QAM將更加受到重視。

QAM隨著階數的增加,對載波恢復的要求也越嚴格。對于高階QAM載波恢復,一個很重要的問題是盲恢復。它是在沒有導頻或者訓練序列幫助的情況下,根據接收到的QAM信號提取出相位誤差信息。但是這種方式中同步帶寬和相位抖動情況是一對矛盾問題。針對上述考慮,本文采用雙模式切換的極性判決相位檢測算法,在捕獲模式利用有較大頻偏捕獲能力的極性判決算法[1],而在跟蹤模式中則使用傳統的DD算法[2-3],因為DD算法具有很好的跟蹤性能。這種算法具有更好的頻偏捕獲能力和健壯性。

隨著微電子技術的發展,FPGA技術也在通信中得到了廣泛的應用。其高效的運算與高集成度在通信系統中占據了越來越多的優勢。本文闡述的FPGA設計方案也在Altera公司的FPGA芯片上得到了實現。

1 極性判決算法結構及設計

1.1 極性判決算法的結構

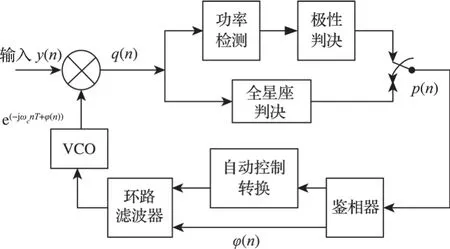

極性判決算法鎖相環路由判決器,鑒相器,環路濾波器,壓控振蕩器VCO以及一個乘法器組成。

極性判決算法的結構及信號流程如圖1所示。為便于理解,這里簡述極性判決算法原理。假設n時刻接收到信號y(n),解調之后得到信號q(n)。然后對信號q(n)進行功率檢測,即通過判斷q (n )2>τ2(τ為功率檢測門限)是否成立來選擇需要鑒相的接收信號點。q (n )2<τ2時相位檢測輸出為0,q (n )2>τ2時相位檢測輸出該信號點的極性判決值。并將解調后的信號q(n)與極性判斷的復信號p(n)相除取虛部,得到誤差信號e(n),再經環路濾波器,VCO后對輸入信號y(n)進行補償。所謂極性判決就是根據接收到的符號的極坐標判決到對應對角線上。當極性判決環路鎖定大概頻偏后便轉向DD算法環路進行跟蹤并糾正剩余的小頻偏。

圖1 極性判決算法流程圖

1.2 多門限極性判決

傳統極性判決算法由于其單一的判決門限導致收斂速度慢鎖定誤差大等缺陷。對于高階高碼率的QAM信號來說這是不符合需求的。為解決以上缺陷以適應高階高碼率QAM信號,本文采用多門限極性判決。

多門限極性判決[4]的核心思想是增加了鎖定誤差為零的信號點。在星座圖中,根據能量的不同,將信號劃分為不同的能量圈。通過降低最外圈門限,可以讓更多的信號點通過,但是會引入鎖定誤差,因此可以通過設定多個門限來多重篩選信號點以逐步鎖定相位。

1.3 環路濾波器和VCO結構設計

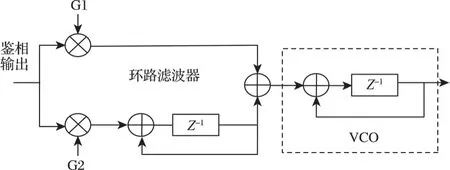

一階環路濾波器和VCO組成的二階環路如圖2所示。其中G1和G2為環路濾波器系數,z-1為一個周期延。

圖2 環路濾波器與VCO環路結構

其中系數G1,G2可以通過以下經驗公式計算得到:

上述公式中ξ為阻尼系數,fn為環路濾波器本振頻率,Ts為符號周期。

1.4 極性判決算法模式轉換設計

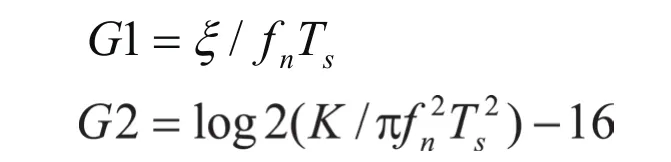

從捕獲模式轉換到跟蹤模式需要有一個轉換模塊來控制環路的切換[5-6]。模式轉換控制有多種方法,可以利用均方誤差MSE,也可以根據幅值的平均或根據信噪比的高低為門限來實現轉換模式的控制并改變環路濾波器參數的調整。本文采用的是MSE方法來控制模式的轉換。下面介紹MSE控制方法的具體設計,圖3為實現的流程圖。

圖3 模式轉換算法流程圖

圖3中的Uc是指極性判決環路的環路濾波器輸出。我們針對極性判決環路的環路濾波器輸出,每64個數據求一個均值,然后對這些均值數據,每32個均值求一次方差,最后針對方差來設置一個門限,這個門限具體可以通過對環路濾波器輸出的仿真來求得。同時在這個設計中,我們總共設置兩個條件來作為模式切換的條件,其中一個就是針對方差的門限判斷,另一個是用于防止假鎖出現的均值符號判斷。由于均值有可能出現負值而導致假鎖現象,所以需要對均值符號做判斷,如果每32個均值中超過半數為正值,則斷定此次方差門限判決結果有效。通過以上轉換控制流程可以準確及時地對模式進行轉換。

2 MATLAB仿真結果與分析

首先給出仿真的參數:調制方式為128QAM,采樣率為102.4 MHz,信號碼速率為25.6 MHz,信噪比為30 dB,對輸入信號加入300 kHz的頻偏和π/3的相偏,功率檢測設置雙門限2.2和13.5,仿真點數100 000。同時這里需要給出本文使用的數字接收機[7-8]系統框圖以示具體信號流程,系統框圖如圖4所示。

圖4 數字接收機部分系統框圖

根據系統框圖,我們將定時同步和信道均衡之后的數據作為本文載波恢復仿真的輸入數據。

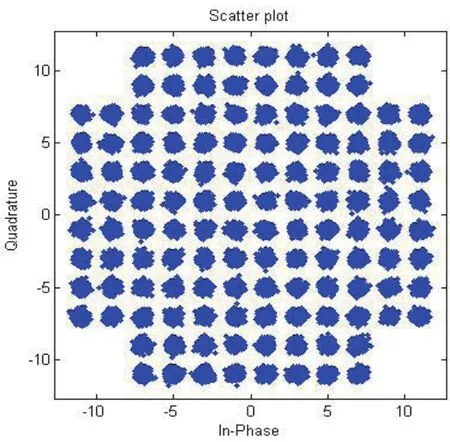

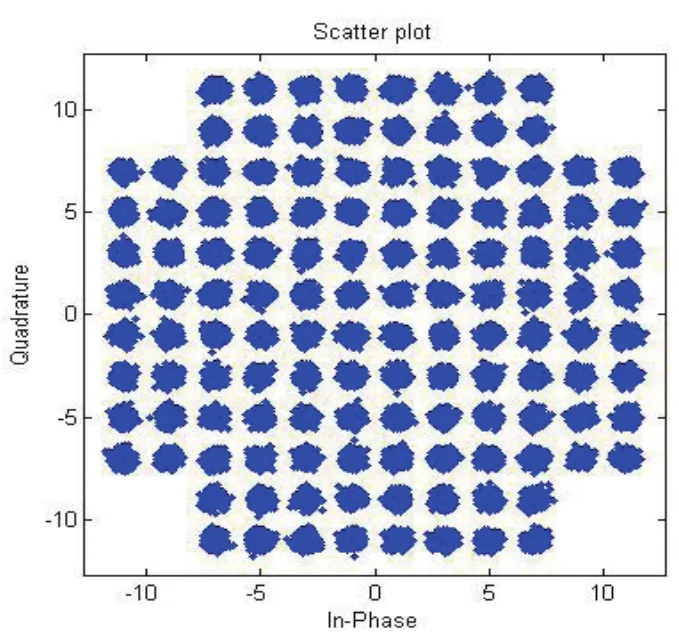

下面我們看載波恢復算法頻偏跟蹤效果以及星座圖。分別如圖5與圖6所示。

圖5 載波恢復頻偏跟蹤結果

圖6 載波恢復后星座圖

從上述圖中可以看到環路最終鎖定效果非常好,頻偏穩定在300 kHz左右。并且輸出星座點清晰可見,達到了理想的情況。

3 定點仿真與FPGA設計

在FPGA設計實現之前,需要通過定點仿真來限定各個變量的精度,分析有限字長對系統性能的影響,權衡資源消耗和系統性能,從而得出各個信號合適的位寬。

圖7為載波恢復算法FPGA實現框圖,框圖反映了載波恢復算法實現的信號流程以及模塊的劃分。

算法框圖中clk為全局時鐘信號,此處為碼速率25.6MHz ;reset為系統復位信號;Iin,Qin分別是輸入數據的實部虛部;Iout,Qout分別是輸出數據的實部虛部。這里所有模塊均使用的全局時鐘,因為碼速率始終不變。cmultip_mult模塊為輸入信號與VCO輸出的復乘模塊,在復乘模塊之后對應兩個環路,分別是極性判決環路和DD算法環路。在捕獲階段系統運行在極性判決環路,首先是經過power_dectect 模塊即功率檢測模塊,然后將判決結果送往鑒相器模塊phase_detect_a進行鑒相,之后送往環路濾波器loop_filter_a,對于環路濾波器輸出會有一個計算其輸出值均方誤差的MSE模塊,并由MSE模塊產生一個環路切換控制信號control。這個控制信號會實現2個控制功能,一個是決定是否轉向DD算法環路,另一個是選擇輸入到VCO模塊的數據,即當前所運行環路的濾波器輸出數據。當環路切換至跟蹤模式時,先進行全星座判決即dd_adjudge模塊,然后將判決結果送至鑒相器phase_detect_b,再送交環路濾波器loop_filter_b,之后輸出給VCO模塊。

圖7 載波恢復算法FPGA實現框圖

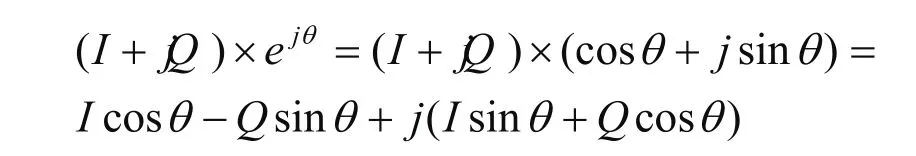

值得特別說明的是復乘模塊與VCO模塊,根據算法我們需要將輸入數據和VCO做一次復乘運算。這里直接將每個數據分解為實部虛部分別和正余弦值的乘加運算,于是就有:

這其中實部虛部均分開單獨處理。上式中涉及的正余弦的值通過VCO模塊的正余弦查找表來獲取。同時由于VCO是進行相位累加運算,最后的相位值必然遠大于2π,而我們的正余弦查找表是存儲的一個周期的值,因此我們需要在每次累加之后對累加的相位值進行對2π求余。

4 FPGA仿真與調試結果

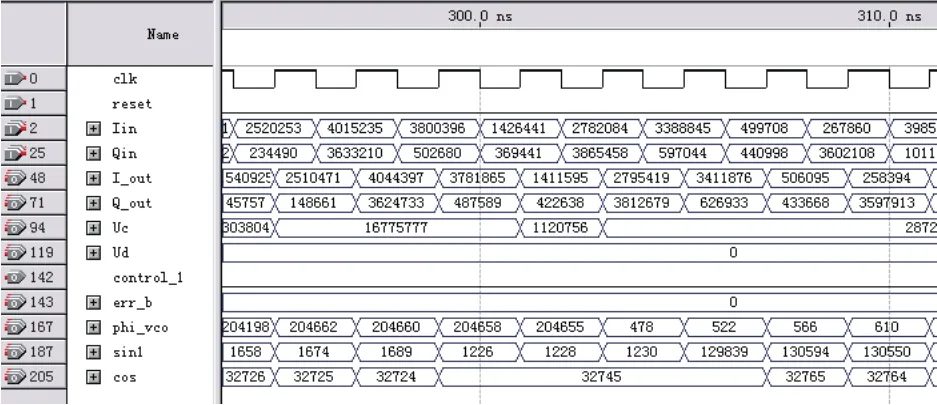

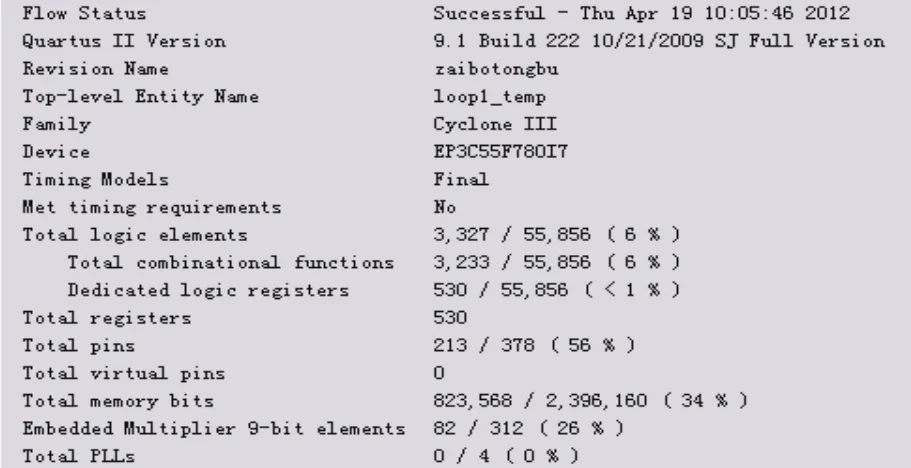

這里FPGA功能仿真使用QUARTUS軟件自帶的仿真工具。輸入數據采用MATLAB仿真時候的數據源以便對比,這之前需要對其量化。圖8為整體的功能仿真圖。其中Uc,Ud分別是極性判決環路和DD環路的環路濾波輸出,從圖中可以看到Ud數據還為0,這是因為環路還沒有切換的原因,當環路切換后Uc為0,Ud為對應數據;control_1為環路切換控制信號,當滿足環路切換條件時置1,否則為0;phi_vco為相位累加結果,也即正余弦查找表的輸入;sin1,cos為查找表結果,并作為復乘模塊輸入。經綜合后該算法結構的資源使用情況如圖9所示,可見所消耗的邏輯資源很少。

圖8 載波恢復算法FPGA整體仿真圖

圖9 載波恢復算法FPGA資源使用情況

在仿真后我們將需要的仿真結果導入到MATLAB中處理可以得到各個環節的情況。這里給出最后的頻率收斂情況(見圖10)以及載波恢復后的星座圖(見圖11)以示設計的效果。從圖中可以看到FPGA處理的效果與MATLAB仿真結果基本一致,且星座圖效果理想。這說明了本文的FPGA設計是完全符合實際要求的。

圖10 FPGA仿真載波恢復頻率收斂曲線

圖11 FPGA仿真載波恢復輸出星座圖

5 結論

本文針對高階QAM的載波恢復,采用了雙模式切換的極性判決算法,并在實際使用中收到了很好的效果。同時,本文針對128QAM設計的FPGA實現方案效果理想,且消耗的邏輯資源很少,最后經過時序約束后運行速率可以達到29 MHz,完全滿足系統25.6 MHz的要求。

[1]Kim,Kim-Yun,Choi,Hyung-Jin.Design of Carrier Recovery Algorithm for high_order QAM with large Frequency Acquisition Range[J].IEEE,ICC 2001,Helsinki,Finland,2001, 6:(11-14):1016-1020.

[2]HORIKAWA I,MURASE T,SAITO Y.Design and performances of a 200 Mbit/s 16QAM digital radio system[J].IEEE Trans.Communica-tons,1979,27(12):1953-1958.

[3]劉劍波,牛亞青.QAM調制解調系統中的載波同步算法研究[J].廣播與電視技術,2002(7):79-84.

[4]沈麗麗,米亮,葛建華.適合高階QAM載波恢復算法[J].電視技術, 2003(12):14-17.

[5]胡楠,鐘洪聲.高階QAM快速載波恢復電路設計[J].通信技術,2007(11):57-60.

[6]梁海麗,段吉海,游路路.1024QAM調制解調系統的FPGA 實現[J].電視技術,2007,31(4):31-32.

[7]陳祝明.軟件無線電基礎[M].北京:高等教育出版社:58-124.

[8]周媛,賈懷義.基于FPGA 的全數字64QAM調制解調器設計[J].電視技術,2007,31(S1):40-42.