FPGA的寬帶步進頻率信號源設計

孫作亮,李廷軍,鐘洪聲

(電子科技大學 電子工程學院,成都611731)

引 言

頻率源是通信系統、雷達系統、儀器儀表等現代電子系統的核心部分之一,其性能的優劣直接影響到整個系統的穩定性。目前的頻率合成方法有多種,其中,應用廣泛的有直接數字頻率合成技術(Direct Digital Synthesis,DDS)和鎖相式頻率合成器(Phase Locked Loop,PLL)兩種,但二者又有各自的優缺點。DDS具有較高的頻率精度和雜散抑制,但寬頻帶是其實現難點;而PLL具有較高的頻率輸出帶寬,但是輸出頻率不可避免的相位噪聲和雜散是其缺陷[1]。本文論述的寬帶步進頻率信號源設計結合了二者的優勢,能夠產生低噪聲雜散并且高輸出帶寬的信號。

由于近些年來,寬帶步進頻率信號以其獨特的優勢在通信和雷達系統中得到了廣泛的應用,因此,本文重點討論LS波段寬帶步進頻率信號源設計方法,考慮到FPGA具有較高的系統集成和時序控制性能,設計采用Xilinx公司的spartan3 系列FPGA 進行頻率源模塊的配置和控制,使頻率源輸出的頻率能夠滿足設計要求。

1 頻率合成器的工作原理

頻率合成器芯片采用ADI公司的寬帶頻率合成器芯片ADF4350。該芯片是一款內部集成VCO、鑒相器、電荷泵、分頻器等的低噪聲雜散PLL(鎖相環)芯片[2]。VCO基波輸出頻率范圍為2 200~4 400 MHz,支持小數和整數N 分頻,利用輸出端的1/2/4/8/16分頻電路可以產生帶寬為137.5~4 400 MHz頻段內的任意頻率。片上VCO 內核由3 個獨立的VCO 組成,其輸出靈敏度為33 MHz/V,每個VCO 使用16 個重疊頻段,可以僅通過0.5~2.5V 壓控范圍,便可以控制整個頻帶的頻率輸出,該芯片采用5 mm×5 mm 封裝,具有集成度大、可靠性強、功耗低等特點。ADF4350 的詳細信息見參考文獻[2]。

ADF4350頻率合成器的參考頻率fREF由外部提供,該頻率經芯片內部R 分頻器后提供給鑒相器,作為鑒相參考頻率FPFD。射頻輸出RFOUT的反饋頻率經內部N 分頻器后輸出的頻率為FN,鑒相器將FN與FPFD比較后的相位差轉換為與之成比例的脈沖,提供給電荷泵。電荷泵產生攜帶誤差信息的推拉電流,經芯片外部的環路濾波器積分轉換成攜帶相位差信息的調諧電壓,調諧片上VCO 的壓控端,控制并輸出相應的頻率。片上VCO 的輸出頻率經輸出分頻器(1/2/4/8/16)電路輸出,產生所需射頻輸出信號:

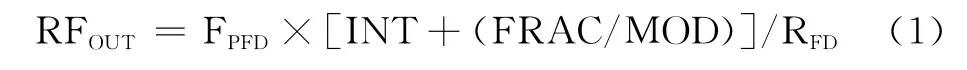

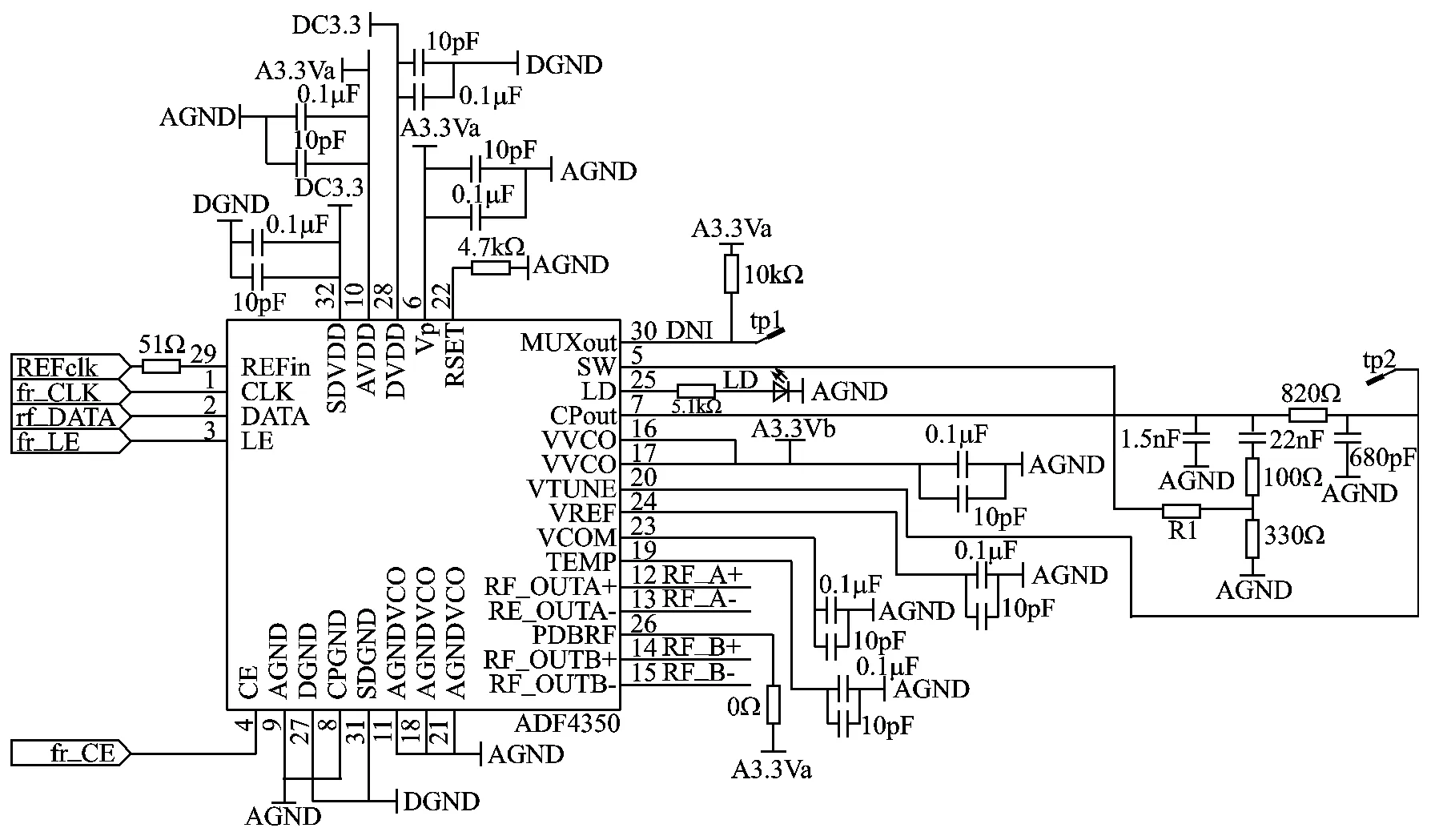

其中,INT 為芯片內部N 分頻器的整數分頻值,FRAC和MOD分別為N 分頻器的小數分頻系數的分子和分母值,射頻輸出端分頻系數RFD為1/2/4/8/16。因此,通過FPGA 配置,有規律的調整鑒相參考頻率FPFD或者內部N 分頻器的分頻值便可以實現寬帶步進頻率信號源的設計。ADF4350硬件外圍原理圖如圖1所示。

圖1 ADF4350外圍電路原理圖

電阻R1用來選擇是否使用ADF4350的快速鎖定模式[2],具體阻值根據環路帶寬值通過ADIsimPLL 仿真工具計算。本系統選用非快速鎖定模式,因此實際電路中R1電阻部分為開路。硬件電路的可測性設計可以方便后期的系統硬件調試。考慮到高頻信號的電路傳輸特點,將各電源和主要引腳添加了濾波電容,頻率輸出端采用雙端口差分形式輸出,提高了頻率輸出的抗干擾特性。

2 步進頻率源的參數設計

本文討論的寬帶步進頻率源參數為:工作頻段為1.1~2.124GHz,射頻輸出步進頻率間隔為2 MHz,即每個步進周期共輸出512 個掃描頻率值。輸出功率可調。單頻點相位噪聲優于-90dBc/Hz@10kHz,雜散優于-60dBc。

通過硬件調試發現,每次更新N 分頻器的分頻值產生步進頻率,由于分頻值的變化差異,導致芯片內部鎖相環完全失鎖,一段時間后再重新恢復鎖定。在此期間,VCO 的壓控端將出現較大的抖動,延長鎖定時間,輸出雜散嚴重,因此本文重點討論以下實現方案。

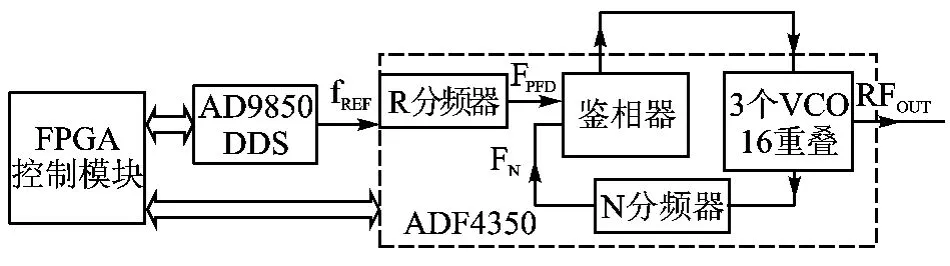

固定ADF4350內部分頻器的值,通過調整FPFD,使射頻輸出端產生滿足要求的寬帶步進頻率信號。DDS具有極高的頻率分辨率和極短的轉換時間,但其工作帶寬和輸出最高頻率受到限制。而鎖相頻率合成器具有很高的工作頻率和帶寬,但其轉換時間相對較長[3]。因此本方案將二者結合起來,融合二者優勢,便可獲得較高性能的頻率輸出。通過DDS控制改變FPFD產生滿足要求的寬帶步進頻率信號,內部寄存器分頻值沒有隨步進頻率的變化而改變,因此鎖相環失鎖時間很短,頻率輸出雜散抑制良好,滿足設計要求。整體實現框圖如圖2所示。

圖2 系統整體實現框圖

設定ADF4350頻率合成器R 分頻器中的分頻參數為0。鑒相參考頻率等于外部參考頻率即fREF=FPFD。設定系統工作在低噪聲模式,射頻輸出分頻器為2分頻,反饋端設定為VCO 基頻。本方案選用的DDS芯片為ADI公司的低成本、低相位噪聲芯片AD9850,其頻率輸出計算公式為:

其中,Phase為相位累加器的值,CLKIN為DDS參考輸入頻率,本文DDS的參考頻率由FPGA 內部數字時鐘管理單元DCM 經6倍頻輸出提供,為120 MHz。

根據頻率輸出參數設計要求,設定頻率源芯片內部分頻器值INT=160,FRAC=0,MOD=20。則由公式(1)可知:

RFOUT=FPFD×[INT+(FRAC/MOD)]/RFD=FPFD×[160+(0/20)]/2=80FPFD

因此,為了使RFOUT能夠輸出1.1~2.124GHz帶寬并且以2 MHz為步進的掃描信號,則FPFD相對應的掃描頻率范圍為:

FPFD=(1.1~2.124)GHz/80=13.75~26.55 MHz

步進間隔為:ΔFPFD=2 MHz/80=25kHz

由于R 分頻器不參與分頻倍頻工作,則有fDDS=fREF=FPFD,ΔfDDS=ΔFPFD。由公式(2)可知:

Phase=fDDS×232/120 MHz=(13.75~26.55 MHz)×232/120 MHz

ΔPhase=ΔfDDS×232/120 MHz=894 785

(phase)min=13.75MHz×232/120MHz=492 131 669

(phase)max=26.55MHz×232/120MHz=950 261 514

綜上所述,Phase配置數據應為492 131 669~950 261 514,數據更新間隔為894 785,將Phase全部的配置數據利用Matlab軟件計算得出,通過FPGA 以一定時序配置DDS即可控制ADF4350輸出端產生滿足要求的寬帶步進頻率信號。

3 測試結果

ADF4350具有兩路射頻輸出,硬件設計考慮到系統的可擴展性,分別將主輸出轉換成單端模式,傳輸至下一級。輔助射頻輸出端設計為差分輸出模式,方便系統功能擴展。電路采用3.3 V 單電源供電,實際PCB 如圖3所示。

圖3 ADF4350PCB

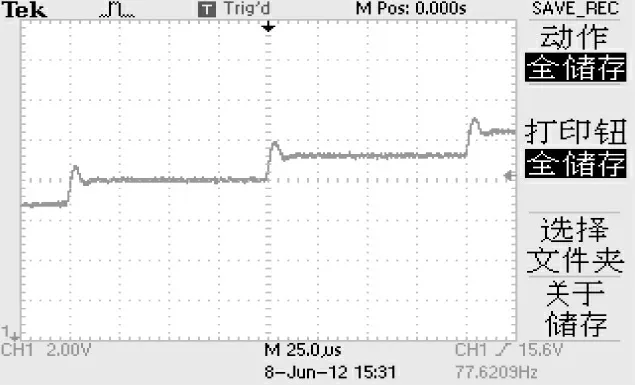

利用示波器測試VCO 壓控端,在100kHz環路帶寬情況下,10倍電壓放大顯示電壓抖動如圖4所示,測定鎖定時間約為12μs。

圖4 VCO 的控制電壓

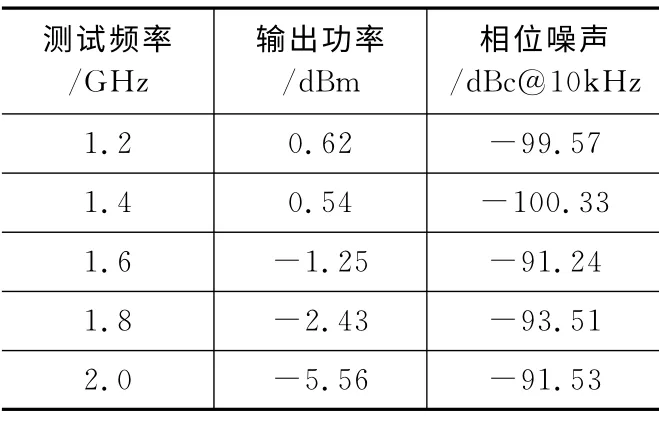

通過R&S公司FSP頻譜分析儀,分別對單頻和步進頻率進行實際測試。單頻點測試通過FPGA 編程配置射頻輸出功率為+1dBm,測試輸出功率與相位噪聲,測試結果如表1所列。

表1 單點頻測試

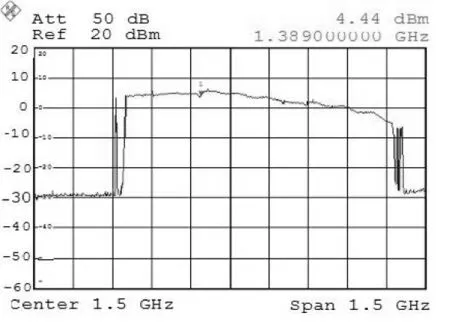

測頻單點頻率輸出為1.5GHz,頻譜分析儀的SPAN寬度為50 MHz,輸出功率為0.22dBm,相位噪聲為-93.83dBc@10kHz,測試結果如圖5所示。

圖5 單頻輸出的頻率和相位噪聲測試

由FPGA 配置,設定每個步進頻點的保持時間為100μs,通過頻譜分析儀,測試寬帶步進頻率的功率值,結果如圖6所示。

圖6 步進頻率輸出頻率譜圖

根據測試結果,本方案設計各項指標基本滿足設計要求。由于傳輸線的衰減和反射作用,導致步進頻率掃描輸出功率不夠平穩。本文設計的寬帶步進頻率源的后級可通過擴展數控衰減器、放大器、選頻濾波器等網絡,將有利于調整輸出功率的平穩度和帶外雜散抑制。

結 語

本方法設計的LS波段寬帶步進頻率信號源結合了DDS和鎖相環芯片二者的優點,在FPGA 的綜合配置、控制下完成了滿足要求的頻率源設計要求。如果將VCO 的基準電壓更新頻率按其16重疊頻段設置,即整個頻率輸出僅更新16次基準電壓,那么在單個VCO 線性區間,輸出頻率的穩定時間將為納秒級,該方法將在后期的設計中重點研究。采用本方法設計的寬帶步進頻率源具有集成度高、頻率穩定性能好、電路簡單、低功耗等特點。同時,該頻率源作為通用電子設備頻率源,可通過FPGA 配置輸出135 MHz~4.4GHz的帶寬輸出,具有廣泛的工程實用價值。

[1]馬宇飛,李署堅,鎖相式頻率合成器的設計與改進[J].電訊技術,2010,50(7).

[2]Analog Devices.Wideband synthesizer with integrated VCO ADF4350datasheet,2008.

[3]劉靜,馬彥恒,胡旭.一種S波段寬帶跳頻頻率合成器的設計與實現[J].計算機測量與控制,2011(6).

[4]Analog Devices.CMOS 125MHz Complete DDS Synthesizer AD9850Datesheet,2004.