FPGA在數據采集與傳輸中的應用

EDA技術是以高級語言描述、系統級仿真和綜合技術為特征的第三代電路CAD技術。在我們研制的數據采集板上使用了該先進技術,采集板主要完成如下功能:A/D轉換、數據緩存、數據傳輸。該板使用一片ALTERA公司的FPGA(Field Programmable Gate Array)芯片FLEX10K,完成了對A/D轉換的控制,數據緩存,以及采集板與計算機的數據異步傳輸(UART)功能。如果用傳統的設計方法完成上述功能至少需要使用MCU(微控制單元)、RAM、RS232的接口芯片等多塊芯片。正是使用了先進的EDA技術使系統更緊湊、更可靠。本文將簡要介紹FPGA的結構,開發方法,以及在我們的采集板中的應用。

1 FLEX10K芯片的結構與工作原理

大部分的FPGA是采用基于SRAM的查找表邏輯形成結構的,用SRAM來形成邏輯函數發生器,我們的數據采集板中的FLEX10K芯片主要由嵌入式陣列塊、邏輯陣列塊、快速通道和I/O單元四部分構成。其中邏輯陣列塊由邏輯單元組成,邏輯單元又是由查找表與附加電路組成。邏輯陣列塊是形成邏輯功能的基礎,多個邏輯陣列塊可以級聯構成更大的單元。快速通道在邏輯單元與I/O單元間起連接作用。嵌入式陣列塊是在輸入、輸出口帶有寄存器的RAM塊,可以提供存儲器的功能。

2 開發系統與語言

我們用的是ALTERA公司的器件,所以開發軟件平臺使用MAXPLUSII,開發硬件平臺使用GW48系統,HDL語言我們選擇了Verilog,verilog語言一般用于硅片邏輯功能設計。

3 FPGA在采集板中的功能劃分

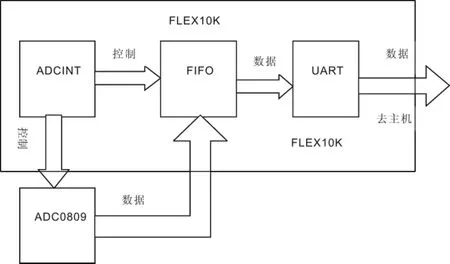

采集板數據采集模塊由A/D轉換芯片ADC0809來實現。我們利用FLEX10K芯片的內部邏輯陣列塊實現數據采集控制器ADCINT;利用其內部的嵌入式陣列塊形成一個先進先出的存儲器FIFO;利用快速通道和I/O單元實現向主機傳送數據的通用異步收發器UART。其系統框圖如圖1:

圖1 采集板系統框圖

4 采集控制器和存儲器功能的實現

4.1 采集控制器的實現

A/D轉換器件ADC0809為單極性輸入,8位轉換逐次逼近A/D轉換器,可對0~5V的INT0~INT7的8路模擬電壓信號分時進行轉換,當時鐘頻率為500 KHz,A/D完成一次轉換的時間為130us。CBA作為8路通道選擇地址,ALE是地址鎖存允許信號,EOC為狀態結束標志,START為轉換啟動信號,上升沿有效;OE為數據輸出允許端,〔D0…D7〕為數據輸出端。

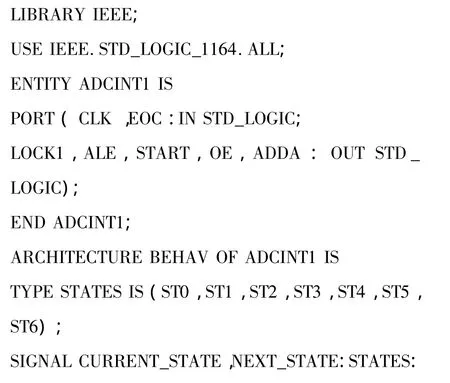

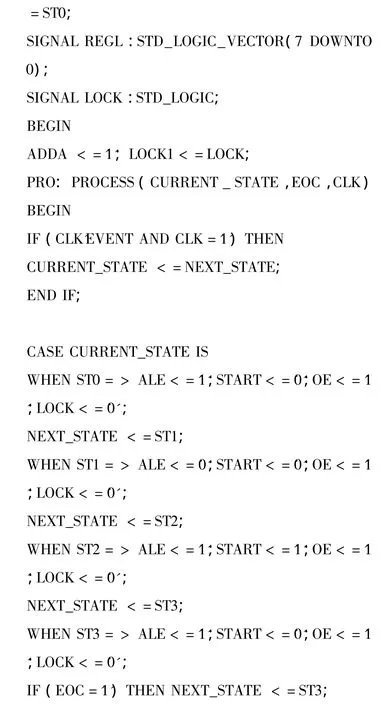

可用硬件描述語言按有限狀態機模式編寫一個模塊實現控制器的定制。其中:ST0初始態,ST1發送地址鎖存信號ALE,ST2發送啟動轉換信號START,ST3檢測轉換結束信號EOC的下降沿,ST4檢測EOC的上升沿,ST5發送輸出使能信號OE,ST6發送輸出鎖存信號LOCK。

控制器的源程序如下:

4.2 FIFO存儲器的實現

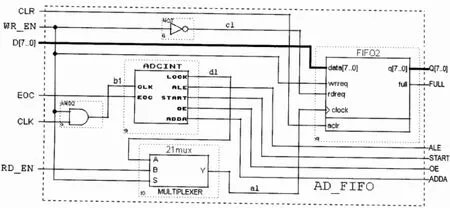

利用FLEX10K內部固有的存儲模塊,通過MAXPLUSII的兆功能塊定制一個帶20字節緩存的FIFO存儲器,因為先入先出存儲器不需要尋址,可以節省時鐘周期,適合動態采集數據.存儲器和控制器組成的控制存儲電路AD_FIFO如下圖2:

圖2 控制存儲電路AD_FIFO電路圖

圖中ADCINT就是采集控制模塊,FIFO2是先進先出存儲模塊。AD_FIFO的工作分兩個階段,即采樣階段和數據讀取階段,在采樣階段WR_EN為高電平,CLK使能,ADCINT開始工作,讀請求被禁止,當某一采樣周期結束,ADCINT發LOCK信號,把出現在D[7.0]的采樣數據存入FIFO2中。

在完成采樣后進入讀取階段,在讀取階段,WR_EN為低電平,FIFO2的讀時鐘CLOCK由RD_EN控制,在每個上升沿,FIFO2的數據將逐一出現在端口Q[7.0]上。

應當注意的是,讀時鐘與采樣時鐘的區別:采樣時鐘是ADCINT的LOCK信號形成的,要與A/D轉換速度匹配;讀時鐘是由外部時鐘發生器的RD_EN形成的,同時讀時鐘應該與后面的數據傳輸的波特率匹配。

5 FPGA中UART功能的集成

UART是基于RS232協議的通用異步收發方式,有免費的軟ip core經過裁剪功能后,再經過MAXPLUSII編譯和綜合到我們的FPGA中。在我們的采集板中的UART只集成了發送器的功能,確定發送方式為:波特率為9600bps;幀格式為,一個起始位、8個數據位、一個停止位。我們用16倍的發送速率做定時信號,還需要做一個16倍波特率發生器。

6 FPGA的整體功能配合和時序分配的問題

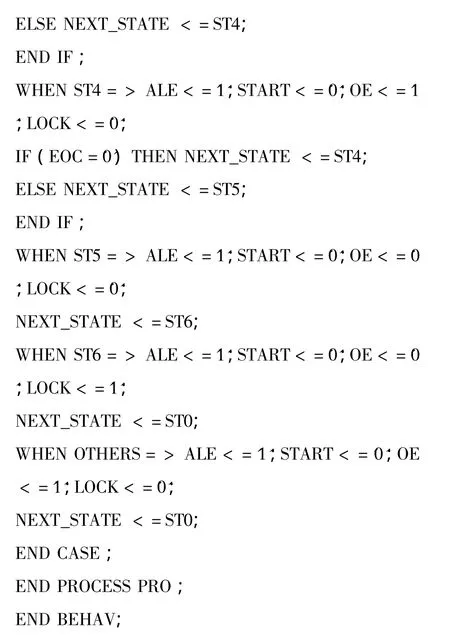

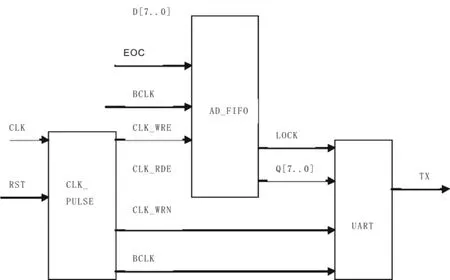

FLEX10K芯片中功能模塊的連接情況如下圖3:

圖3 FLEX10K芯片內功能模塊圖

圖中的CLK_PULSE單元用于為整個系統功能提供時鐘信號,共需4種時鐘信號:CLK_WRE采樣周期,CLK_RDE采樣數據的讀周期,CLK_WRN數據的傳輸周期,BCLK為16倍的波特率。

整個時序配合情況如下:CLK_WRE根據ADC0809的轉換速率130 US和設定的緩存區大小決定的采樣時間;CLK_RDE要根據緩存的數據以及UART的傳輸速率,決定的數據的讀時間;CLK_WRN要根據每幀的位數和發送波特率決定的傳輸時間;BCLK是波特率的16倍。在本系統中時序配合非常重要,它決定了數據傳輸是否能可靠實現,因此我們除了要準確計算各個時鐘周期外,還利用MAXPLUSII的時序仿真功能,分析整個系統功能是否正確。

在時序仿真正確的情況下,在我們的數據采集板上做了實際驗證,實際驗證中發現接受的數據有誤碼。經分析后,發現是在傳輸中沒有考慮芯片延時造成的,經過對時序的仔細調整后,最終解決了傳輸中的誤碼問題。

[1] FLEX 10K Embedded Programmable Logic Device Family[EB/CD] .http://www.altera.com/literature/ds/archives/dsf10k.pdf.January 2003,Ver.4.2.

[2] Donald E.Thomas,Philip R.Moorby.The Verilog Hardware Description Language[M] .Fifth Edition.New York:Kluwer Academic Publishers,2002.