一種數字化中頻接收機的研究與實現

邱冬冬,魯新龍,董 炯,金華松

(中國衛星海上測控部 江蘇 江陰 214431)

軟件無線電(Software Radio)的概念自上世紀末提出以來,最近幾年取得了引人注目的進展。數字化中頻接收機是軟件無線電的重要部分。軟件無線電的主要原理是將數字化推向前端,即是把模數/數模轉換器(ADC/DAC)盡量放在射頻端,這是數字化接收機的發展方向,也是軟件無線電的理想實現方法。早期的數字化接收機受ADC發展水平的限制,采用正交雙通道零中頻的實現方案,即將射頻通過變頻變換到零中頻(基帶),正交解調得到模擬的正交信號之后再進行數字化。該方案的頻率變換主要都在模擬部分實現,數字化較少,不是真正意義上的數字化接收機。而且,此方案實現起來設備量較大,方案中的正交混頻器是模擬器件,得到的正交I,Q信號也難以保證幅相正交的精度[1]。目前比較成熟的數字化接收機理論和實現方案是中頻數字化接收機,即將射頻信號經一次或二次下變頻后,在中頻(或高中頻)直接采樣,再數字下變頻到基帶,得到正交I,Q信號。

軟件無線電技術的迅猛發展,使其在航天測控領域的應用成為了可能。在我國當前的C頻段微波統一測控系統中,中頻接收機主要由模擬電路構成,這種結構已經逐漸不能達到測控系統的精度要求。數字化已經成為中頻接收機的必然發展趨勢,關于這方面的研究,已經開展了很多[2-6]。文中設計了一種數字化中頻接收機,該方案采用軟件無線電思想,并給出了采用FPGA和DSP實現該接收機的方法。

1 系統工作原理

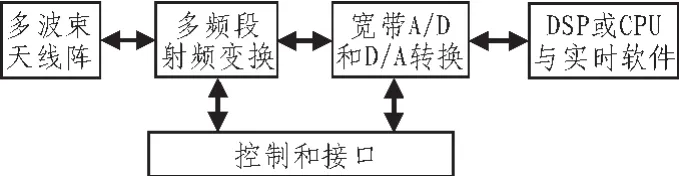

軟件無線電的目標和思路是在標準化、完全可編程的硬件平臺上,用不同的軟件適應通信、測控等業務的各種體制,并實現盡可能多的無線功能,其原理框圖如圖1所示。在理想的軟件無線電中,系統的所有功能都在一個通用的處理器上用軟件實現,原則上允許同一硬件平臺支持任何物理層和更高的協議層。

圖1 軟件無線電的結構框圖Fig.1 Software radio structure diagram

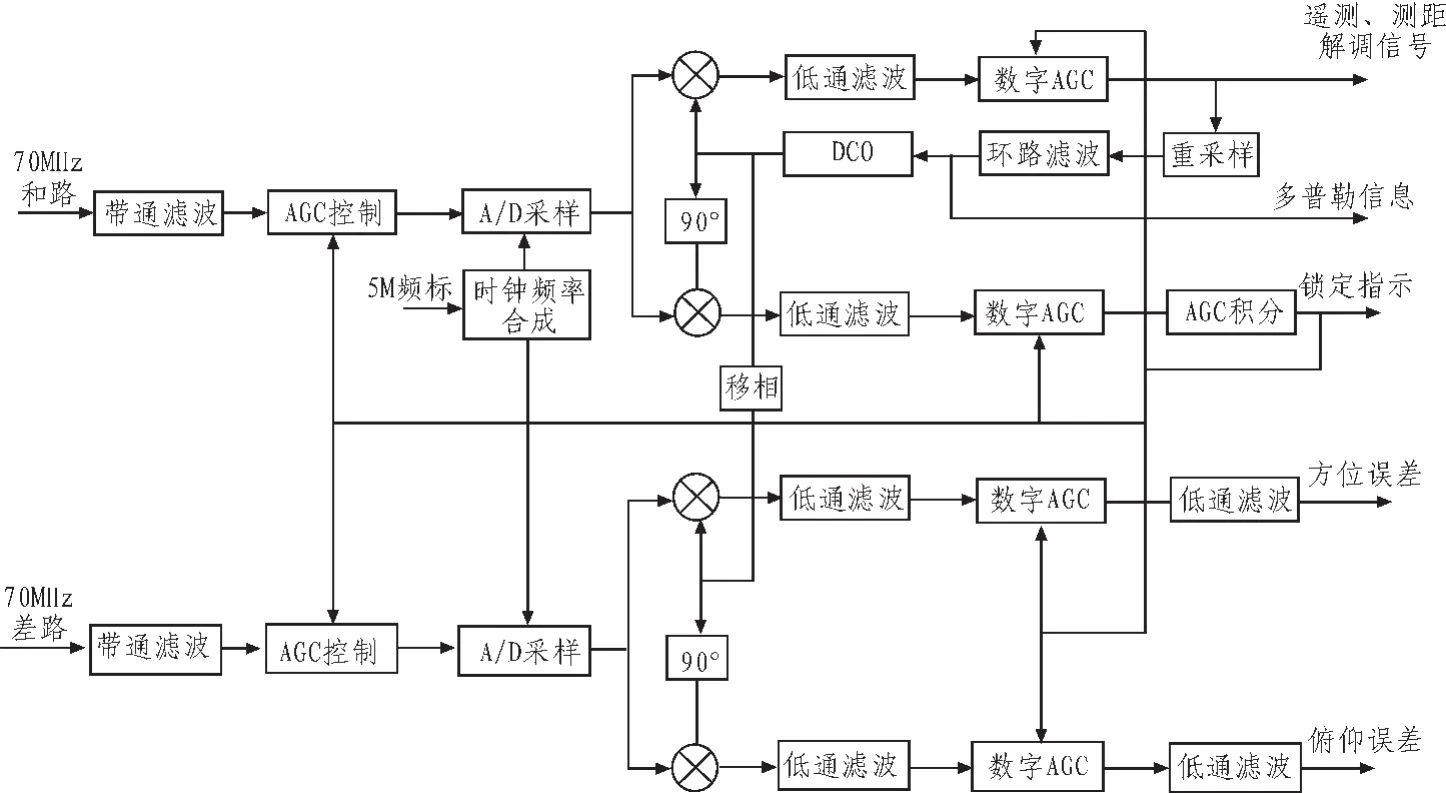

文中所設計的數字化中頻接收機的應用了軟件無線電的設計思路,在中頻70 MHz上進行帶通采樣。輸入的信號有和路和差路,其中和路信號包含有測距、遙測等信息,而差路信號則含有角誤差信息。

圖2 數字化中頻接收機原理框圖Fig.2 Principle diagram of digital intermediate frequency receiver

和路和差路的輸入信號經過濾波和放大后,被A/D采樣變為數字信號,分成I、Q兩條支路,分別完成數字信號的下變頻。其中和路信號分成兩條支路分別解調出遙測、測距信息并完成信號幅度檢測。環路鑒相輸出的誤差信號經數字濾波后控制數字壓控振蕩器(DCO)的頻率和相位完成閉環,并給出多普勒頻率偏移信息。和路信號為移相后的環路DCO輸出后信號,該信號與差路信號進行鑒相檢測出方位和俯仰角誤差信息。移相器與DCO進行一體化設計,實現和路對差路信號幅度的歸一化的AGC控制信號由和路產生。圖2所示的是系統原理框圖。

2 關鍵技術及器件選擇

2.1 ADC的設計

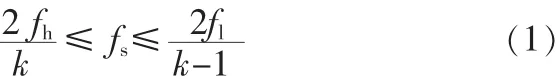

帶通采樣適用于帶通輸入信號,因此將其作為理想的高速中頻采樣方案[7]。

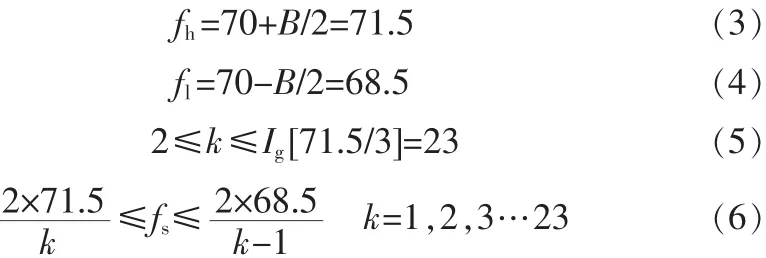

為了保證采樣后不發生頻譜混疊,采樣頻率必須滿足:

其中k取滿足以下條件的整數:

其fs是采樣頻率,fh是信號最高頻率,fl是最低頻率。本方案中,載波中心頻率為70 MHz,信號帶寬為3 MHz。則有:

由以上公式,為了保證采樣變頻輸出各段頻譜不重疊采樣率,fs的可選擇范圍很大。

ADC的性能必須滿足自身和采樣后系統的處理能力,其位數則必須符合一定的動態范圍要求及數字處理部分的精度要求。用于中頻頻段的A/D轉換器件,一般要求動態范圍在 60~80 dB。

ADC選用Analog Devices公司的芯片AD9432。AD9432為單片式12位的芯片,具有精度高、速度高和性能高的優點,內部有采樣保持電路,在整個工作頻率范圍內具有較好的動態性能指標。對于輸入帶寬為25 MHz的信號,它的無雜散動態范圍可達80 dB,一般情況信噪比為67 dB,模擬輸入帶寬能達到300 MHz,其最高采樣速率可達105 MHz,非常適合用來進行中頻采樣。實際應用中,考慮到組合干擾等因素,采樣頻率設定為55 MHz,設為此值可以降低后續濾波器的設計難度。

由于輸入信號動態范圍為-52~8 dBm,最低幅度低于ADC的最小分辨率,所以要加一個放大器。而且考慮到由于電路設計中,還有許多電磁干擾因素,中頻數據采集ADC的有效位數定低于12位,較好的情況下能達到10位~11位,使得實際動態范圍不一定達到60 dBm,因此該放大器還需兼顧一定的AGC功能。這里選用了NS公司的數控放大器CLC5526。

2.2 數字下變頻器的設計

在ADC采樣后,信號的頻率下移到15 MHz附近,還需在鑒相時進行數字下變頻才能完成載波信號的解調。

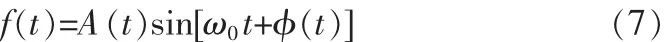

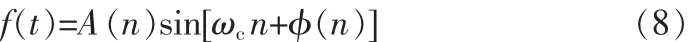

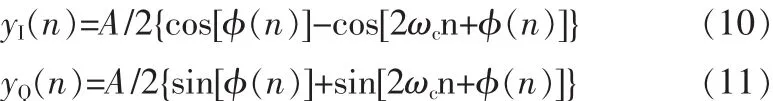

設輸入的中頻模擬信號為:

采樣后的信號為:

式中:

DCO產生的信號為 sin(ωcn),經 90°移相后變為正交信號cos(ωcn),與采樣信號在混頻器相乘后得:

通過低通濾波器濾除其中的倍頻分量后,得到所需的正交 I,Q 信號:

由于信號的采樣頻率較高,即I(n)和Q(n)的速率很高,一般遠大于窄帶信號的帶寬,這時可對其進行速率轉換(抽取),以降低此時的輸出數據率。不過,應當注意的是抽取后的數據率應大于信號帶寬。

DCO的功能是產生頻率可變的正交正、余弦樣本,并作為數字下變頻器的本振信號。輸入的信號與DCO產生的正弦波樣本在數字鑒相器中進行鑒相。由于數字載波中心頻率為15 MHz,所以DCO產生的正弦波樣本信號的基頻應為15 MHz。這樣,鑒相的同時完成了數字下變頻的功能。乘法器輸出的乘積樣本再經過低通濾波器,信號頻譜被搬移到基帶,這樣就完成了載波信號解調。DCO是決定數字下變頻(DDC)性能的主要因素之一。

數字下變頻部分的運算量很大,如果全部由DSP來完成,對DSP需要具有很高的處理速度,比較難以實現[8]。目前,數字下變頻功能的實現方式主要有兩種:一種是使用專門的數字下變頻芯片,如Intersil公司的HSP50214、HSP50216;另一種是采用FPGA,自行設計數字下變頻器。

現場可編程門陣列(FPGA)的主要優點就是其完全可編程性[9]。在設計中需要處理很多信息,為了提高可編程性和系統的集成度,設計中采用了FPGA實現數字下變頻的方案。本文設計的中頻數字接收機,有4路70 MHz的中頻信號輸入。在本文的設計方案中,FPGA選用ALTERA公司APEX系列的EP2A15,其最大門數可達1 900 000門,最高工作頻率可達200 MHz以上,能滿足系統的要求。方案中,不僅4路中頻采樣信號的數字下變頻在FPGA中實現,而且抽取、濾波、以及DCO均集成在FPGA中,FPGA的資源利用率達到了 70%~80%。

3 硬件平臺結構

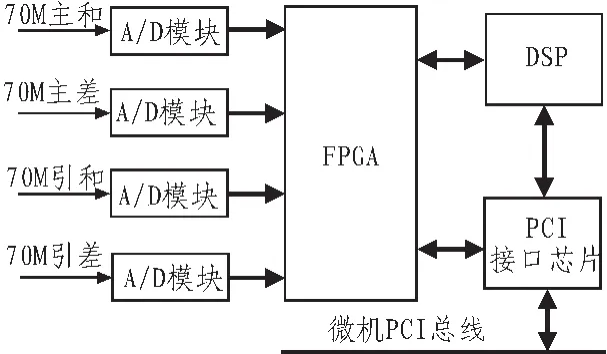

數字處理平臺基于FPGA+DSP的結構來構建,將FPGA的可編程性及高速特性與DSP的復雜運算能力相結合,共同實現數字解調鎖相環,完成載波跟蹤、環路鎖定指示和相關AGC電壓的產生。數據處理平臺與微機CPU進行的數據交換采用PCI總線接口。結構框圖如圖3所示。

圖3 中頻接收機硬件平臺結構圖Fig.3 Intermediate frequency receiver hardware structure chart

這種硬件平臺結構具有通用、標準和模塊化的特點,通過軟件編程來實現接收機的各種功能。同時,設計注重結構的開放性和全面可編程性,通過軟件的更新改變硬件的配置結構,實現新的功能。采用標準的、高性能的開放式總線結構(PCI),有利于硬件模塊的升級和擴展。

4 結束語

鑒于目前硬件水平的限制,直接對射頻信號進行數字化存在困難,只能先將射頻信號下變頻至中頻信號。數字中頻接收機是對中頻信號進行帶通采樣數字化,同時還將信號頻譜向下復制到零頻附近。中頻接收機的數字化是測控系統終端數字化的關鍵。文中設計了一種基于軟件無線電、采用FPGA和DSP架構的中頻數字化接收機實現方案,并分析了其系統工作原理和關鍵技術細節。該方案基于一個標準的硬件平臺,通過不同的加載軟件,該平臺可以演進成適應多種調制方式的中頻接收機,其處理能力可以滿足目前測控系統中絕大部分場合的要求。該平臺現已應用于國內某C頻段統一測控系統中,大大提高了該系統的整體性能。

[1]何勤,束永江.一種通用中頻數字化接收機的實現[J].現代電子技術,2009(11):94-97.

HE Qin,SHU Yong-jiang.Implementation of general IF digital receiver[J].Modern Electronics Technique,2009(11):94-97.

[2]雷兵.雷達數字化借手機設計[J].信息化研究,2010,36(8):54-56.

LEI Bing.Design of the radar digital receiver[J].Informationization Research,2010,36(8):54-56.

[3]汪敏,胡澤,肖斌.基于FPGA的中頻數字化接收機系統實現[J].信息技術,2007(7):113-115

WANG Min,HU Ze,XIAO Bin.Realization of IF digital receiver system based on FPGA[J].Information Technology,2007(7):113-115.

[4]張曉明,陳禾,仲順安.脈沖多普勒小型數字化中頻接收機的設計與實現[J].電視技術,2008,48(11):5-9.

ZHANG Xiao-ming,CHEN He,ZHONG Shun-an.Design and implementation of the miniaturized and digitized IF receiver for a PD radar seeker[J].Telecommunication Engineering,2008,48(11):5-9.

[5]薛繼華.一種中頻數字化接收機中的自動增益控制方案[J].南通紡織職業技術學院學報,2007,7(2):11-14.

XUE Ji-hua.A scheme of auto gain control applied in digital intermediate frequency receiver[J].Journal of Nantong Textile Vocational Technology College,2007,7(2):11-14.

[6]靳鵬飛,楊海濤.中頻數字化接收機系統設計與實現[J].科學技術與工程,2008,8(11):2972-2976.

JIN Peng-fei,YANG Hai-tao.Design and implementation of a digital intermediate frequency receiver[J].Science Technology and Engineering,2008,8(11):2972-2976.

[7]陳禮光,徐福安,張進,等.軟件無線電接收機中頻數字化設計[J].現代電子技術,2004(11):94-97.

CHEN Li-guang,XU Fu-an,Zhang Jin,et al.Design of software radio receivers IF digitalization system[J].Modern Electronics Technique,2004(11):94-97.