并行多通道模擬信號發生器的設計與實現

侯鈺龍,盧一男,張會新

(中北大學儀器科學與動態測試教育部重點實驗室;電子測試技術國家重點實驗室;電子科學與技術系,山西 太原 030051)

近年來,隨著航空航天工業的飛速發展,針對通信、雷達、宇航、遙感遙測等方向的測試任務也變得日益復雜。單一的測試任務已不再是對單一信號的測試,而轉變為對形式多樣、數量龐大的信號群的測試。以往,要完成如此復雜的測試任務,需要眾多的測試設備,消耗龐大的人力物力和許多寶貴的時間。隨著測試的精確性更高,就要求信號源提供高精度的模擬信號,對輸出信號頻率的精確度、穩定度、分辨力都有了更高的要求。在這種情況下,設計出一種高效、多功能、高精度的信號發生器就成為迫切的需要。本設計實現的信號發生器可以并行產生多達80路的模擬信號,并且根據需求,可方便地進行擴展。采用本設計方法可以輸出直流量、方波、正弦波等多種波形,頻率范圍0~100 kHz,頻率分辨力為0.1 Hz,幅值范圍±5 V。

1 設計原理及依據

本文介紹的模擬信號發生器依據并行測試(Parallel Test)的思想結合直接數字頻率合成技術(Direct Digital Synthesizer)而設計。并行測試意指測試系統在同一時間段內完成多項測試任務,包括對單個被測對象(Unit Under Test,UUT)的多項參數進行測量或對多個被測對象的多項參數進行測量。能夠同時輸出80路模擬量測試波形,并且最大可擴展至512路模擬量輸出,使得測試效率相比以往大大提高。直接數字頻率合成技術(DDS)是由美國學者Tiemey J,Rader C M和Gold B等人于70年代首次提出,經過幾十年特別是近年來數字集成電路及微電子技術的發展,目前已經在電子儀器領域得到廣泛應用[1]。

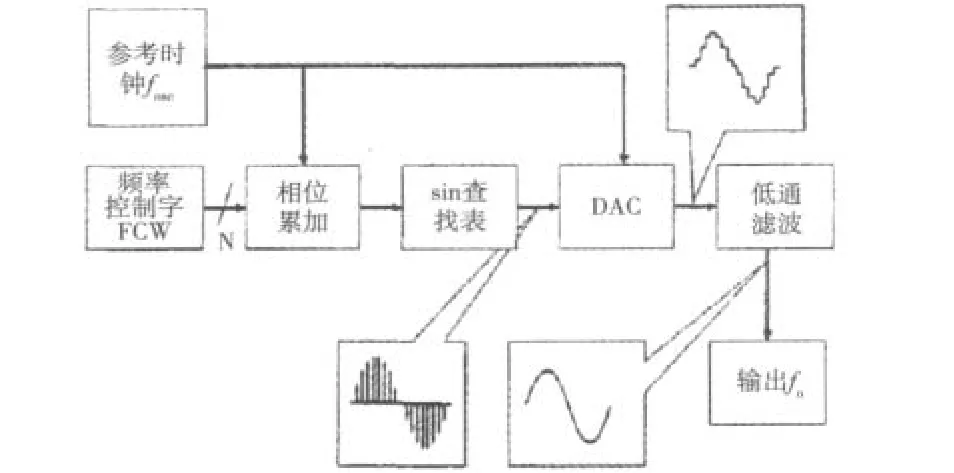

DDS技術的理論依據是時域采樣定理,將一個階梯化的數字信號,通過低通濾波器還原為平滑連續的模擬信號。階梯化的數字信號一般采用單片機或其他控制芯片控制D/A芯片產生,后級則通過運放放大至所需的幅值。首先,主控芯片需要將輸出波形進行DDS量化,簡單說也就是找出不同相位所對應的幅度值,并且將這些量化好的幅度值存儲在一個查找表(ROM)中。然后,主控芯片選取適當的頻率控制字通過相位累加進行尋址,從查找表中讀出對應的幅值,控制D/A芯片產生階梯化信號[2]。DDS基本原理框圖如圖1所示。

圖中輸出波形頻率與參考時鐘頻率的關系表達式為

圖1 DDS基本原理框圖

式中:fo為輸出頻率,fosc為參考時鐘頻率,FCW為頻率控制字,n為相位累加器的位數。從式(1)可以看出,只需給定參考時鐘及頻率控制字,即可得到某一對應的頻率信號。當FCW=1時,即可得到DDS所能產生的最低頻率信號,fo=fosc/2n即頻率分辨力,當n越大,則得到的頻率分辨力越高。本設計采用40 MHz晶振,32位累加器,頻率分辨力可達到0.01 Hz,滿足設計要求[3]。

2 設計方案

2.1 整體方案設計

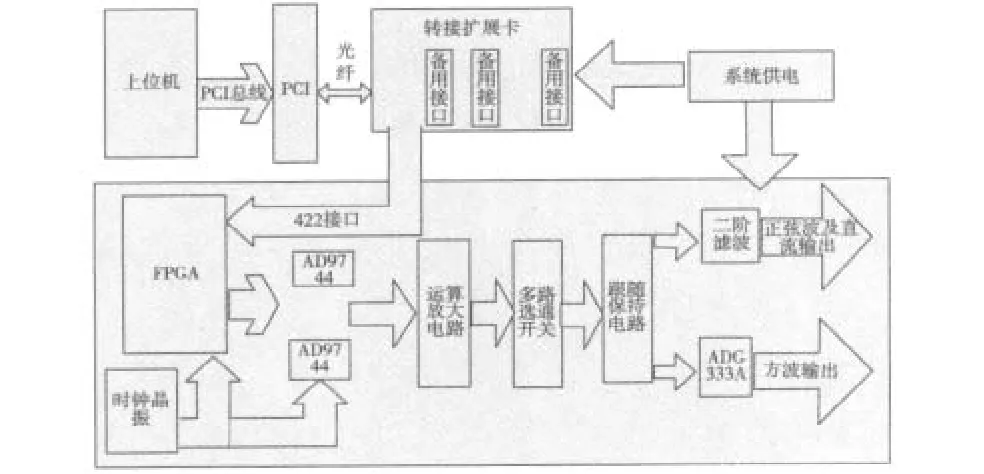

基于DDS的信號源有多種設計方法,需要根據不同的需求進行適當的選擇。一般來說,輸出信號頻率較高,輸出路數較少時,可以考慮選用如 AD9851,AD9852,AD9957等由ADI公司生產的專用集成DDS芯片,其優點為:通常芯片內部集成了混頻、調制、轉換、濾波等功能,大大降低了設計難度,提高了輸出性能,減少了電路面積。但其缺點為:輸出路數較少,且芯片價格高昂,無法滿足多路并行測試的需要。考慮到本設計的特殊要求,采用Xilinx公司生產的xc3s400 FPGA作為主控芯片,利用FPGA并行處理能力,多輸出管腳的優點結合選通開關進行多路切換,實現多路并行輸出。采用AD9744作為D/A轉換芯片,實現轉換精度14位,125 Msample/s轉換速率。后級通過AD818進行放大,AD818可采用雙15 V供電,軌到軌輸出,保證了較寬范圍內的輸出幅度。放大后的信號經過多路選通開關進行切換,再經過跟隨,濾波后輸出。系統總體框圖如圖2所示。

圖2 系統設計框圖

此次設計在以往設計的基礎上增加了轉接擴展卡,擴展卡上提供16個卡槽,最多可掛接16塊模擬量輸出板卡,每塊板卡集成32路輸出,使得信號源最多可實現512路并行模擬量輸出。

2.2 輸出信號的實現

本設計中從FPGA產生原始數據到最終信號產生,大致經過了D/A轉換、放大、通道切換、跟隨、濾波等多個環節,根據產生不同波形的需要,經過的環節也不相同。正弦波需要波形圓潤平滑,所以在濾波時,需要濾除掉高頻分量,采用二階低通濾波器,經過試驗,當正弦波頻率<100 kHz時使用兩個1 nF電容有較佳的濾波效果。產生方波時則需要保留高頻分量以使得波形更陡峭,采用ADG333A單刀雙擲開關通過高低電平的來回切換以實現方波的高低電平變換。實驗發現,這種切換的方式會產生過沖及震蕩,因此在輸出級加入適當的電阻及電容以改變電路的阻尼特性,使得電路阻尼系數達到臨界狀態,從而消除過沖及震蕩。直流量輸出雖然控制方式簡單,但是對信號精度要求極高,本次設計要求達到0.1%的精度,經過分析,直流輸出的精度主要受限制于電源的紋波及器件差異造成的幅度偏移,其中幅度偏移可通過標定解決,而針對電源紋波,該設計采用了線性電源,以使得紋波控制在10 mV以內。

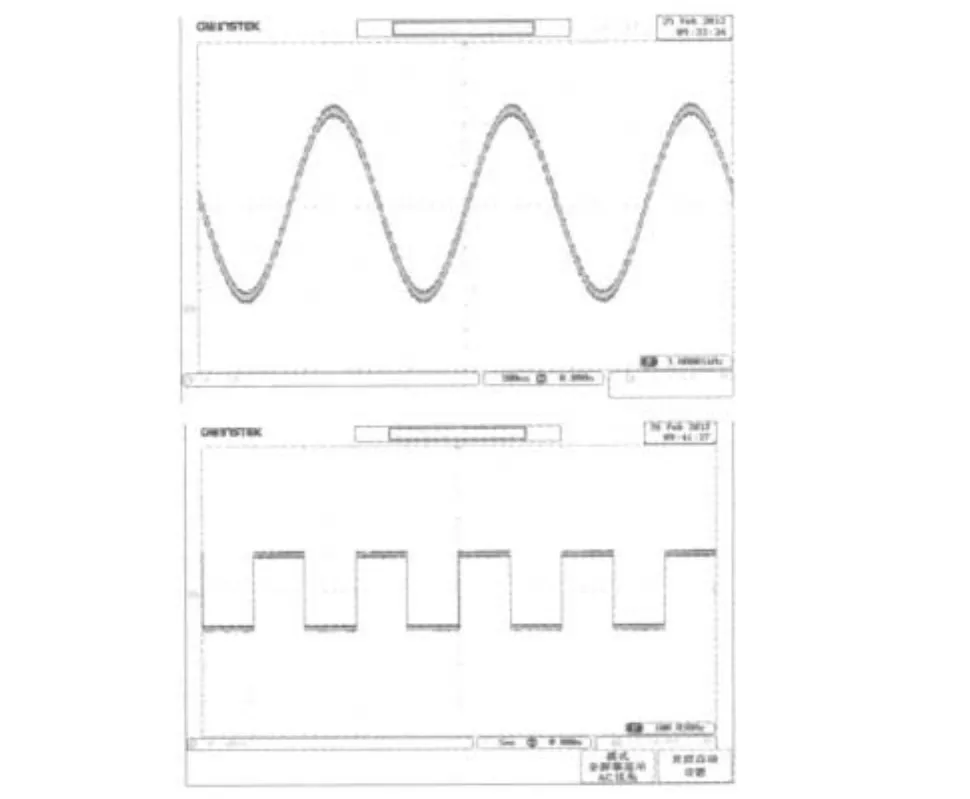

設計采用通道切換產生多路輸出,因此存在通道切換時間與運放壓擺速率的協調問題,本設計采用的AD818壓擺率為500 V/μs,切換時間應按照相鄰兩路最大幅值差計算,實際設計中,模擬量電壓輸出范圍為±5 V,因而通道保持時間必須大于20 ns,否則產生通道干擾[4]。在跟隨保持環節,實際是電容的充放電過程,充電時間與放電時間決定了切換時間的范圍,實際設計中必須保證通道切換時間在此范圍之內。信號源產生的正弦及方波波形如圖3所示。

圖3 測試波形(截圖)

3 結束語

本設計已在實際項目中交付,并且較好地完成了測試任務。在實際測試中也存在一些不完美之處,比較突出的一點是,長時間輸出致使運放發熱的問題沒有得到較好的解決,熱噪聲會導致一定程度的溫漂,采用了抗溫漂性能較好的阻容器件,使得誤差仍在可接受的范圍內。

[1]HOU Yulong.The design and realization of multi-channel parallel testing system based on FPGA[C]//Proc.MACE 2011.[S.l.]:IEEE Press,2011:787-790.

[2]雷國偉,林興元,舒強.基于DSP Builder的通用調制信號發生器設計[J]. 電視技術,2009,33(2):18-19.

[3]王建明.基于DDS技術的多波形信號源設計[D].南京:南京理工大學,2005.

[4]趙呈愷.通用測試臺模擬信號源的設計[D].太原:中北大學,2009.