軟硬件聯(lián)合仿真平臺的設(shè)計

廈門大學(xué)信息科學(xué)與技術(shù)學(xué)院 奎 偉

1.前言

在做FPGA設(shè)計時,軟件仿真這個步驟是必不可少的。仿真工具如Modelsim在每一個仿真時鐘片上會依次計算電路中每一個寄存器的值,完成之后再進(jìn)入下一個仿真時鐘片。由于CPU的運(yùn)算是串行的,當(dāng)仿真時間較長,或者電路結(jié)構(gòu)很復(fù)雜時,軟件仿真就會變成一件很耗時的事情。

假設(shè)仿真的最小時鐘片是1ps,那仿真1s的時間長度需要進(jìn)行1萬億次時間片的計算,每個時間片內(nèi)的所需要的計算時間是由電路中寄存器的個數(shù)來決定的。如果目標(biāo)電路是一個簡單的加法器,這樣的仿真過程僅需要不到1秒的時間;但是當(dāng)目標(biāo)電路換成一個1O萬門以上的系統(tǒng)之后,所需要的仿真時間就會變得難以忍受。

軟硬件聯(lián)合仿真的概念早在HDL語言建立之初實際上就已經(jīng)提出來。HDL的標(biāo)準(zhǔn)里有很大一部分描述了HDL語言與其他高級編程語言的接口規(guī)范,verilog對應(yīng)的接口規(guī)范叫做PLI(Programmable Language Interface)[1],這個接口允許在仿真層次上verilog與C語言進(jìn)行互動。有這個編程接口之后,HDL仿真就變得十分靈活,它可以借助于C語言實現(xiàn)的驅(qū)動程序與各種硬件設(shè)備進(jìn)行交互,這就提供了一種可靠的軟硬件聯(lián)合仿真的技術(shù)基礎(chǔ)。文獻(xiàn)[2]給出了聯(lián)合仿真的統(tǒng)一模型,文獻(xiàn)[3-5]提出了不同的硬件加速設(shè)計方案。本文基于上述研究,提出一種使用USB2.O接口作為數(shù)據(jù)傳輸通道的軟硬件聯(lián)合仿真平臺實現(xiàn)方式。

2.軟硬件聯(lián)合仿真平臺設(shè)計

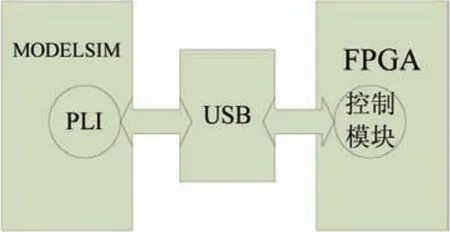

軟硬件聯(lián)合仿真的大體思路是:將一個系統(tǒng)拆分成為兩部分,待驗證模塊和其他部分。將需要重點關(guān)注的待驗證模塊放在仿真工具上仿真,然后將其他部分直接燒入FPGA芯片里,通過外設(shè)接口(PCI-E、USB等)實現(xiàn)FPGA芯片和電腦的數(shù)據(jù)交互。為了保證仿真結(jié)果的可靠性,燒入FPGA芯片內(nèi)的模塊必須是驗證后可靠的。

一個大系統(tǒng)的設(shè)計往往會經(jīng)過從算法仿真到硬件描述語言仿真再到FPGA實現(xiàn)的過程,逐步的由軟件框架變?yōu)橛布O(shè)計。借助于軟硬件聯(lián)合仿真的方法,就可以將一個系統(tǒng)分塊由軟件變?yōu)橛布⑶夷軌蛟谠O(shè)計過程中很方便的驗證設(shè)計的正確性和可靠性,將出錯的風(fēng)險分散在整個設(shè)計流程內(nèi),降低最后除錯的復(fù)雜性。

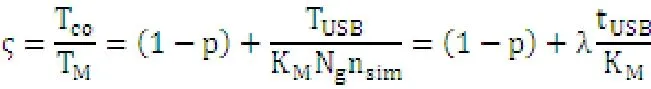

本設(shè)計實現(xiàn)了Modelsim與FPGA開發(fā)板的通信,傳輸接口采用USB2.O。USB2.O數(shù)據(jù)傳輸速率最高可以達(dá)到48OMbps,平均傳輸速率大概是3MB/s,可以滿足仿真過程中大量測試數(shù)據(jù)的傳輸。

聯(lián)合仿真需要解決的問題主要有,軟硬件通信方式的設(shè)計以及軟件時鐘和硬件時鐘的同步。本設(shè)計中采用軟件生成時鐘,驅(qū)動硬件產(chǎn)生時鐘邊沿脈沖信號,來控制硬件運(yùn)行速度,保證軟硬件運(yùn)行速度的一致性。

2.1 系統(tǒng)框架

整個軟硬件聯(lián)合仿真平臺的設(shè)計主要分為三個部分:Modelsim端的接口程序設(shè)計、USB驅(qū)動在PC上和FPGA上的實現(xiàn)、FPGA端接口控制電路的設(shè)計。

Modelsim端需要實現(xiàn)的功能有:時鐘信號的生成,測試文件的實現(xiàn)以及實現(xiàn)USB通信的軟件設(shè)計。這個部分是整個系統(tǒng)的驅(qū)動部分,所有對仿真過程的控制都在Modelsim上實現(xiàn),同時也是系統(tǒng)人機(jī)交互的接口。這一部分需要實現(xiàn)對硬件的透明化設(shè)計,即用戶只需要修改測試文件就能控制整個仿真的流程,與純軟件的仿真過程沒有太大差異。

USB的驅(qū)動部分分為PC端和FPGA端。PC端的驅(qū)動采用windriver自動生成底層接口函數(shù),然后再在這個基礎(chǔ)上編寫通信控制程序以及PLI的調(diào)用,實現(xiàn)Modelsim通過USB接口進(jìn)行收發(fā)數(shù)據(jù)的功能。FPGA端采用了一塊通用USB控制芯片cy7c68O13,直接連接到FPGA上。然后在對該芯片進(jìn)行操作,實現(xiàn)FPGA通過USB接口進(jìn)行收發(fā)數(shù)據(jù)。

FPGA端接口控制電路的設(shè)計所實現(xiàn)的功能包括:時鐘信號的生成與驅(qū)動,仿真數(shù)據(jù)的收集功能,通信幀的組成與解幀。其中重點就是需要完成與軟件時鐘的同步以及數(shù)據(jù)搜集邏輯的實現(xiàn)。

2.2 系統(tǒng)性能分析

軟硬件聯(lián)合仿真平臺的設(shè)計目標(biāo)是為了加快仿真速度,縮短系統(tǒng)的設(shè)計周期和設(shè)計復(fù)雜度。我們會從時間性能上來分析使用軟硬件聯(lián)合仿真的方法帶來的好處。

Modelsim的仿真過程是分仿真時間片進(jìn)行的。每個仿真時間片內(nèi),Modelsim按照數(shù)據(jù)路徑依次對系統(tǒng)中所有門電路和基本邏輯單元的輸出進(jìn)行計算。因此Modelsim每個時間片的仿真時間與系統(tǒng)綜合后占用的門數(shù)成正相關(guān)。

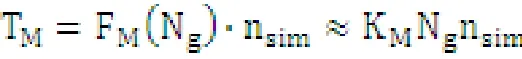

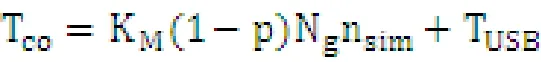

設(shè)仿真時間TM與系統(tǒng)所占用的邏輯門數(shù)Ng之間的關(guān)系為:

若采用軟硬件聯(lián)合仿真的方式,將該系統(tǒng)的一部分放入FPGA內(nèi)運(yùn)行,則可以計算出聯(lián)合仿真模式下所需要的仿真時間。

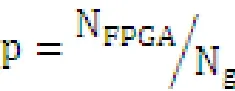

對待測系統(tǒng)進(jìn)行分割之后,設(shè)需要放入FPGA的部分所占用的邏輯資源比例為p:

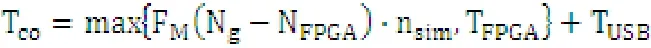

采用軟硬件聯(lián)合仿真后,所需要的仿真時間分為兩個部分:運(yùn)算和數(shù)據(jù)傳輸,計算公式如下所示:

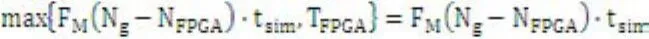

上式中,TFPGA表示FPGA內(nèi)部計算時間,包括成幀解幀邏輯和系統(tǒng)一個時鐘周期的運(yùn)行時間,而這個時間不會超過微秒數(shù)量級,所以通常情況下,

上式可以化簡為:

由系統(tǒng)加速比的公式可以看出,軟硬件聯(lián)合仿真所帶來的加速收益是與軟硬件劃分程度p和系統(tǒng)復(fù)雜度Ng成正比。而USB傳輸所需的時間又可分為設(shè)備初始化時間和傳輸時間,由于這是一個高速的串行接口,因此對于絕大多數(shù)待測系統(tǒng)來說,tUSB可以看作是一個固定不變的值(即不隨系統(tǒng)的復(fù)雜度而改變)。因此,當(dāng)系統(tǒng)越復(fù)雜時,采用軟硬件聯(lián)合仿真可以得到更好的仿真加速性能。

3.仿真平臺的實現(xiàn)

3.1 PC端設(shè)計

PC端實現(xiàn)的功能是:1.產(chǎn)生測試用信號;2.實現(xiàn)USB接口驅(qū)動,完成與FPGA的通信;3.利用PLI的接口在Modelsim的波形窗口中顯示需要關(guān)注的信號。

如圖2所示,待測系統(tǒng)被分為軟件和硬件兩個部分。同樣,我們所設(shè)計的接口也分為軟件和硬件部分,PC端實現(xiàn)的就是仿真平臺接口的軟件部分。

PLI全稱為Programmable Language Interface,是在1985年就公布的Verilog HDL語言與c語言的編程接口。通過PLI接口,Verilog HDL語言的仿真器變得更為靈活,可以完成幾乎任何能夠想到的任務(wù),包括圖形交互工具、文件讀寫、以及本設(shè)計中所用到的硬件驅(qū)動。

定義系統(tǒng)任務(wù)$getData,實現(xiàn)PC端對數(shù)據(jù)的讀取操作。該系統(tǒng)在時鐘信號發(fā)生變化時做出響應(yīng),首先會判斷時鐘上升沿和復(fù)位、使能信號是否有效。當(dāng)條件都滿足時,$getData讀入標(biāo)準(zhǔn)化后的輸出端口信號值,將其打包組成通信幀,之后再調(diào)用USB驅(qū)動程序?qū)?shù)據(jù)發(fā)送出去,并且讀入來自FPGA的輸入端口信號值,解幀后驅(qū)動到Verilog HDL的端口上,實現(xiàn)PC與FPGA的通信。

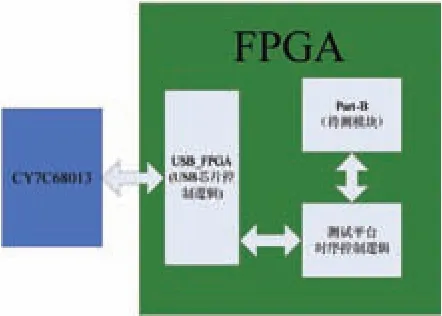

圖1 系統(tǒng)設(shè)計框圖

圖2 系統(tǒng)軟硬劃分示意圖

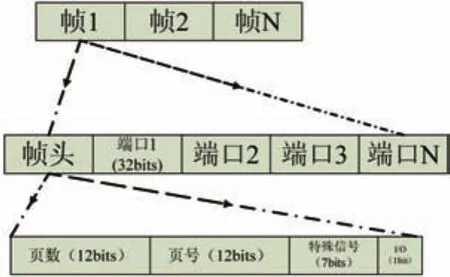

圖3 通信幀結(jié)構(gòu)

圖4 FPGA端結(jié)構(gòu)圖

圖5 待測模塊的時鐘生成邏輯

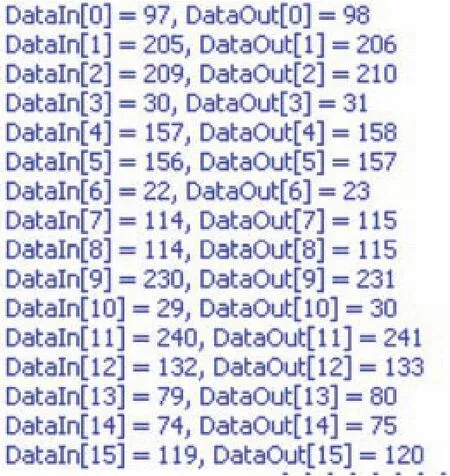

圖6 加法器的軟硬件聯(lián)合仿真結(jié)果

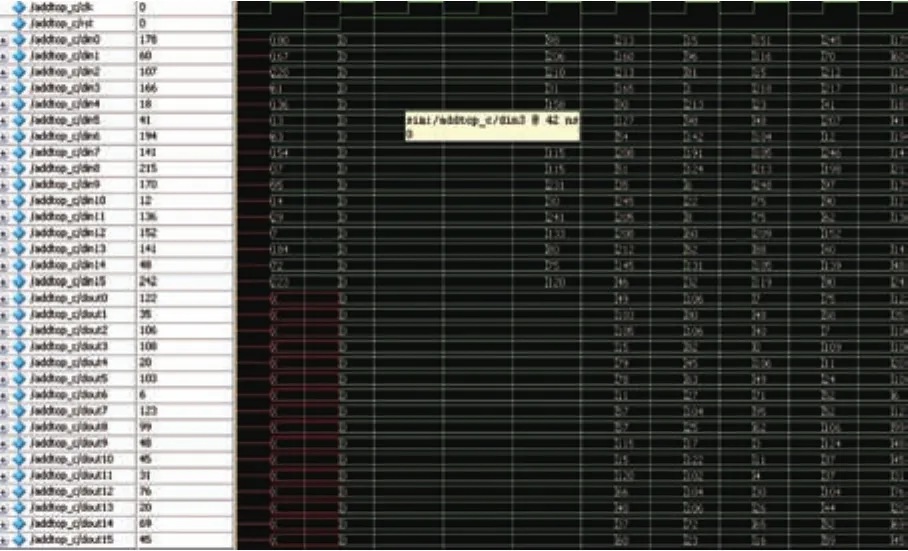

圖7 加法器的軟硬件聯(lián)合仿真波形圖

3.2 通信幀設(shè)計

對于不同的待測系統(tǒng),所需要傳輸?shù)男盘枖?shù)量也各不相同。為了保持通用性,我們在軟硬件仿真平臺的USB通信部分設(shè)計了數(shù)據(jù)幀格式,使得程序可以自主的完成傳輸過程,而不需要對每一個待測系統(tǒng)再進(jìn)行單獨的配置。

通信幀的結(jié)構(gòu)如圖3所示。幀長度設(shè)計為32(N+1)bits,其中N代表每一幀包含的32位端口個數(shù)。一個完整的通信幀由1個記錄傳輸信息的幀頭和N個記錄數(shù)據(jù)的幀體所組成。當(dāng)N=7時,每個通信幀的傳輸容量為256位,其中可以傳輸224位信號線的數(shù)據(jù)。

幀頭的32位數(shù)據(jù)定義如下:頁數(shù)12位,表示當(dāng)前通信過程總共需要的通信幀的個數(shù),最多可以支持到4O95個幀,28665x32位的數(shù)據(jù)傳輸。頁號12位,表示當(dāng)前幀在整個通信過程中的序號,用來避免順序出錯以及做通信結(jié)束判斷標(biāo)志。特殊信號7位,每一位代表一種特殊信號,比如時鐘、復(fù)位、使能信號等控制信號。傳輸方向標(biāo)志(I/O)1位,表示當(dāng)前通信幀是由FPGA傳向PC還是反向。

作為數(shù)據(jù)空間,第一幀的第二個子幀(即數(shù)據(jù)域端口1)的32位被用來以無符號整數(shù)的形式傳輸port_in(或port_out)端口的個數(shù),因此有效的總數(shù)據(jù)量會減少32位。

3.3 FPGA端設(shè)計

FPGA端完成的工作包括USB芯片的時序控制電路,以及聯(lián)合仿真的時鐘數(shù)據(jù)控制電路,共分為兩個獨立的模塊實現(xiàn),分別是USB_FPGA和enFrame。前者實現(xiàn)的是對USB接口進(jìn)行32位數(shù)據(jù)的讀寫操作,后者實現(xiàn)將USB端口傳入的數(shù)據(jù)正確的配置到待測模塊Part-B上,并控制Part-B進(jìn)行單時鐘脈沖運(yùn)行(單步運(yùn)行),使得FPGA的運(yùn)行速度與PC端Modelsim的仿真速度相匹配。

與軟件端對應(yīng),enFrame也采用自動代碼生成器生成與Part-B的連線邏輯,并且內(nèi)部實現(xiàn)了將PC端傳來的通信幀解幀,剝離出數(shù)據(jù)信號,配置到Part-B的輸入端口;同時,enFrame也在每一個仿真時鐘周期對Part-B的輸出信號采樣,成幀后由USB接口發(fā)送至仿真平臺的軟件端。

這個過程有一個難點在于,如何實現(xiàn)FPGA上系統(tǒng)的單步運(yùn)行。我們采用的方法是,將Part-B的時鐘信號單獨剝離出來,由測試平臺提供的單脈沖上升沿信號作為Part-B的時鐘輸入。如圖5所示,利用使能信號ENB和晶振產(chǎn)生的方波信號,可以實現(xiàn)易于控制的單脈沖時鐘信號。當(dāng)enFrame將所有數(shù)據(jù)信號配置在Part-B的輸入端之后,激活使能信號ENB,在一個時鐘周期之后立刻禁用ENB,這樣,圖5所示電路的輸出就只有單個上升沿/下降沿,達(dá)到預(yù)先的目的。

4.測試實例

通過USB接口,對FPGA發(fā)送測試數(shù)據(jù)。將FPGA數(shù)據(jù)處理后的結(jié)果采集并發(fā)送給Modelsim中的shift.v模塊。如圖6,DataIn是通過USB發(fā)送給FPGA上加法器的測試數(shù)據(jù),DataOut是經(jīng)FPGA加法后返回的數(shù)據(jù),可見結(jié)果是正確的。如圖7,是將DataOut發(fā)送給Modelsim,由shift.v模塊中的din接收,dout為經(jīng)過移位后的結(jié)果。如圖6:DataIn[O]傳入FPGA數(shù)據(jù)為97,經(jīng)加法后為DataOut[O]=98,發(fā)送給shift.v的dinO為98,經(jīng)右移后結(jié)果為doutO為49。結(jié)果完全正確。從而驗證了硬件仿真加速的想法。同樣,亦可在FPGA中運(yùn)行更為復(fù)雜的系統(tǒng),UUT模塊選擇為H.264,方法亦是相同的。

5.結(jié)論

本文實現(xiàn)了PC與FPGA的聯(lián)合仿真平臺設(shè)計,并從理論上證明了該仿真平臺能夠達(dá)到的加速性能。軟硬件聯(lián)合仿真平臺共分為3個部分,分別是電腦上的用戶軟件接口,數(shù)據(jù)通信協(xié)議和FPGA內(nèi)的控制模塊,電腦與FPGA平臺使用USB接口連接。本文使用加法器作為測試樣例證明了該結(jié)構(gòu)的可行性。與純軟件仿真的FPGA設(shè)計方法相比,在設(shè)計過程中使用聯(lián)合仿真方案可以極大降低設(shè)計風(fēng)險,縮短設(shè)計周期。

[1]“IEEE Standard Verilog Hardware Description Language”,New York,September 2001.

[2]Valderrama,C.,A.Changuel,et al.“A unified model for co-simulation and co-synthesis of mixed hardware/software systems”,Proceedings of European design and test conference,1995.

[3]Ruelland,R.,Gateau,G.,Meynard,T.A.,Hapiot,J.-C,“Design of FPGA-based emulator for series multicell converters using cosimulation tools”,IEEE Transactions on Power Electronics,January 2003.

[4]Jingzhao Ou,Prasanna,V.K.,“MATLAB/Simulink based hardware/software cosimulation for designing Using FPGA configured soft processors”,Proceeding of parallel and distributed processing symposium,2005.

[5]A.Hoffman,T.Kogel,H.Meyr,“A framework for fast hardware-software co-simulation”,Pro-ceeding of the conference on design,utomation and test in Europe,2001.