基于FPGA 的S 模式信號處理

黃曉卿

(中國西南電子技術研究所, 成都610036)

1 引 言

S 模式是一種用于空中交通管制(ATC)的協同式監視數據鏈,提供了更高的監視精度、性能和效率。隨著S 模式在空中交通管制、敵我識別系統(IFF)、機載防撞系統(TCAS/ACAS)、自動廣播相關監視(ADS-B)等系統中的越來越廣泛應用,對于S模式信號處理終端的信號數據處理能力提出了更高的要求。

S 模式詢問/應答機除了兼容處理A/C 模式信號外,還需要準確快速地完成S 模式的全呼、監視和廣播等信號的處理。S 模式提供了25 種詢問和應答格式,在ICAO 附件10 中對大部分的信號格式進行了規定, 其報文格式分短型(56 bit)和長型(112 bit)兩種。S 模式詢問/應答機在實現大量數據通信處理的同時,如何能更高效準確快速地完成對其信號處理終端提出了更高要求。

本文著重介紹了S 模式信號處理的硬件設計,針對S 模式詢問/應答信號長、攜帶數據信息量大、干擾脈沖多等特點, 將傳統由數據處理器(DSP)完成主要的數據處理設計通過硬件電路現場可編程門陣列(FPGA)實現,充分利用FPGA 的并行高速處理能力,提高S 模式信號處理終端的性能。

2 S 模式信號處理

2.1 信號處理終端組成

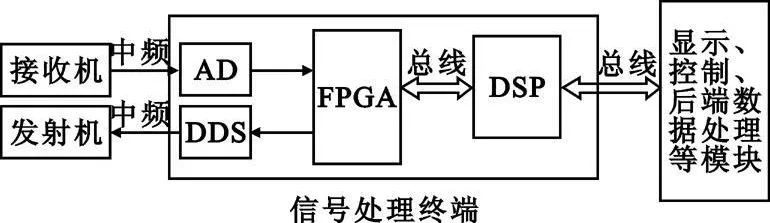

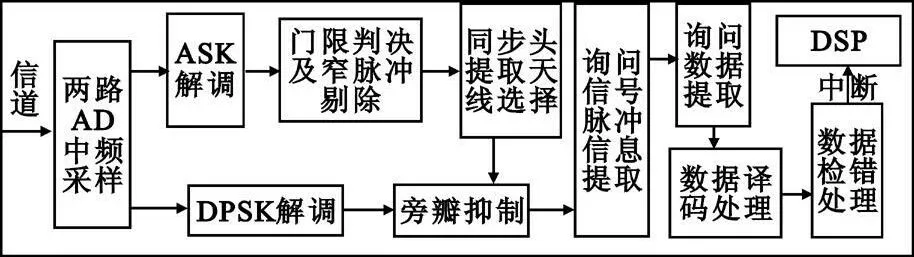

S 模式信號處理終端是詢問/應答機信號數據處理的核心部分,詢問機信號處理終端主要完成對詢問信號的編碼和對應答信號的解碼處理功能,應答機信號處理終端主要完成對詢問信號的解碼和產生應答信號。信號處理終端組成框圖如圖1 所示,硬件電路主要由DSP+FPGA+AD+DDS 等器件組成,器件AD 主要實現對中頻信號的數據采樣(模擬信號轉換成數字信號);FPGA 主要完成信號數據處理,包括數據編碼、調制、解調、解碼、檢錯和糾錯等,具體實現過程見2.3 ~2.6 節,對于詢問應答信號的調制解調過程和對應答信號數據的糾錯處理這里就不詳細介紹;DSP 主要實現與外部設備的數據通信功能(詢問機參數、應答機參數和部分數據處理等);DDS 主要完成將數字信號轉換成模擬信號。充分利用FPGA 性能好、資源豐富、并行處理能力強以及開發環境優越等特點,將主要的信號處理、數據處理、編解碼等功能通過FPGA 來實現完成。

圖1 信號處理終端組成框圖Fig.1 Block diagram of the Mode S signal processor

2.2 S 模式詢問信號格式

S 模式詢問信號和應答信號格式[1]如圖2 所示。

S 模式詢問信號脈沖的P1、P2為前導同步脈沖,P5為旁瓣抑制脈沖,采用脈沖幅度調制(ASK),脈沖寬度為0.8 μs,脈沖間隔為2 μs。數據塊脈沖為P6,寬度為16.25μs或30.25 μs,采用的是差分相移鍵控調制(DPSK),調制速率為4 Mbit/s,包含56 bit或112 bit的信息。最后24 bit數據是詢問信息(前3 2bit或88 bit)的循環校驗碼與飛機地址碼和多項式相乘結果的異或數據。

S 模式應答信號由前導同步脈沖和56 bit 或112 bit的數據塊組成,前導同步采用脈沖幅度調制(ASK),數據采用脈沖位置調制(BPPM)。前導脈沖共由4 個脈沖組成,脈沖寬度為0.5 μs。前導脈沖用于S 模式應答引導脈沖。數據塊每1 μs的時間間隔對應于信息的一個比特。前0.5 μs有脈沖,則信息為“1”;后0.5 μs有脈沖,信息為“0”。傳輸速率為1 Mbit/s。與S 模式詢問信號一樣, 數據塊最后24 bit是應答信息(前32 bit或88 bit)的循環校驗碼與飛機地址碼的異或數據。

2.3 S 模式詢問編碼產生原理

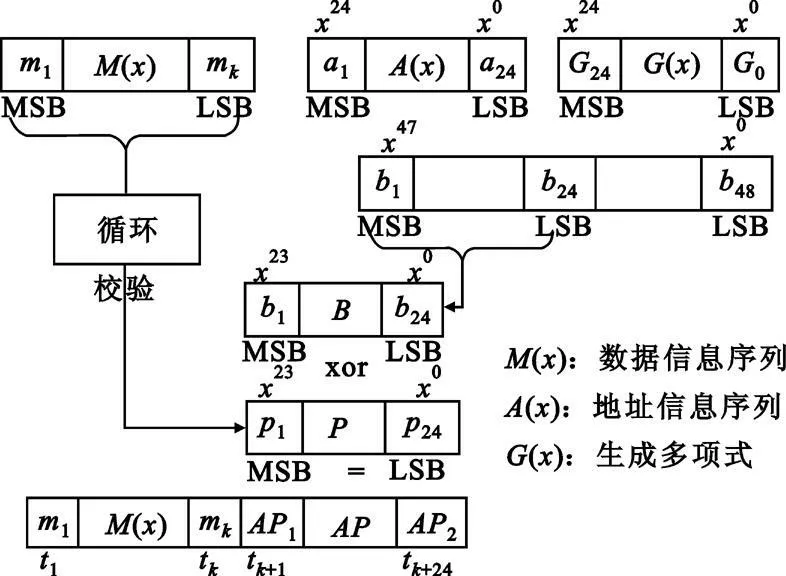

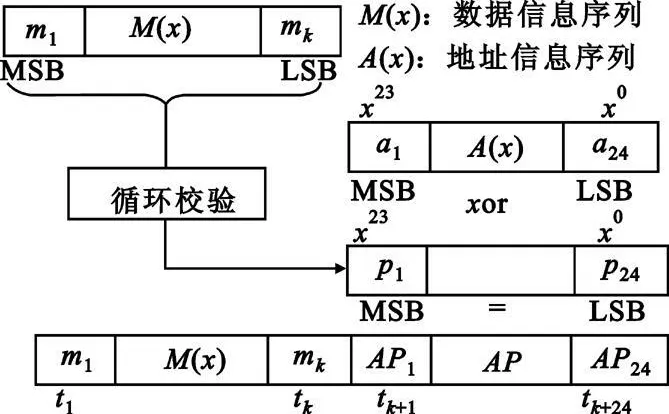

S 模式詢問機啟動S 模式詢問時,由DSP 處理器根據詢問機啟動模式及詢問機狀態設置,計算出詢問信息數據M(x)以及地址碼A(x),FPGA 對數據進行編碼調制(數據編碼原理[2]如圖3 所示),并通過DDS 產生詢問中頻信號啟動詢問發射。

圖3 詢問編碼過程Fig.3 Uplink encoding process

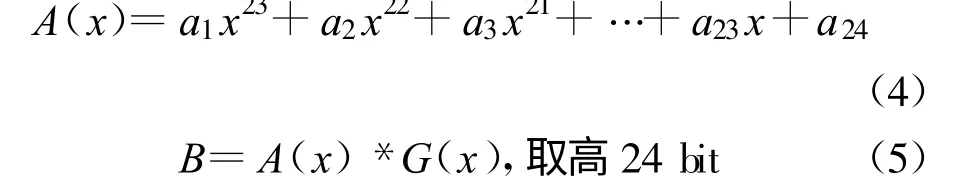

詢問信號數據信息由M(x)(28 bit或88 bit)和AP(24 bit)組成,每種詢問格式(詳細格式內容見ICAO 附件10)對應具體的M(x),將詢問數據信息M(x)與生成多項式G(x)進行循環冗余校驗(CRC)得到數據P ,在S 模式的信號處理中,無論是編碼還是譯碼過程都使用了相同的生成多項式G(x)進行數據的循環冗余校驗,實現對數據的保護,也為詢問機對應答信號的數據檢錯[3]糾錯提供了依據,提高了系統的應答解碼能力。

數據B 為地址A(x)與生成多項式G(x)乘積的高24 bit,其中地址碼A(x)在詢問機全呼詢問和廣播時為全1,點名詢問時為點名的應答機的地址。

數據AP 為多項式P 和多項式B 相異或后的24 bit數據。

2.4 S 模式應答機譯碼

S 模式應答機在工作過程中,接收機一直處于接收狀態(應答機處于應答發射和廣播發射除外),并將下變頻后的中頻信號送入信號處理終端,終端接收并進行詢問信號解碼。終端處理流程如圖4 所示。

圖4 應答機詢問信號FPGA 處理流程Fig.4 FPGA-based interrogatation signal process flow for transpondor

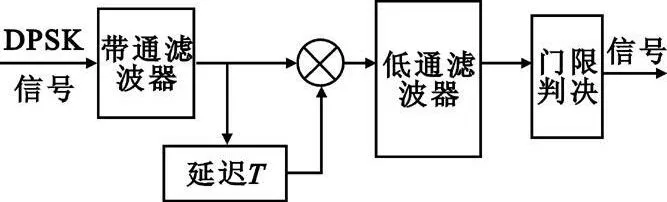

FPGA 接收兩路AD 中頻采樣數據(應答機配備兩個全向應答天線),并進行二進制轉換,再將數據分別進行ASK 解調和DPSK 解調(解調模型見圖5),再進行門限及窄脈沖處理,根據詢問格式提取同步脈沖P1和P2,如果滿足同步頭脈沖條件,則進行上下天線比幅,對幅度強的信號詢問旁瓣抑制處理,同時提取DPSK 解調后的脈沖數據,根據脈沖的幅度寬度等信息進行判斷, 提取詢問數據(56 bit 或112 bit),將詢問數據進行譯碼處理并進行數據檢錯處理,完成后將數據送入DSP 處理器,DSP 根據當前應答機的狀態對詢問數據進行后續處理。

圖5 DPSK 解調模型Fig.5 Block diagram of DPSK demodulation

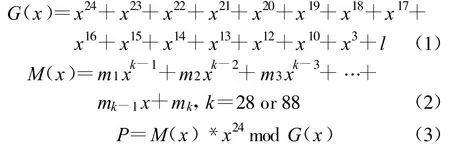

FPGA 實現數據譯碼處理過程,可根據詢問編碼的產生過程進行逆過程處理,得到詢問信號中的地址信息A(x),也可以通過圖6 應答機詢問信息數據解碼過程得到詢問信號中包含的地址信息。應答機對詢問信號數據檢錯的過程實際上就是對譯碼得到的地址信息A(x)的判斷過程,如果A(x)為全1 或者與應答機的地址一致,則詢問數據譯碼正確,進行后續處理,否則譯碼錯誤,本次接收數據丟失。

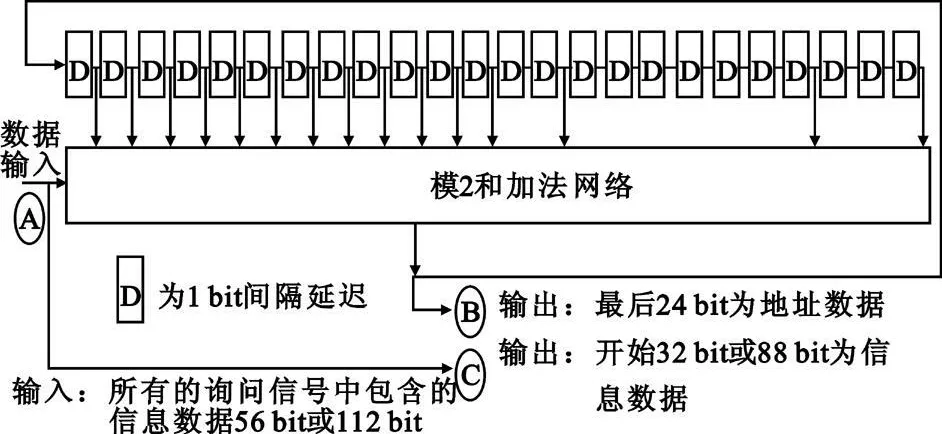

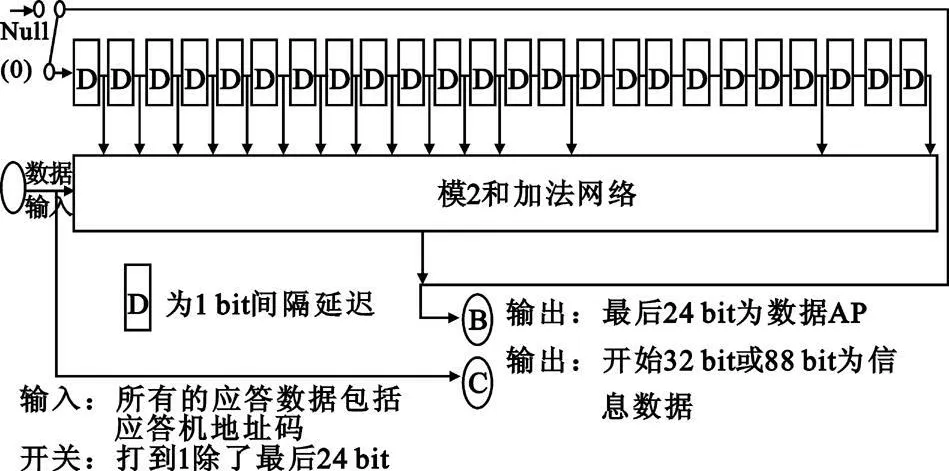

圖6 為S 模式應答機對詢問信號信息數據的等效解碼電路[4],D 為D 觸發器,24 個D 觸發器初始值為0,模2 和加法網絡為所有抽頭的D 觸發器和輸入值模2 和過程。終端FPGA 提取出56 bit 或112 bit數據塊后,將所有數據按先高后低(先收到的數據為高)的順序依次輸入到數據輸入口A,同時保存輸出口C 的前32 bit或88 bit,輸出口B 輸出的最后24 bit即為譯碼得到的詢問信號中攜帶的應答機地址,得到原始的詢問信息數據。

圖6 詢問數據譯碼電路Fig.6 Decoding circuit of interrogation data

2.5 S 模式應答機編碼

S 模式應答機在收到詢問信號(全呼、點名等)后,根據譯碼結果,產生相應的應答信號(應答機自動廣播即S 模式間歇振蕩器報告傳送能力由應答機自己啟動)。應答機的應答信息數據編碼產生過程原理如圖7 所示。

圖7 應答編碼過程Fig.7 Downlink encoding p rocess

終端DSP 處理器根據詢問模式、數據長度、規程、回答概率、分機狀態等信息產生相應格式的應答信號M(x)(28 bit或88 bit),將M(x)和A(x)等數據存入FPGA,FPGA 啟動循環冗余校驗(CRC),得到24 bit校驗數據P,將P 與應答機地址碼A(x)相異或,得到24 bit數據AP,再將所有信息數據(M(x)和AP)進行脈位調制后發射。應答信號的循環冗余校驗和詢問信號的一樣。應答信息數據的編碼可以根據產生原理分步產生,也可以通過圖7 應答信息數據編碼過程產生,在FPGA 中可以快速地實現CRC校驗、數據異或等功能。需注意當應答格式DF 為0、4、5、16、20、21 或24 時,A(x)為應答機的地址;當DF 為11 時, A(x)為17 bit 0、3 bit CL和4 bit IC;當DF 為17 或18 時,A(x)為24 bit 0。

圖8 為S 模式應答機應答信息數據的等效編碼電路,與譯碼電路一樣,24 個D 觸發器初始值為0,模2 和加法網絡為所有抽頭的D 觸發器和輸入值模2和的值。將開關選擇位置1,所有數據按先高后低的順序依次輸入到數據輸入口A(先收到的數據為高),輸入最后24 bit時開關選擇位置0,同時保存輸出口C的前32 bit或88 bit,輸出口B 輸出的最后24 bit即為應答編碼數據的AP ,完成后FPGA 對編碼后的信息數據進行脈位編碼,同時終端啟動應答發射。

圖8 應答數據編碼電路Fig.8 Encoding circuit of reply data

2.6 S 模式詢問機譯碼

詢問機在發射詢問信號后,打開接收機等待接收,應答信號經過接收機下變頻后送入信號處理終端,終端接收并進行應答信號處理。終端數據處理通過FPGA 硬件完成,處理流程如圖9 所示,FPGA完成數據解調、門限、窄脈沖處理后,提取同步脈沖和應答數據脈沖,并進行脈位解調,提取應答數據和設置數據置信度,將提取的數據譯碼處理后,進行數據檢錯處理,如果檢錯后數據正確,則直接將數據送入DSP 處理器,否則進行數據糾錯處理(詢問機信號處理終端必須對檢錯有誤的數據進行糾錯處理,其糾錯原理及方法可參考相關資料,本文不詳細敘述),完成后再將糾錯后的數據送入DSP 處理器,并將詢問結果傳給顯示等外部設備。FPGA 對應答信息數據的譯碼處理,可根據應答機的應答編碼原理進行逆過程處理,也可以根據應答機的譯碼電路(如圖8 所示,應答信號的譯碼電路與應答編碼電路一致,唯一不同的就是譯碼電路端口A 輸入的是所有的應答數據,端口B 輸出的最后24 bit 為應答機的地址碼)來實現。

圖9 詢問機應答信號FPGA 處理流程Fig.9 FPGA-based reply signal process flow for interrogator

詢問信號處理終端對應答信號的檢錯處理,實際上就是對譯碼完成得到的24 bit地址碼與詢問機所問應答機地址碼的比較判斷,如果一致,則數據正確,否則該數據有錯誤,需要進行糾錯處理。

3 數據仿真及結果

在工程設計應用中,根據實際的應用和專業的儀器設備對本文介紹的方法進行了仿真和驗證。圖10 為S 模式詢問信號的產生和處理仿真圖,(a)為S模式詢問發射信號的原始數據(數據信息為0x20123456789abc),(b)是詢問信號經過差分編碼后的信號,(c)為調制后的中頻詢問發射信號,(d)為終端的AD 采樣信號(采樣率為80 Msample/s,橫坐標為采樣點數,縱坐標為12 bit采樣值),(e)為DPSK 解調處理中采樣信號通過一個碼元延遲后相乘結果(即差分相乘),(f)為差分相乘信號經過低通濾波后的信號波形(高于該門限的信號為1,低于門限的信號為0),通過DPSK 解調處理,就得到了波形(g),為濾波后信號進行門限判決后的波形,該解調信號和原始信號是一致的。

圖10 S 模式詢問信號產生和處理仿真波形Fig.10 Modulate and demodu late process of Mode S interrogation signal

在實際調試中,我們通過ChipScope Pro(在線邏輯分析儀)對FPGA 內部的編碼解碼等程序分別進行數據測試,其中兩組數據如下所示。

(1)S 模式詢問編碼

全呼詢問數據前32 bit M(x)=0x58000000,全呼地址為A(x)=0x111111,根據圖3 得到AP =0x4A430A,得到發射數據為0x580000004A 430A;應答機通過圖 6 (或圖 3)可得到詢問數據0x58000000111111。短格式點名詢問數據前32 bit M(x)=0x20000000, 點名應答機地址為A(x)=0x29CBB8,根據圖3 得到AP =0xB115A2,得到發射數據為0x20000000B115A2;應答機通過圖6(或圖3)可得到詢問數據0x20000000B115A2。

(2)S 模式應答編碼

廣播應答數據前32 bit M(x)=0x58000000,廣播地址為A(x)=0x111111,根據圖7 得到AP =0x1F10F2,得到發射數據為0x580000001F10F2;詢問機通過圖 8 (或圖 7)可得到廣播數據0x58000000111111。短格式點名應答數據前32 bit M(x)=0x20000000, 應答機地址為 A (x)=0x29CBB8,根據圖7 得到AP=0xA 9ADE7,得到發射數據為0x20000000 A9ADE7;詢問機通過圖8(或圖7)可得到詢問數據0x2000000029CBB8。

4 結束語

本文主要介紹了詢問/應答信號的處理過程和數據的編解碼原理和硬件實現方法,將傳統主要由軟件完成的數據處理通過硬件FPGA 完成。該設計已經在工程應用中實現,并通過航管專用測試儀器(美國An Aeroflex 公司的MK12/Mode S IFF Accessory Unit)和航管應答機(美國Honeywell 公司的KT73 Mode S Transponder)測試。隨著FPGA 產品的不斷更新換代,FPGA 資源越來越大,功耗越來越低,處理速度越來越快,設計者可以實現更優的信號處理,不斷提高終端的處理能力,實現系統更高的抗干擾和多目標處理能力。

[1] ICAO.Annex10 to The Convention on International Civil Aviation[M] .2nd ed.[S.l.] :International Civil Aviation Organization,1998.

[2] ICAO.Manual on the Secondary Surveillance Radar(SSR)Systems[M] .3the ed.[ S.l.] :International Civil Aviation Organization,2004.

[3] 徐慧.基于TMS320C6416 的S 模式二次雷達應答信號處理系統[ D] .成都:電子科技大學,2005:11-12.

XU Hui.System of the Second Surveillance Radar mode S signal processor base on TMS320C6416[ D] .Chengdu:University of Electronic Science and Technology of China, 2005:11-12.(in Chinese)

[4] 張尉.二次雷達原理[M] .北京:國防工業出版社, 2009:140-157.

ZHANG Wei.The Theory of Secondary Radar[M] .Beijing:National Defense Industry Press,2009:140-157.(in Chinese)