基于FPGA視頻和圖像處理系統的FIFO緩存技術

向厚振,張志杰,王 鵬

(中北大學 信息與通信工程學院,山西 太原030051)

近年來,基于FPGA硬件技術的視頻圖像處理系統被廣泛地應用于視頻智能監控、智能交通系統、視頻采集、跟蹤系統等。作為機器視覺的一個重要研究方向,動態目標檢測在視頻智能監控、智能交通系統等方面得到了越來越多的應用。動態目標檢測是視頻智能化系統的前提,其目的是從視頻圖像序列中將變化區域提取出來。對變化區域的有效提取對后續的目標分類、跟蹤和行為理解等處理都非常重要[1-2]。

視頻圖像處理系統設計中,視頻信號經過采集、緩存、處理、輸出(顯示或存儲)。而緩存模塊的設計取決于視頻圖像數據傳輸速率以及格式大小,根據國際電聯定義的ITU-RBT.656數字圖像接口標準[3],中國采用的是世界上大多數國家所采用的720×576分辨力的PAL制式視頻信號,每幀數據由場消隱信號、行控制信號、有效視頻數據組成,一幀圖像大小為3 240 kbit(灰度數據)。在基于FPGA技術的視頻和圖像處理系統設計中,利用FPGA可配置邏輯資源設計一幀圖像數據緩存單元的方法是行不通的,那么如何更好地利用FPGA芯片有限資源成為FPGA設計的難題。

本文基于Xilinx Vritex-4芯片的動態目標檢測系統設計,合理利用芯片資源,以及根據系統動態檢測設計幀間差分法更有效地完成系統設計,達到動態檢測實時性的目的。

1 動態目標檢測系統架構

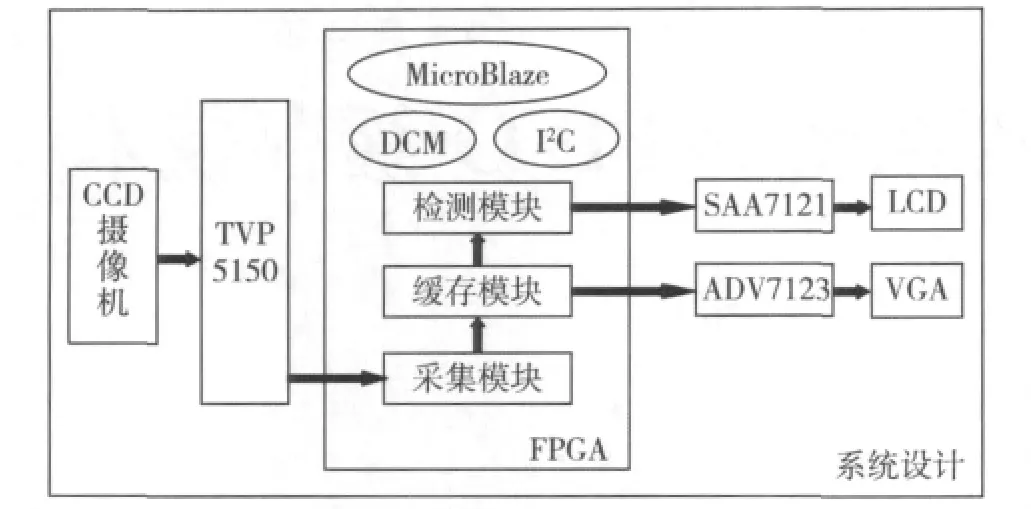

基于FPGA的動態目標檢測系統分為視頻采集模塊、視頻圖像緩存模塊、視頻數據檢測模塊。系統硬件平臺設計框架如圖1所示,FPGA芯片接收由CCD攝像機采集到模擬視頻信號經TVP5150解碼芯片轉換出來的數字視頻信號,FPGA視頻采集模塊檢測數字視頻流當中的有效視頻圖像信號,經圖像緩存模塊緩沖,一路傳輸給檢測模塊進行算法處理,經SAA7121編碼芯片轉換輸出LCD顯示,一路直接還原為視頻數據流信號,完善的系統顯示模塊還包括經ADV7123芯片轉換輸出到VGA顯示器對比,以達到動態目標檢測的可視化效果。此外,系統涉及到FPGA芯片與各個器件之間的硬件連接和通信協議,以及對FPGA內部的邏輯資源進行例化,包括MicroBlaze軟核、IIC總線模塊、DCM模塊等[4-5]。

系統基于Xilinx Virtex-4芯片設計[6],其資源豐富,功能強大,內嵌1個32位的MicroBlaze軟核,集成了10 240個邏輯單元(slice),128個DSP邏輯單元,4個數字時鐘管理模塊(DCM)。這些邏輯單元包含分布式RAM的容量高達160 kbit,塊RAM的容量高達2 304 kbit。這些為視頻流在FPGA芯片內部實現延時提供了緩存空間。DSP邏輯單元為視頻數據流在片內進行運算和處理提供了計算能力上的支持。DCM模塊為內部例化器件提供系統時鐘信號。另外,DCM具有將信號差分、相移、倍頻、分頻等功能,這些都為系統外接器件提供了相應的時鐘信號,使整個系統具有良好的擴展性。

圖1 系統硬件平臺設計

2 FIFO緩存與幀差法設計

動態目標檢測圖像數據緩存的難點在于數據容量大,速率與系統時鐘不一致,以及視頻圖像數據的連續性。視頻圖像處理是以一幀圖像數據進行算法處理為前提。經過解碼模數轉換后的720×576分辨力的一幀數字視頻圖像,包括色度信號Cb和Cr,以及亮度信號Y。一幀圖像分奇數場和偶數場各288行,一行數據以色度信號Cb、亮度信號Y和色度信號Cr按2∶4∶2組成,共1 440個采樣點。其中的Y數據流就是視頻圖像的灰度值數據流,也是人眼敏感的圖像數據,通常圖像處理的也是圖像灰度值。

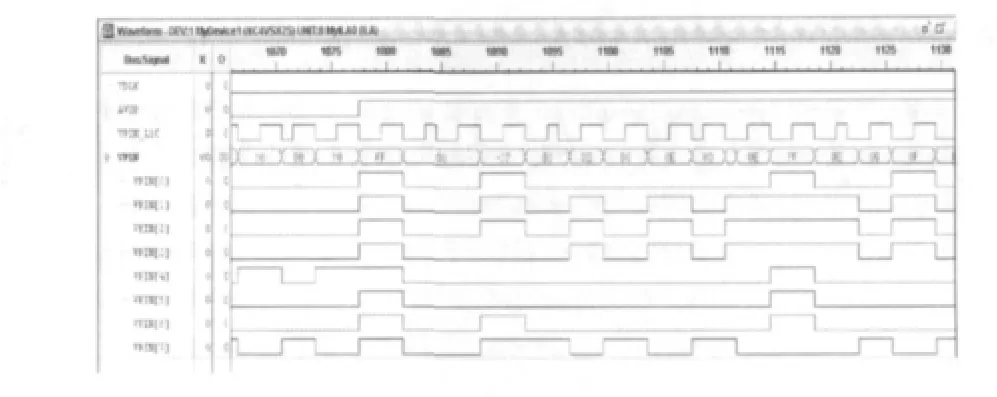

由解碼芯片傳輸給FPGA芯片的視頻信號是頻率為27 MHz的亮度色度混合的數字信號VPIN。該系統利用VPIN_LLC分頻時鐘clk_675將亮度信號(灰度數據信號)單獨提取出來寫入FIFO做處理,但前提是要檢測這些信號是否為視頻有用信號。檢測方式有兩種,一種是通過解碼芯片產生的AVID指示信號檢測高低電平,從而判斷輸出數據是否為灰度數據或無效數據。AVID用來檢測指示VPIN有效視頻起始SAV信號和有效視頻結束EAV信號,圖2是通過在線邏輯分析儀ChipScope Pro得到的系統設計內部信號波形圖。由圖可知,AVID Start跳變指向的是VPIN有效數據起始SAV信號FF,00,00,C7,同樣AVID Stop跳變指向的是EAV信號。另一種檢測方法是通過可綜合的VHDL程序代碼寫狀態機FSM檢測SAV,EAV信號。

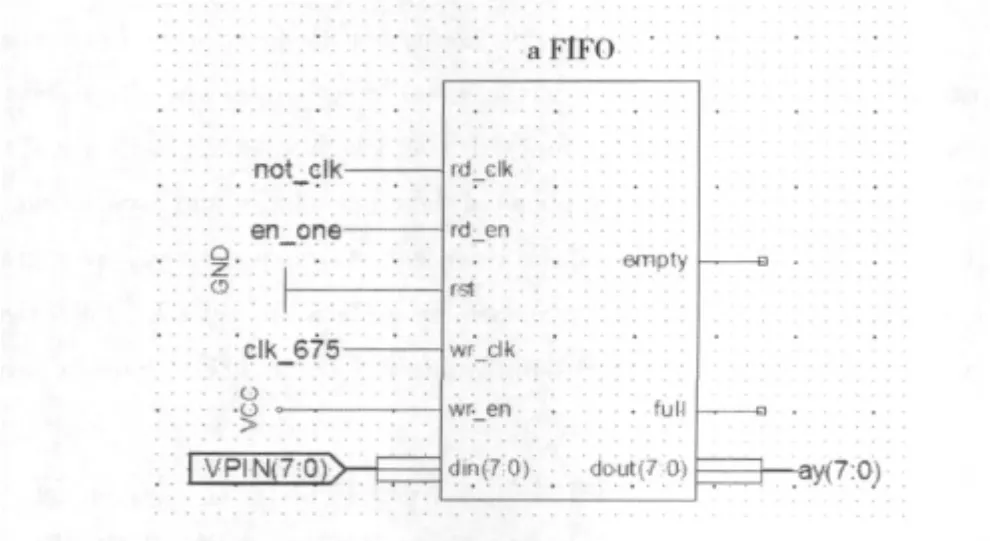

圖3是系統部分設計原理圖。設計中,a FIFO緩存VPIN當中有效灰度數據,b FIFO延遲a FIFO的輸出數據。通過寫時鐘wr_clk控制數據輸入,讀使能rd_en、讀時鐘rd_clk控制數據輸出。當clk_675上升沿到來時,a FIFO寫入VPIN數據流有效數據當中的亮度信號Y,直到a FIFO寫滿半幀奇數場數據或偶數場數據,讀使能en_one打開,讀時鐘not_clk上升沿時讀出數據Y,此時a FIFO輸出是第一幀的奇數場或是偶數場的Y值信號。Y值信號進入b FIFO緩存,相當于將Y值信號做了延遲,讀使能開啟輸出Y信號。在系統時鐘下,兩個FIFO輸出的ay,by則是VPIN第二幀、第一幀的奇數場或是偶數場的Y值信號,將兩個輸出做差法,可得出相鄰兩幀灰度值變化區域。

圖2 ChipScope Pro Analyzer分析結果局部示意圖

圖3 ISE Schematic Symbol FIFO部分原理圖

動態目標檢測就是將視頻圖像序列中變化區域檢測出來,這里通過相鄰兩幀之間做差,將差值通過閾值判斷,得出像素變化區域,進而檢測出動態目標。系統設計中,巧妙地根據幀差法、FIFO緩存達到系統檢測的目的[7-8]。

3 ChipScope在線邏輯分析

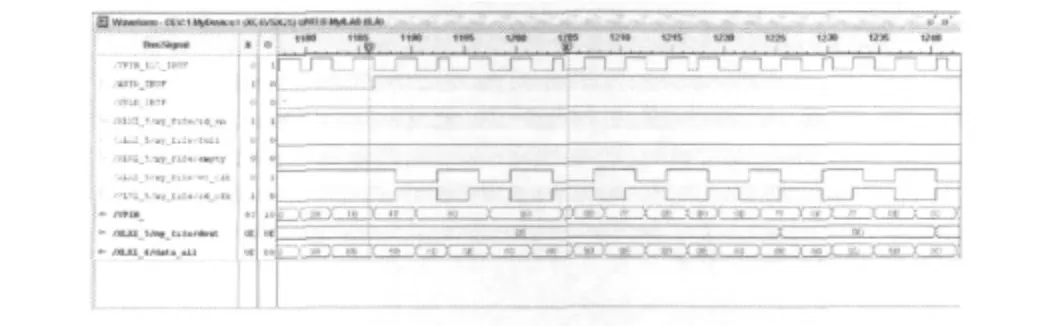

系統設計中的解碼編碼芯片和A/D芯片均由FPGA芯片控制其工作狀態,通過系統設計工具EDK和Platform Studio,對其內部寄存器以及I/O口的配置均由C語言編寫實現。系統內部工作狀態由內部資源實例化MicroBlaze軟核、總線模塊、DCM模塊等實現芯片工作的時序性、穩定性。ISE工程實現系統邏輯處理功能,對視頻圖像序列進行動態檢測。ChipScope在線邏輯分析儀調試查看系統搭建成功后內部信號或節點,包括嵌入式硬件和軟處理器。如圖4所示,系統搭建成功后,各個主要信號實時波形圖。包括視頻輸入信號VPIN、緩存FIFO輸出dout、系統輸出信號data_all以及系統時鐘VPIN_LLC、FIFO讀寫時鐘。由波形可得出,在有效數據位時FIFO進行數據輸入,寫入一場數據后輸出,data_all是系統將有效灰度數據經過檢測模塊處理后還原到視頻序列后的信號,可輸出LCD顯示其動態檢測效果。另外,將FIFO緩存輸出信號直接還原到視頻序列經ADV7123輸出到VGA顯示器[9],可觀測實時視頻圖像,以便對比檢測動態效果。

圖4 Analyzer分析結果

4 小結

視頻圖像處理系統設計中,圖像緩存可以讓系統時序穩定,實時性更高。本文以動態目標檢測系統設計中FIFO緩存與系統設計幀差法巧妙結合,以Xilinx Vritex-4芯片為處理器,TVP5150,SAA7121解碼編碼碼芯片以及ADV7123轉換芯片系統實現了對視頻圖像的動態檢測。系統設計實時性高,穩定性好,其次以FPGA芯片為處理器的系統設計具有小型化、低功耗、開發周期短、投入少、芯片價格適中等優點。該系統設計可應用于基于FPGA的視頻圖像處理系統各類應用場合中,具有一定的擴展性和應用前景。

[1]鄭世寶.智能視頻監控技術與應用[J].電視技術,2009,33(1):95-97.

[2]程明潔.智能視頻監控系統目標檢測和跟蹤技術分析[J].電視技術,2008,32(10):86-88.

[3]ITU-R BT 656,Digtal TV system[S].1995.

[4]田耕,胡彬,徐文波.Xilinx ISE Design Suite 10.x FPGA開發指南[M].北京:人民郵電出版社,2008.

[5]田耘,徐文波.Xilinx FPGA開發實用教程[M].北京:清華大學出版社,2008.

[6]XILINX.Virtex-4 FPGA data sheets[EB/OL].(2010-08-30)[2011-9-07].http://china.xilinx.com/.

[7]王德勝,康令州.基于FPGA的實時圖像采集與預處理[J].電視技術,2011,35(3):38-41.

[8]熊璟,唐廣,唐湘成,等.基于DDR IP核視頻圖像緩存的設計與實現[J].電視技術,2011,35(2):55-57.

[9]宋海吒,唐立軍,謝新輝.基于FPGA和OV7620的圖像采集及VGA顯示[J].電視技術,2011,35(5):51-53.