中頻采樣全數字接收機的設計與實現

齊青茂,王巖建,張華沖

(中國電子科技集團公司第五十四研究所,河北石家莊050081)

0 引言

軟件無線電的基本思想是:構造一個具有開放性、標準化和模塊化的通用硬件平臺,將各種功能用軟件完成。軟件無線電的理想結構,是將模/數(A/D)、數/模(D/A)變換器盡可能地靠近天線[1]。考慮到目前ADC和DAC器件的帶寬以及數字信號處理芯片的處理能力,在接收機中在中頻實現數字化比較合適。

根據偵察接收機的需要,提出了一種基于軟件無線電理論的中頻采樣全數字接收機的設計方案,并且采用XILINX的高性能FPGA芯片進行了實現。

1 中頻采樣全數字接收機總體方案

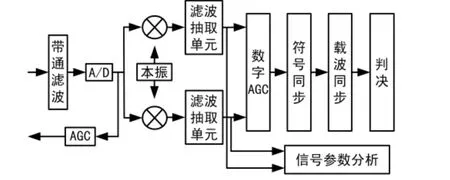

傳統(tǒng)的接收機采用模擬正交下變頻,基帶數字化的方案,在這種方案中,模擬混頻器的非線性和模擬本振的頻率穩(wěn)定度、相位噪聲、溫度漂移和IQ信號的幅相一致性等都是難以解決的問題。中頻數字化接收機,采用數字下變頻技術,避免了以上的問題,能得到嚴格正交的2路IQ信號。

中頻采樣全數字接收機框圖如圖1所示,主要單元包括:帶通濾波器、高速AD采樣單元、數字下變頻、濾波抽取單元、AGC單元、信號參數分析單元以及數字解調單元。

圖1 中頻采樣全數字接收機框圖

輸入的模擬中頻信號首先由帶通濾波器濾除帶外噪聲,經過AD采樣單元轉換為數字中頻信號,數字下變頻單元用一組正交本振信號與輸入的數字信號進行混頻,然后根據信號的帶寬進行濾波抽取,得到2路速率適中的零中頻信號,再對降低速率的信號進行調制類型識別、符號速率以及載波頻偏進行精確估計,2路零中頻信號同時送給后面的數字AGC、符號同步和載波同步模塊進行解調處理。

2 帶通采樣單元

帶通采樣定理是軟件無線電的基礎。用fH和fL分別表示帶通信號的最高頻率和最低頻率,K為[1,fH/(fH-fL) ] 之間的整數,則采樣頻率應該滿足下式:

接收的模擬信號中頻為140 MHz,信號帶寬最大為48 MHz,根據帶通采樣定理可得采樣率范圍為:

采樣頻率增大,量化信號的頻譜重復間隔變大,對抗混疊濾波器的帶外抑制特性要求降低,同時ADC處理增益變大,輸出信噪比增加,但是后級處理負擔會增加。考慮后級信號處理芯片采用XILINX V4系列FPGA芯片,其內部乘法器時鐘速率最高可以達到500 MHz,所以選取fS=190 MHz。

帶通采樣具有頻譜搬移的作用,采樣后信號在50 MHz頻率處出現鏡像譜,該譜是原來模擬信號的負譜,根據傅里葉變換的性質[2]可知該頻譜對應的時域函數應該取共軛。

為了保證ADC采樣后頻譜不混疊,并且不使過多的帶外噪聲進入ADC,設置了4種帶寬的抗混疊帶通濾波器:2 MHz、10 MHz、20 MHz和 50 MHz,根據處理信號的帶寬進行選擇。

3 數字下變頻的設計

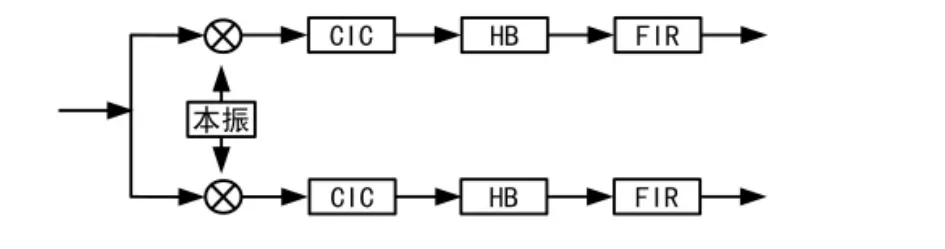

數字下變頻(DDC)由數字混頻器、數控振蕩器(NCO)和濾波抽取單元構成,NCO可將產生的正交本振信號輸入到數字混頻器,與采樣信號混頻,混頻后的信號再輸出抽取濾波器以濾除倍頻分量和帶外信號,并進行抽取處理[3],得到速率適中的2路零中頻信號。當抽取倍數很大時,采用單級濾波會造成濾波器階數非常高,消耗大量乘法器。因此在FPGA中大都采用由積分梳狀濾波器(CIC)、半帶濾波器(HB)和FIR濾波器級聯結構來實現。數字下變頻的實現框圖如圖2所示。

圖2 數字下變頻框圖

在FPGA中,NCO采用相位累加器和正余弦查找表的結構來實現,它的工作時鐘為采樣時鐘,輸入的頻率控制字與輸出頻率的關系如式(4)所示:

式中,N為相位累加器的寬度,FCW為頻率控制字,fout為輸出頻率。在設計中,N取30 bit,輸出位寬取16 bit,頻率分辨率可達0.2 Hz,無雜散動態(tài)范圍可達95 dB,完全可以滿足需要。

數字下變頻輸出信號采樣率為符號速率的4~8倍,下變頻抽取倍數由采樣率和接收信號的符號速率決定。接收信號符號速率范圍為128 kHz~30 MHz,因此抽取率范圍取為1~256,這一抽取范圍由CIC、HB和FIR 3部分完成,CIC完成最大16倍抽取,2級HB濾波器最大抽取4倍,FIR最大抽取4倍。每級濾波器的抽取倍數要根據信號帶寬合理設定。

3.1 CIC濾波器的實現

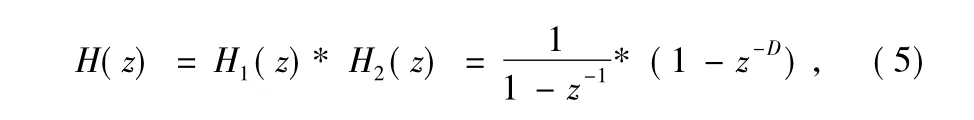

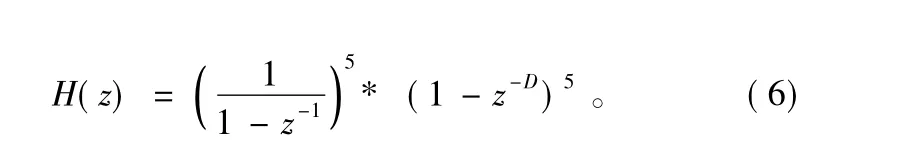

單級CIC濾波器的傳輸函數為:

式中,H1(z)是積分器,它是一個反饋系數為1的單極點濾波器,工作在采樣頻率fS下。H2(z)是梳狀濾波器,工作在一個較低的頻率fS/D,D是抽取因子。

單級CIC濾波器的旁瓣電平只比主瓣低13.46 dB,意味著阻帶衰減很差[4],難以滿足實際要求,為了降低旁瓣電平,采用5級CIC濾波器級聯,相應的旁瓣抑制可以達到67 dB,5級CIC濾波器的系統(tǒng)函數為:

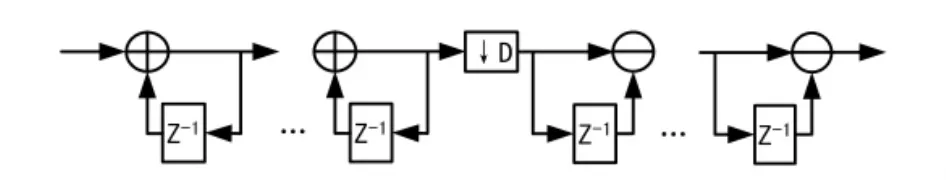

根據濾波器的等效變換,該濾波器可以先實現5級積分器,然后進行D倍抽取,最后進行5級梳狀濾波。

在FPGA中,積分器用加法器實現,梳狀濾波器用減法實現,沒有乘法操作,可以達到很高的處理速度,因此CIC很適合做抽取前的抗混疊濾波器,并且放在采樣率最高的一級。在設計中抽取因子最大為16,級聯CIC濾波器實現如圖3所示。

圖3 級聯CIC濾波器實現框圖

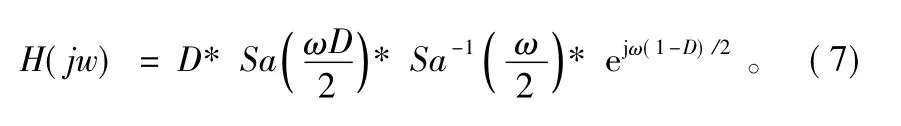

在式(5)中,令z=ejw可以得到單級積分梳狀濾波器的頻率響應:

在CIC濾波器的實現過程中有幾個問題需引起注意:

①CIC輸出分辨率問題。在式(7)中可以看到,5級CIC濾波器D倍抽取的處理增益為D5,當輸入數據位寬為16位,抽取因子為16時,輸出為36位,截取高16位輸出,但是D較小時,數據截位后有效位會大大降低。為了保證輸出截取后依然有足夠的分辨率,需要在CIC輸入端加一級桶形移位器[5],根據D的大小對輸入數據進行左移位,移位值LS可以按照下式計算:

②CIC積分器溢出問題。CIC濾波器直流增益為D,5級CIC級聯則直流增益為D5,在FPGA實現中,輸入信號存在直流偏移時,很容易造成溢出,所以在CIC之前必須有去除直流偏移的電路。

3.2 HB濾波器的實現

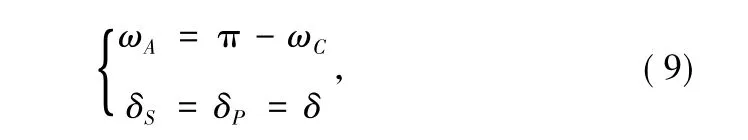

所謂半帶濾波器(HB)就是其頻率響應H(jw)滿足以下關系的FIR濾波器:

或者說半帶濾波器的阻帶寬度π-ωA與通帶寬度ωC是相等的,并且通帶和阻帶的紋波也相等。半帶濾波器的沖擊響應除了零點不為零外,其余偶數點全為零。所以采用半帶濾波器作為抗混疊濾波器時,在FPGA中只需要一半的乘法器,有很高的計算效率[6]。

這種濾波器特別適合于實現2k倍的抽取。半帶濾波器進行2倍抽取后,過渡帶有混疊,但是通帶沒有混疊,所以信號是可以恢復出來的。在設計中采用2級HB濾波器的,每級濾波后進行2倍抽取,最大可以進行4倍抽取。

用MATLAB工具設計濾波器系數,第1級HB濾波器為19階,通帶寬度ωC=0.2,系數量化為16位,阻帶抑制可達80 dB。第2級HB濾波器為27階,通帶寬度ωC=0.3,系數量化為16位,阻帶抑制可達80 dB。

3.3 FIR濾波器的實現

FIR濾波器是濾波抽取的最后一級,要保證通帶的平坦度以及足夠的阻帶抑制。在設計中,階數取60階,通帶頻率取0.23,阻帶頻率取0.35,系數量化為16位,系數對稱,紋波小于0.02 dB,阻帶抑制大于60 dB。

考慮到抽取倍數為1,即不抽取的情況,此時,數據速率為190 Msps,為了保證FPGA內部布局布線的成功,該濾波器采用FPGA內部的乘法器實現,因此本模塊是消耗硬件資源最大的一部分,約需要30個乘法單元。

4 解調單元

經過濾波抽取單元后,帶外噪聲被濾除,有用信號的幅度可能有了很大的變化。幅度不同的信號輸入給符號同步環(huán)路,對環(huán)路增益會產生影響,造成環(huán)路不穩(wěn)定,因此需要通過數字AGC調整信號幅度。AGC環(huán)路是1個一階環(huán)路,其工作過程為:對IQ零中頻信號求功率,再與設定的閾值功率比較,得到幅度誤差,誤差信號送給NCO,產生增益控制系數,調整IQ信號幅度。

符號同步環(huán)路根據異步采樣點的值采用內插濾波器插值得到同步采樣點的值,即插值后的數據速率是符號速率的整數倍(K倍),并且包含判決點(眼圖張開最大點)的值,在設計中K=2。符號同步后一倍符號速率的采樣值輸入給載波同步環(huán)路,糾正載波頻偏相偏,載波環(huán)根據不同的調制樣式選擇不同的鑒相算法,BPSK、QPSK和8PSK采用相應的松尾環(huán),16QAM信號采用通用環(huán)。根據調制類型選擇不同的星座圖,把載波同步后IQ電平值判為相應的星座點,再根據星座點與比特組合的映射關系進行解映射得到比特輸出。

5 設計實現

本接收機設計方案在1塊CPCI接口的采樣及信號處理板卡平臺上得到了實現。其中高速ADC芯片采用 ANALOG公司 AD9430,最高采樣率為210 Msps,分辨率為12 bit,最大模擬輸入帶寬為700 MHz,無雜散動態(tài)范圍可達80 dBc。信號處理部分采用XILINX公司Virtex-4系列高性能FPGA芯片 XC4VLX100和 TI公司高性能定點 DSP芯片TMS320C6455。

本設計方案可以對中頻為140 MHz的模擬信號進行采樣,變頻和基帶基帶信號處理單元都在數字域實現,相比基帶采樣接收機實現方案,具有幅相一致性好、高穩(wěn)定性和體積小等優(yōu)點。通過改變抗混疊濾波器的中心頻率,還可以實現對中頻為70 MHz信號的接收。

DSP主要實現對信號的載波頻率、符號速率和調制樣式等的分析,分析結果送解調單元。

解調相關處理算法首先在MATLAB中進行了仿真,對各級濾波器系數進行了量化,然后在ISE中進行了VHDL的編程,用ModelSim工具進行了時序仿真。該方案通過設置相應的參數可以處理200 kHz~45 MHz帶寬的信號,并且已經實現BPSK、QPSK、8PSK和16QAM等信號的解調處理。另外,可以添加其他調制類型的解調模塊,根據具體信號的特點,在解調后還可以添加比特處理單元。利用FPGA在線加載的功能,可以加載不同的算法模塊,進一步擴展接收機功能。

6 結束語

提出了1種基于FPGA的中頻采樣全數字接收機的實現方案,可以靈活、綜合地實現多種接收機的功能,充分體現了軟件無線電所具有的各種優(yōu)越性。整個系統(tǒng)具有高度的靈活性和可擴展空間,具有較高的應用價值。

[1] 沈琰,田治禮.一種中頻數字化接收機的設計與實現[J].南通大學學報,2006(3):77-79.

[2] 鄭君里,應啟珩,楊為理.信號與系統(tǒng)[M].北京:高等教育出版社,2000:123-126.

[3] 劉凱,王海,周渭,等.一種基于FPGA的數字下變頻器的設計[J].電子元器件應用,2009(1):63-66.

[4] 田耘,徐文波,張延偉.無線通信 FPGA設計[M].北京:電子工業(yè)出版社,2008:215-219.

[5] 陳勇.基于FPGA實現高速專用數字下變頻器[D].四川:電子科技大學,2005.

[6] 王靜,楊梅,劉濤.半帶抽取有限沖激響應濾波器的應用設計及仿真[J].大連海事大學學報,2004,30(2):57-60.