一種基于虛擬儀器技術的任意波形發生器

王水魚,馮曉靖

(西安理工大學 自動化與信息工程學院,陜西 西安710048)

傳統的信號發生器采用模擬電路技術[1],由分立元件構成振蕩電路和整形電路來產生各種波形。采用這種技術的波形發生器電路結構復雜、體積龐大、穩定度和準確度較差,難以產生較為復雜的波形信號。虛擬儀器[2]的出現是儀器發展史上的一場革命,代表著儀器發展的最新方向和潮流,是信息技術的一個重要領域。本文的主要工作是結合虛擬儀器技術進行任意波形發生器的研究與設計。

1 DDS基本原理

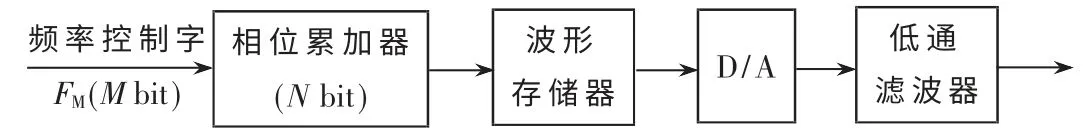

DDS的基本原理是利用采樣原理,然后根據查表產生波形。一個完整的DDS原理如圖1所示。

圖1 DDS原理圖

其電路一般包括基準時鐘、相位累加器、波形存儲器、D/A轉換器和低通濾波器(LPF)[3]。每來一個時鐘脈沖fclk,就送入相位累加器一個頻率控制字X。相位累加器包括一個N位加法器和一個累加寄存器,N位加法器將頻率控制字X與相位累加寄存器寄存輸出的累加相位數據相加,把X與反饋的累加器輸出端的相位數據之和再次送至累加寄存器的輸入端。而相位累加器模塊中的累加寄存器在上一系統時鐘信號周期作用下一方面將已經存儲在寄存器中的相位數據反饋到相位累加器中加法器的其中一個輸入端,以便加法器將其用于在下個時鐘信號的作用下繼續與控制模塊發出的頻率控制字X相加;另一方面,將這個數據作為相位累加器的輸出值送入波形存儲器按照相位查找表查找,并由波形存儲器輸出。最后,波形存儲器的輸出結果經數/模轉換(D/A Converter)和低通濾波器(Low Pass Filter)[4-5]的濾波將其轉換成所需要的模擬波形。相位累加器在時鐘的作用下,連續不斷地進行頻率控制字的線性累加,直至滿量時產生溢出,這樣就完成了一個周期,也是DDS合成信號的一個頻率周期。

DDS的輸出頻率由頻率控制字X決定。輸出頻率與系統時鐘的關系為:

離散樣本的個數由相位累加器位數N決定,可以看出在參考時鐘頻率SYSCLK不變的情況下,通過改變頻率控制字X就可以改變輸出波形的頻率,并且當頻率控制字X=1時DDS的輸出頻率最小。因此,DDS輸出分辨率與相位累加器位數N之間的關系為:

2 系統整體設計方案

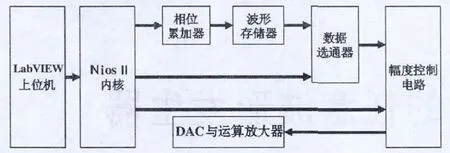

圖2 系統整體設計方案框圖

本設計系統整體框圖如圖2所示。LabVIEW[6]上位機界面主要實現波形的選擇調整和繪制,即實現對基于FPGA的下位機硬件部分的控制。基于FPGA的下位機硬件部分主要包含了DDS模塊以及外圍電路部分。其工作過程如下:LabVIEW上位機負責波形的選擇和調整,當產生固定波形時,LabVIEW上位機將所選擇的波形種類和頻率范圍傳輸給FPGA器件生成的NiosⅡ內核,由NiosⅡ首先向相位累加器模塊輸出頻率控制字,相位累加器通過頻率控制字的累加輸出至波形存儲器中進行波形尋址,將尋址到的波形輸出送入數據選通器[7-8]。NiosⅡ同時向數據選通器送出一個數據選通信號,數據選通器根據選通信號決定輸出波形的種類,然后將確定要輸出的波形數據送入幅度控制電路,幅度控制電路根據NiosⅡ送來的幅度控制數據對波形數據進行幅值調整然后送入DAC與運放電路,經過變換后輸出。如需產生任意手繪波形,則波形數據直接由NiosⅡ內核送至數據選通器,經選擇幅度變換和D/A轉換后輸出。

2.1 FPGA硬件電路部分整體結構設計

系統硬件主要由PLL鎖相環[9]、MY CPU微控制器(Nios II)、波形數據ROM存儲器、相位累加器等核心部分以及外圍電路(包括數/模轉換、放大和通信模塊等)組成。Nios II處理器用于與上位機LabVIEW進行通信、控制輸出選通器、寫任意波形數據至緩存器并輸出,以及調整頻率控制字、幅度控制字等;波形存儲器用于存儲正弦波、方波和三角波的波形數據;相位累加器是DDS的核心部分,由兩個模塊構成,分別是一個移位寄存器和一個累加器;輸出選通器用于選擇將要輸出的波形信號形式(正弦波、方波、三角波或任意波形)。

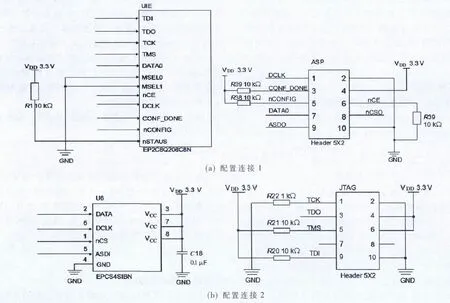

配置方面采用了JATG+AS的配置方法[10],其好處是可以在調試和設計階段先用JTAG方式調試編寫的程序,待最終驗證所有的程序已經完好無誤后,再使用AS模式把已經修改好的程序下載寫入到配置芯片里去。此處用到了一塊EPCS4SI8N芯片對其進行配置,配置芯片以及兩種配置連接如圖3所示。

2.2 上位機軟件設計

LabVIEW上位機主面板設計如圖4所示。可以看出,主程序面板上提供了波形選擇、頻率調節、幅度調節等功能,其中波形選擇包括了正弦波、方波和三角波以及手工波形繪制;頻率調節支持上下箭頭和手工輸入;幅度調節支持上下箭頭調節。

在波形繪制界面中,使用者可以通過鼠標點擊在波形繪制面板上進行手工繪制。手工繪制波形時,使用者按鼠標左鍵不放,在面板左側的空白區域進行繪圖,右側第一個窗口按照使用者繪制的鼠標圖像進行采樣取值,顯示采樣點以及采樣數據,繪制完成后點擊停止。手繪波形功能的程序框圖如圖5所示,手繪波形的過程中定義了鼠標左鍵點擊、鼠標移動、鼠標松開等幾個用戶事件。

圖3 FPGA配置圖

圖4 主面板

圖5 手繪波形功能的程序框圖

3 調試及實驗結果

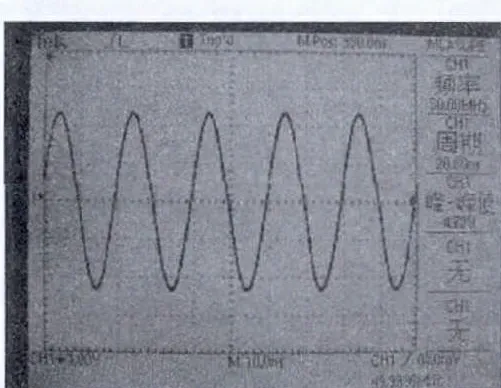

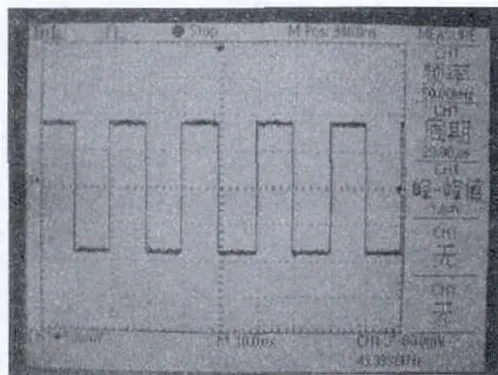

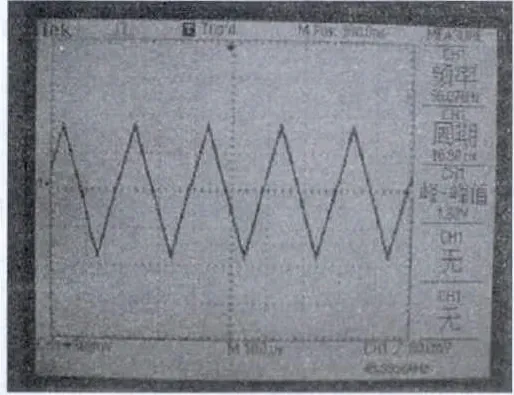

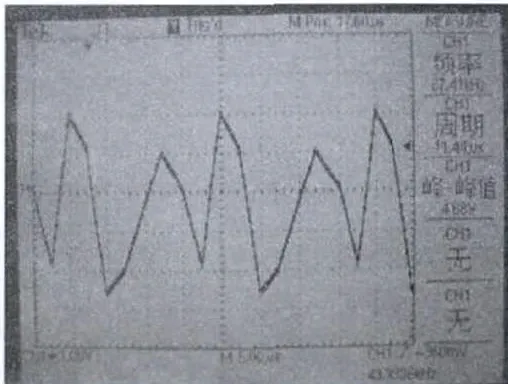

通過下位機輸出端連接示波器顯示產生的三種固定波形(正弦波、方波、三角波)和任意手繪分別如圖6~圖9所示。

圖6 正弦波

圖7 方波

圖8 三角波

圖9 任意手繪波

4 結果分析

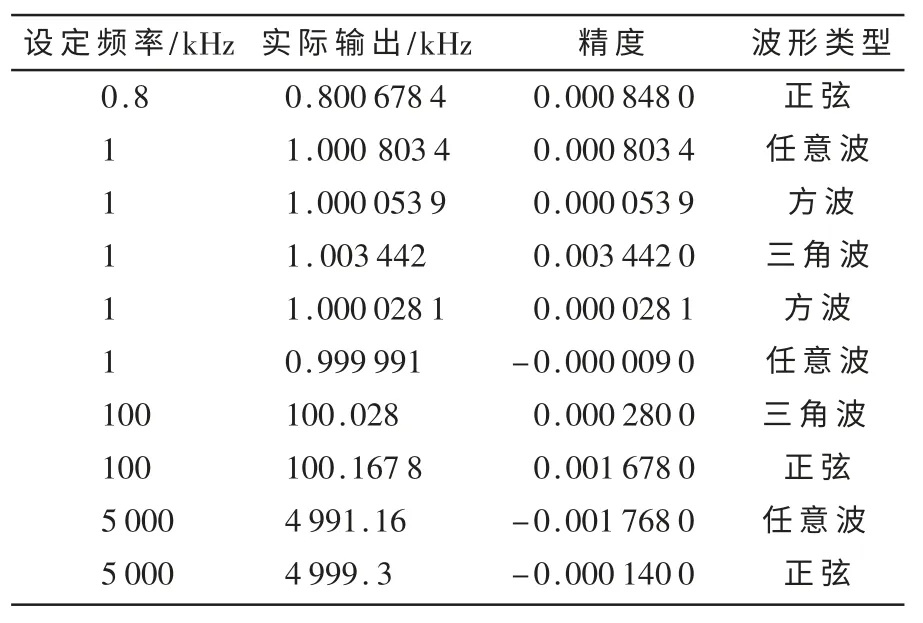

信號源的主要指標為頻率指標,包括最大輸出頻率和頻率分辨率。經過對不同狀態下不同波形的數據采集,得出表1所示的波形數據表格。

表1 設定頻率與輸出頻率

經過表格數據計算,輸出信號的平均精度為0.004 065 76%,最大輸出頻率為5 MHz,且在信號頻率大于5 MHz后失真嚴重。

[1]陳永泰,潘志浪.基于FPGA的DDS信號源設計[J].電子元器件應用,2007,9(9)∶45-47.

[2]黃軼程.采用虛擬儀器技術的任意波形發生器的研制[D].南京:東南大學,2005.

[3]俞一鳴,唐薇,陸曉鵬,等.Altera可編程邏輯器件的應用與設計[M].北京:機械工業出版社,2007.

[4]王誠,吳繼華,范麗珍,等.Altera FPGA/CPLD設計(基礎篇)[M].北京:人民郵電出版社,2005.

[5]王偉,趙吉祥.基于FPGA+DDS的控制設計[J].國外電子元器件,2008(6)∶13-15.

[6]王呈貴,徐以濤.高分辨率DDS的FPGA設計[J].解放軍理工大學學報,2003,4(4)∶20-22.

[7]豆衛敏.基于全數字鎖相環的時間數字轉換器的研究[D].杭州∶浙江工業大學,2009.

[8]夏瀑.基于分布式算法的FIR濾波器設計及FPGA實現[D].大連∶大連海事大學,2008.

[9]Altera.Cyclone II devise handbook[Z].2008.

[10]EDA先鋒工作室,王誠,蔡海寧,等.Altera FPGA-CPLD設計(基礎篇)[M].北京:人民郵電出版社,2011.