一種低壓低功耗的亞閾型CMOS基準電壓源

劉宇,王丹

(西南交通大學信息科學與技術學院,四川成都610031)

傳統的帶隙基準電壓源以其良好的溫度穩定性和電源抑制特性被廣泛應用于A/D轉換器、D/A轉換器、開關電源以及存儲器的數模混合信號集成電路中,其性能好壞直接影響整個電路功能的實現。隨著數據轉換精度的不斷提高,傳統帶隙基準源的精度已很難滿足電路設計的需要。有很多關于設計基準源的文獻使用成本較高的工藝,例如BiCMOS工藝。還有一些文獻是把具有溫度依賴的對數項進行泰勒展開,然后對二階項甚至高階項進行補償,但是這種方法不能全部抵消掉所有高階項,因此設計的基準源精度很有限。

隨著CMOS工藝的不斷發展,低電壓和低功耗越來越重要。為了滿足不斷降低的電壓和功耗的要求,本文提出了一種新型的CMOS亞閾型基準電壓源的設計方法。將MOSFET管偏置在亞閾值工作區已成為一個重要的低壓、低功耗設計方法。CMOS亞閾型基準電壓源電路設計的關鍵,是把需要的MOSFET管偏置在可以控制的亞閾工作區,產生一個具有負溫度系數的電壓,然后與正溫度系數的電壓進行適當權重的相加,得到一個零溫度系數的電壓基準。

1 亞閾型基準電壓源的工作原理

經典的帶隙基準電壓源,其工作原理在于利用PN結電壓的負溫度系數,與不同電流密度下PN結電壓差的正溫度系數相互補償,最后得到一個具有零溫度系數的電壓基準。而亞閾值型基準電壓源的工作原理則不同。亞閾值區又被稱為弱反型工作區,介于強反型區與截止區之間。Filanorsky和Allam在文獻[2]中研究了MOSFET的溫度特性,明確指出MOSFET低于一個與溫度有關的特定偏置點時,MOSFET的“柵-源”電壓隨溫度的增加而減小,具有負的溫度系數。可以利用MOSFET的“柵-源”電壓代替三極管的“基-射”電壓,來設計一個與溫度系數無關的基準電壓。在本文的設計中,具有正溫度系數的電壓是利用PTAT電路產生的,PTAT電路是一個典型的具有正溫度系數電流的電路。負溫度系數的電壓是利用MOSFET的“柵-源”電壓產生的。最后把正負電壓進行適當的權加,就得到一個具有零溫度系數的電壓基準。

下面的理論推導將用到以下符號,S=W/L表示CMOS管的寬長比,φB表示表面勢,φB表示襯底費米勢,NCH表示襯底摻雜濃度,UT=kT/q表示熱電勢,n=1+Cd/Cox表示亞閾型斜率因子,T0表示室內溫度300 K,εsi表示硅的介電常數,Eg表示硅的能隙等。

假設MOSFET的溝道長度足夠長,VBS=0,VBS>4UT,漏電流的等效表示為:

如果φS=φB,則:

VOFF是用于BSIM3v3的一個矯正常數項[6]。因此,比較(1)和(2),可以得到相同的漏電流:

其中φB和φS與溫度有下面的關系式:

因此,可以得到的一個溫度函數的表達式:

由于給出的漏電流表達式等價于(3),所以可以得到下面這個表達式:

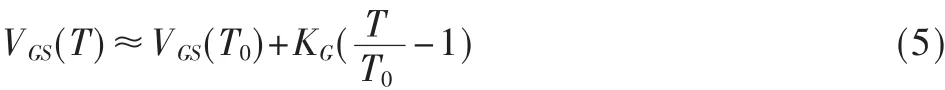

假設n(T)隨溫度有很小的改變(n(T)≈n(T0)),在KT<0時,閾值電壓模型為:

可以得到:

其中:

KT,VOFF,VGS-VTH和KG的典型值都是負數,因此,對任何固定漏電流ID,電壓VGS都隨溫度的增加而減小。所以是一個典型的負溫度系數的電壓。G.Ciustolisi在文獻[3]中通過實驗證明理論推導模型表達式(5)與MOSFET的實際行為表現是一致的。經過理論的推導和實驗的證明,VGS是個可以用來設計基準電壓源的負溫度系數電壓。因此本文的負溫度系數電壓就利用VGS來產生。

2 電路結構的設計

綜上所述,可以得到:VR=V1+V2+V3+V4

化簡為:

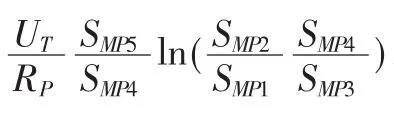

于是

使式(7)成立的溫度就是溫度系數為零時的溫度,此時α與β的值可以通過調節M4~M9,MP1~MP4的寬長比以及R1~R4和Rp等電阻來調節,從而可以方便地決定溫度系數為零的輸出電壓值。

3 電路實現及仿真結果

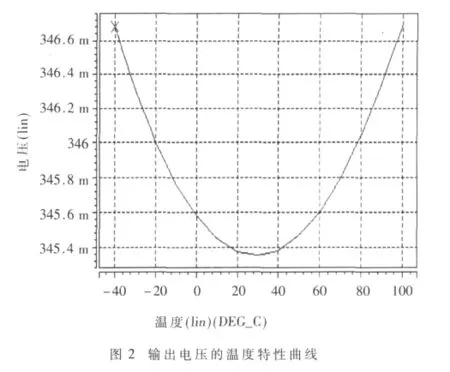

本文所設計的電路采用0.35 μm CMOS工藝實現,主要參數:VTn=0.479 V,VTp=-0.827 V。電路的電源電壓1.2 V,顯然,采用低門限處理過程能夠提供低電源。整個電路的仿真采用Hspice軟件仿真,仿真結果如圖2所示,溫度系數(TCVR=V(T0)-1ΔV/ΔT)在-40℃~+110℃范圍內,其值大約為262.6 ppm/℃。低頻時電源抑制比為-27 dB。在27℃時,輸出電壓VR的值為345.36 mV,總電流為5.45 μA。

本文介紹了一種新型的低電壓、低功耗、低溫度系數和工作在亞閾值區的CMOS基準電壓源。一種在溫度表現方面類似于三極管的“基-射”電壓差的亞閾值型CMOS“柵-源”電壓。這個電路是完全的CMOS電路,不需要用到BiCMOS工藝,簡單的電路結構也降低了芯片的制造成本。但是電源抑制比不是很高,可以在輸出端增加負反饋電路或改進電路結構,來提高電源抑制比。需要指出的是,工作在亞閾值區的電路基本上局限于低速電路,與工作在強反型層電路相比,工作在弱反型層的MOSFET器件溝道尺寸減小了。

[1]RAZAVI B.Design of analog CMOS-Circuit design,Layout and Simulation.Piscataway,NJ:IEEE Press,1997.

[2]FILANOVSKY I M,ALLIAM A.Mutual compensation and threshold voltage temperature effects with application in CMOS circuits[J].IEEE trans,Circuit Syst I,2001,48(7):876-884.

[3]GIUSTOLISI G,PALUMBO G.A low-voltage low-power voltage reference based on subthreshold MOSFETs[J].IEEE JSSC,2003,38(1):151-154.

[4]PALUMBO G,PENNISI S.Feedback Ampilfiers:Theory and Design,New York:Kluwer,2001.

[5]VITTOZ E A,FELLRATH J.CMOS analog integrated circuits based on weak inversion operation[J].IEEE JSSC,1977,SC 12(3):634-643.

[6]CHENG Y,HU C.MOSFET Modeling&BSIM3 User’s Guide,New York:Kluwer,1999.