基于FPGA和ZigBee的無線數據采集系統

王 濤,王紫婷,劉文博

(蘭州交通大學電子與信息工程學院,甘肅 蘭州,730070)

0 引言

應用ZigBee技術和FPGA技術所研制的無線數據采集系統,克服了傳統數據采集系統的缺點。目前比較實用的短距離無線通信技術包括紅外、藍牙技術以及IrDA 技術等等.綜合考慮硬件設計復雜度、接口方式、開發周期、開發成本以及通信距離等因素。設計采用ZigBee技術來實現數據的無線傳輸。采用EP1C3T144C6來完成整個系統的控制和數據采集功能,性能大大優于傳統的單片機控制數據采集系統。實驗結果證明,該系統操作簡單,工作穩定可靠,具有廣闊的應用前景。

1 系統總體設計

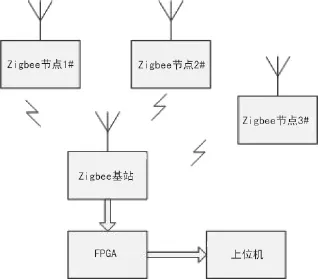

由Zigbee各節點采集數據并傳輸至Zigbee基站,基站和FPGA之間應用串口進行通信,再將數據傳送到FPGA,FPGA作為整個系統的核心控制部分,完成整個系統的數據處理和控制。如圖1是系統的整體結構圖。

圖1 系統整體結構圖

2 硬件設計

2.1 FPGA部分

1)FPGA配置

FPGA上電以后會有3個狀態,首先進入配置模式(Configuration),將編程文件載入器件,在最后一個配置數據載入到FPGA以后,進入初始化模式(Initialization),這個過程中復位各類寄存器,為正常工作做準備。當初始化完成以后,隨即進入用戶模式(User-Mode)。在配置模式和初始化模式下FPGA的用戶I/O處于高阻態(或者內部弱上拉狀態),當進入用戶模式時,用戶I/O就將按照所設計的功能正常工作。

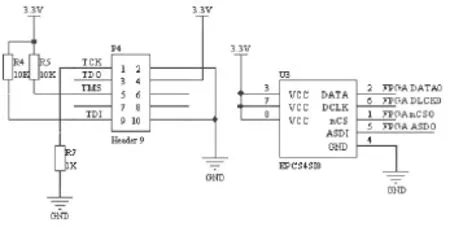

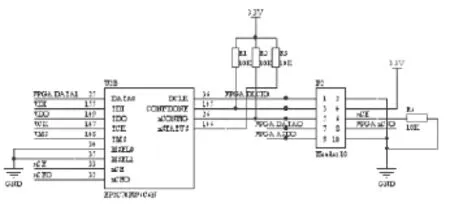

系統在設計中既保留了JTAG配置方式,又保留了AS配置方式,硬件配置電路圖分別如圖2和圖3所示。在JTAG配置方式下,TCK需要下拉到地,只接一個1kΩ下拉電阻就能滿足要求,TMS、TDI需要上拉到3.3V,所使用的電阻是10kΩ,這也是為了防止影響正常的配置以及工作;同樣在AS配置口的設計中nCE需要下拉到地,nSTATUS、CONF_DONE和nCONFIG需要上拉到3.3V,所用的上拉電阻和下拉電阻都是l0 kΩ,這些是為了確保在使用JTAG配置或者正常使用時,這些管腳能處在一個正確的電平狀態。因在本設計中采用JTAG和AS配置方式,所以將MSEL0和MSEL1接地就可以支持這兩種方式 。

圖2 JTAG配置方式

圖3 AS配置方式

2)FPGA外圍電路設計。FPGA系統一般需要多電源供電,內核電壓為1.8V,外圍輸入/輸出電壓為3.3V,所以采用TI公司的TPS70451為FPGA供電,它采用5V輸入,1.8V和3.3V輸出,最大輸出電流達2A。FPGA的時鐘源電路采用外接50MHz的晶振作為Cyclone FPGA的外部時鐘源。

2.2 ZigBee部分

選用TI公司的CC2430芯片。CC2430是一顆真正的系統芯片(SoC)CMOS解決方案.這種解決方案能夠提高性能并滿足以Zigbee為基礎的2.4GHz ISM波段應用,及對低成本,低功耗的要求。它結合一個高性能2.4GHz DSSS(直接序列擴頻)射頻收發器核心和一顆工業級小巧高效的8051控制器 。

CC2430芯片需要很少的外圍部件配合就能實現信號的收發功能。電路使用一個非平衡天線,連接非平衡變壓器可使天線性能更好。電路中的非平衡變壓器由電容和電感以及一個PCB微波傳輸線組成。內部T/R 交換電路完成LNA和PA之間的交換。用1個32 MHz的石英諧振器和2個電容構成一個32 MHz的晶振電路。用1個32.768 kHz的石英諧振器和2個電容構成一個32.768 kHz的晶振電路。電壓調節器為所有要求1.8V電壓的引腳和內部電源供電。引出所有可用I/O,并提供RS232串行接口,用于系統的擴充和通信等功能 。

3 軟件設計

3.1 FPGA的軟件實現

FPGA與ZigBee基站的串行通信,整個設計采用模塊化的設計思想,可分為3個模塊:FPGA波特率發生器模塊,RS232接收器模塊和RS232發送模塊。

RS232發送器的用途是將準備輸出的并行數據按照基本異步串行通信的幀格式轉為TXD信號串行輸出。RS232接收器接收RXD串行信號,并將其轉化為并行數據,但串并轉換的時鐘同發送器一樣處理,收發設備間的時鐘是會累計的,會導致接收數據不正確,波特率發生器就是專門產生一個遠遠高于波特率的本地時鐘信號對輸入RXD不斷采樣,以不斷地讓接收器與發送器保持同步 。

1) RS232串行通信的波特率發生器

波特率發生器實際上就是一個簡單的分頻器,可以根據給定的系統時鐘頻率(晶振時鐘)和要求的波特率算出波特率分頻因子,已算出的波特率分頻因子作為分頻器的分頻數。對于波特率發生器中的系數一般在FPGA實現時往往是固定的,但對于不同的實現,這個系數需要更改。波特率發生器產生的分頻時鐘,不是波特率時鐘,而是波特率時鐘的16倍,目的是為了在接收時進行精確的采樣,以提出異步的串行數據 。

2) RS232串行通信的接收器

由于串行數據幀和接收時鐘是異步的,由邏輯1轉為邏輯0可以被視為一個數據幀的起始位。然而,為了避免毛刺的影響,能夠得到正確的起始位新后,必須要求接收到的起始位在波特率時鐘采樣的過程中至少有一般都是屬于邏輯0才可認定接收到的是起始位。由于內部采樣時鐘bclk周期(波特率發生器產生)是發送或接收波特率時鐘頻率的16倍,所

以起始位需要至少8個連續balk周期的邏輯0被接收到,才認為起始位接收到,接著數據位和奇偶校驗位將每隔16個bclk周期被采樣一次(即每一個波特率時鐘被采樣一次)。如果起始位的確是16個bclk周期長,那么接下來的數據將在每個位的中點處被采樣。

3)RS232串行通信的發送器

發送器只要每隔16個bclk周期輸出1個即可,次序遵循1位起始位、8位數據位和1位停止位。本設計中沒有校驗位,但只要改變Generic參數FrameLen,也可以加入校驗位,停止位是固定的1位格式 。

3.2 ZigBee部分的軟件設計

1)在ZigBee基站中首先初始化CC2430和液晶,然后程序開始初始化協議棧并打開中斷。之后程序開始格式化一個網絡,如果網絡格式化成功,可以在液晶上或是通過串口看到格式化網絡的一些信息,之后程序開始進入應用層,有節點加入網絡之后,節點發送過來的數值和按鍵信號就會被顯示在液晶上。

2)在ZigBee節點中程序同樣首先初始化CC2430,然后打開傳感器電源。之后初始化協議棧,就開始發送加入網絡信號,等待主機響應,并給自己分配網絡地址。如果加入網絡成功,ZigBee節點指示燈就會點亮。如果加入失敗則不亮。

加入網絡成功后,Zibee節點就可以向ZigBee基站發送數據及按鍵值了。此后程序開始循環發送數據和按鍵值。Zibee節點每隔一段時間采集一次數據和掃描一次按鍵值,然后把數據打包再發送到Zibee基站,并開始接收應答。如果發送成功,Zibee節點回到空閑狀態;如果發送不成功,Zibee節點馬上重新采集一次數據再發送給基站,直到發送成功。

3)上位機軟件設計

在本系統設計中,用VC開發環境來實現對FPGA采集的數據進行處理和顯示等功能,上位機程序主界面如圖4所示。

圖4 上位機程序主界面

4 結果分析

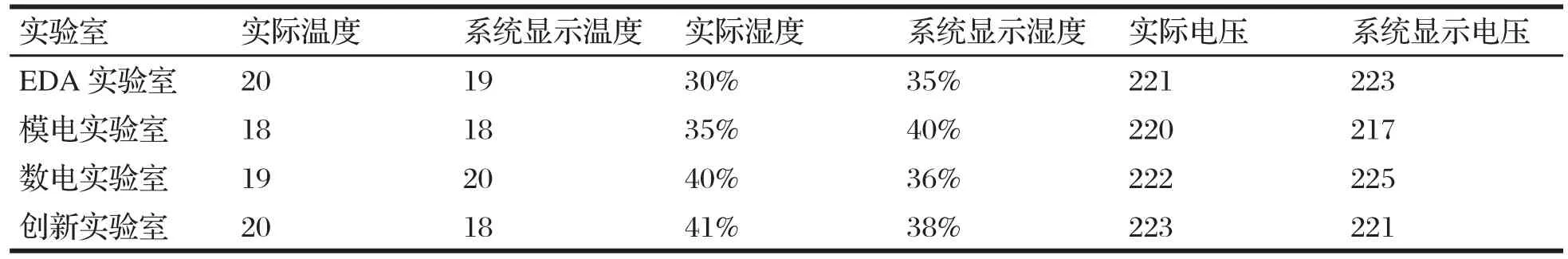

經過實際測試,4個節點所采集的數據和實際數據如表1所示。

根據數據,除濕度測試部分需要繼續改進,使其精度更為精確為,其余部分均符合設計目標。

表1 系統測試數據與實際數據比較

[1]董亞超.基于ZigBee技術的無線環境監測網絡的開發[D].大連:大連理工大學,2008.

[2]文璧,張潔,徐謙.基于無線射頻與FPGA技術的數據采集系統[J].中國測試,2009.

[3]王彥.基于FPGA的工程設計與應用[M].西安:西安電子科技大學出版社,2007.

[4]田春雷.基于FPGA的機房環境參量采集系統設計[D].呼和浩特:內蒙古工業大學,2007.

[5]王志華.基于FPGA的四路同步數據采集和處理系統的設計[D].南京:南京理工大學,2007.

[6]李文仲.ZIGBEE無線網絡技術入門與實戰[M].北京:北京航空航天大學出版社,2007:184-200.

[7]張明.基于PIC單片機和DS18B20的溫度測量系統設計[J],電子測試,2010(4).

[8]孫波.基于MSP430的串口擴展設計[J].電子測試,2010(4).