IC封裝中互連線信號完整性的研究

高雪蓮,陳銀紅,雷曉明

(華北電力大學電氣與電子工程學院,北京 102206)

1 引言

隨著電子產品芯片復雜度不斷提高,噪聲容限、功耗和特征尺寸不斷降低,同時隨著互連線所傳輸的脈沖信號擴展到微波、毫米波頻段,互連線已不能簡單視為無電阻、無電容、無電感的金屬導線。在高頻或交流的情況下,信號的波長已與互連線的尺寸處于同一數量級,信號脈沖在互連線上呈現明顯的波動效應。因此,在現代高速大規模集成電路系統中,封裝結構尤其是互連線系統對整個電路系統電特性的影響日趨明顯,對互連、封裝結構電特性的分析在整個高速集成電路系統的分析和設計中占有越來越重要的地位。

2 建模與仿真

本仿真首先采用基于有限元法(Finite Element Method,FEM)的三維電磁場軟件Ansoft Q3D,建立不同管腳電壓輸入時芯片管腳的三維物理模型,然后對模型劃分網格,利用有限元法進行分析,得到精確的電容電感矩陣參數;接著采用參數提取方法提取部分等效管腳參數值;最后,利用優化仿真功能不斷改進參數得到較理想的結果。

2.1 建立模型

首先需要建立不同管腳電壓輸入時芯片管腳的三維物理模型。IC封裝的互連線封裝外殼模型由基板(host_board)、填充材料板(trans_board)、地(trans_gnd)、引線(pin)、封裝外殼(body)、上下壓焊塊(hpad,tpad)等部分構成,各個部分的結構尺寸和材料參數的設定參見表1。

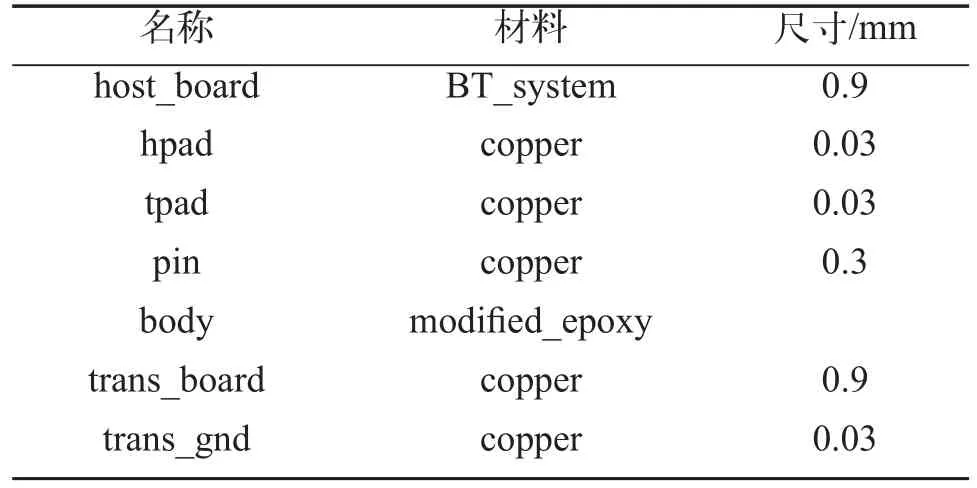

表1 互連線各個部分尺寸和材料設定參數

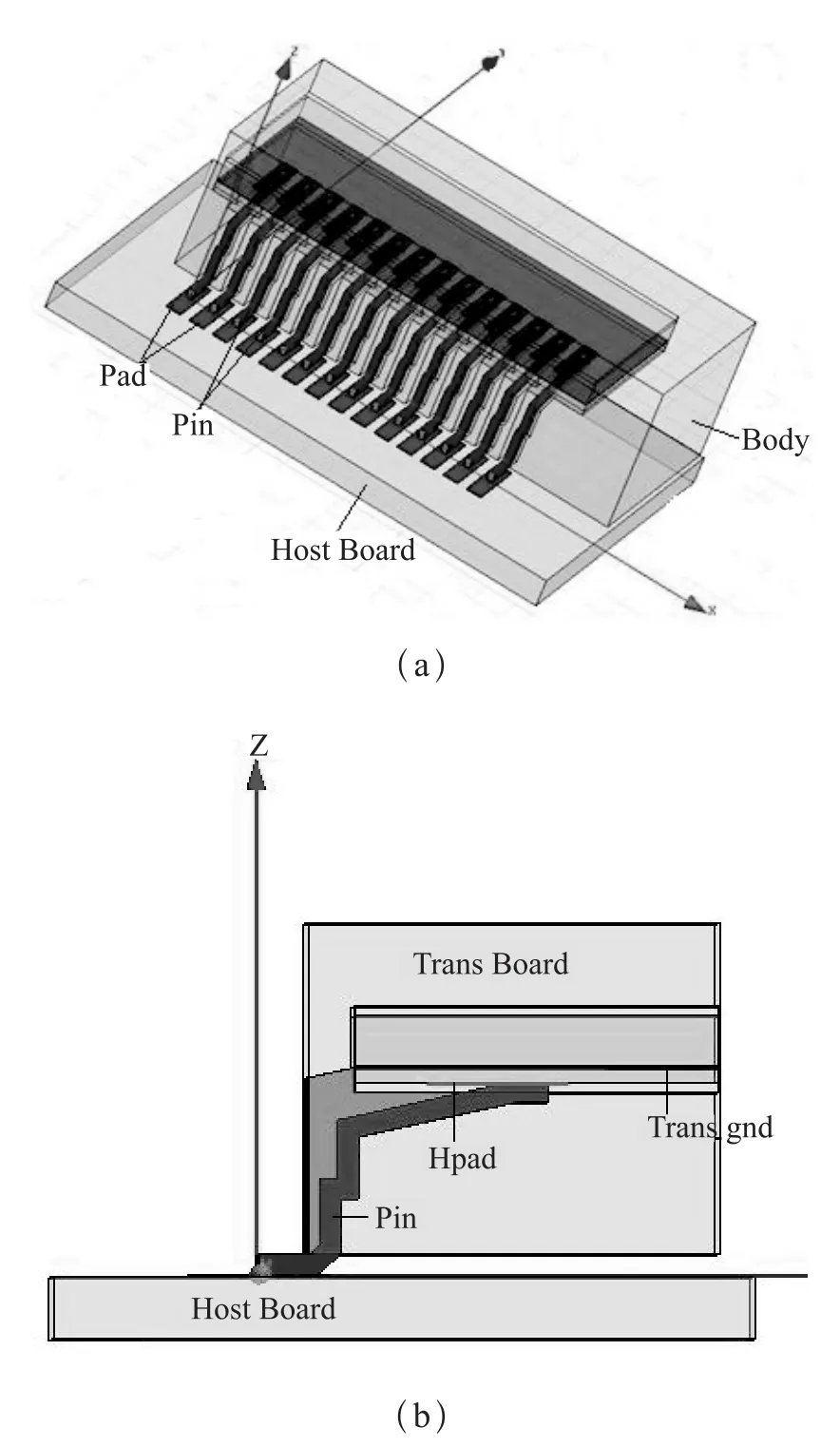

由于該模型具有對稱性,所以本實驗選取模型的四分之一建立。通過確定芯片封裝結構尺寸,定義模型的材料屬性(電導率、電介質常數、磁介質電常數及電介質損耗參數)以及模型的布爾運算,最終完成Q3D有限元模型的建立,圖1(a)和(b)分別示出了所建立模型的透視圖及側視圖。

2.2 模型分析

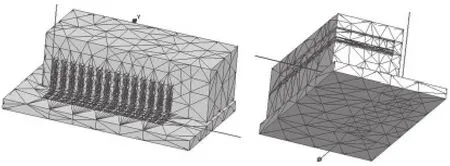

Ansoft Q3D Extractor將所建立的模型自動劃分為若干個節點,節點相互連接形成網格,每個網格可以稱為一個有限元。對模型進行合理的網格劃分才能保證用較少的計算資源和時間得到高頻下芯片電容、電感矩陣分布等有價值的數據,封裝模型網絡分配圖如圖2所示。

在完成網絡分配的工作后,需要對提取線路兩端口的網絡源端(Source)和末端(Sink)進行設置,因為該操作會影響信號流及表面電流密度場的方向,從而影響互感的正負值。本文將臨近芯片的下接合墊Tpad定義為源端,上接合墊Hpad定義為末端(Sink)。

圖1 封裝模型透視圖(a)及側視圖(b)

圖2 模型網格分配圖

2.3 參數提取

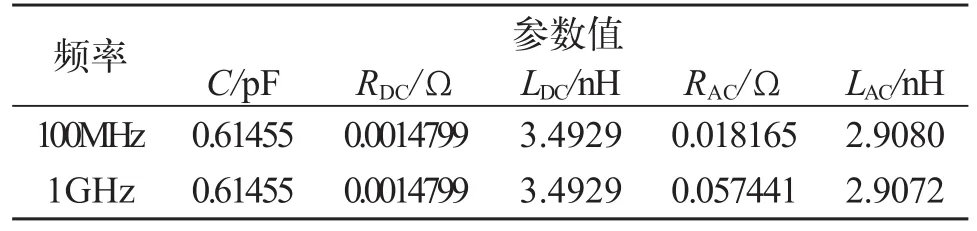

通過對芯片不同管腳施加高低電平,預測產生的電容、電感,進而減小矩陣規模,對矩陣進行優化,可得到較好的電容電感的矩陣參數及表面電流密度場。本實驗在100MHz和1GHz的頻率下分別提取同一根引線(pin14)的RLC參數,實驗數據如表2所示。由表2可知,隨著頻率的提高,由于趨膚效應和介質的耗散因子存在,傳輸線上的交流電阻值增大,電感減小。

表2 100MHz 和1GHz頻率下引線的RLC參數

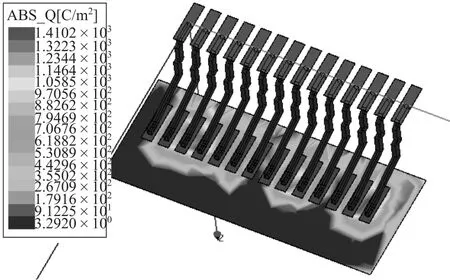

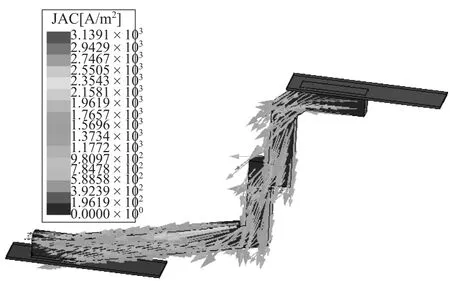

對電源進行編輯,可得到不同電源分配狀態下各管腳的電容分布,如圖3。由圖3可以看出管腳電平設置為高電平時的電容值大,管腳為低電平時的電容值小,多根相鄰高電平引線間的互電容效應十分明顯。本實驗產生的電容密度范圍為3.2920~1.4102×103C/m2。圖4為一根高電平引線(pin14)上交流場表面電流密度分布矢量圖。

圖3 各管腳的電容分布

圖4 交流場表面電流密度分布矢量圖

3 互連線信號完整性分析

通過對該封裝模型的同一根引線在100MHz和1GHz下進行參數三維的提取計算,在得到RLC值后,可對關鍵的信號線路(如時鐘和高速信號控制線)和最長信號線進行仿真分析,從而驗證頻率與信號完整性之間的關系。

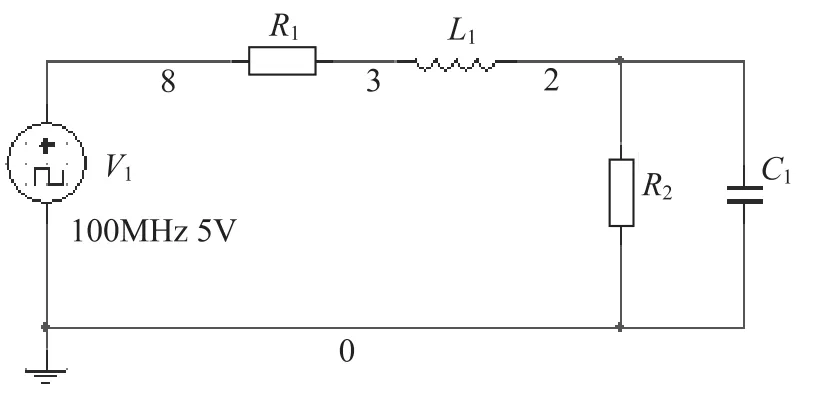

結合Multisim軟件,根據所提取的參數建立一個單根引線(pin14)的Ⅱ端口等效電路,其中R1為傳輸線的特性阻抗50Ω,R2、L1和C1分別為引線在相應頻率下提取的自電阻、自電容和自電感,V1為方波信號源,如圖5所示。

圖5 Ⅱ端口等效電路圖

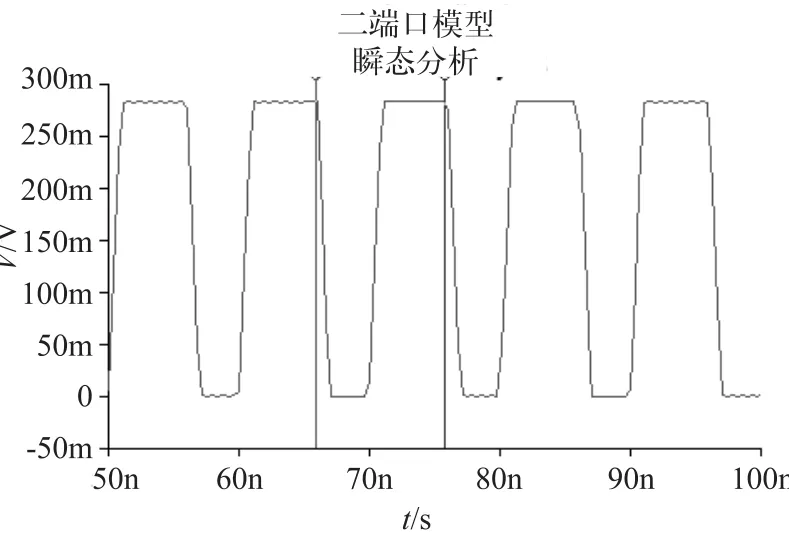

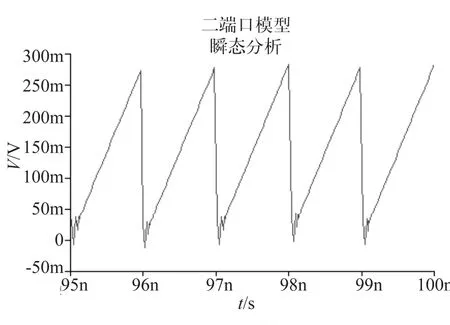

我們首先將信號源設為頻率為100MHz、電壓為5V的方波,通過示波器我們可以觀察節點2(node 2)處的輸出波形,如圖6所示。 接著我們將信號源頻率提高到1GHz,并將Ⅱ端口等效電路RLC變換到1GHz下的對應參數,輸出波形如圖7所示。

通過比對上述兩組實驗,可以明顯觀察到,100MHz的頻率下,信號沒有出現失真,而當信號頻率提高到1GHz時,信號出現明顯失真,既在1GHz的時鐘頻率下信號已無法完整地通過引線,此時必須要繼續優化設計,才能保證系統正常工作。

圖6 100MHz時信號的輸出波形

圖7 1GHz時信號的輸出波形

4 總 結

一般來說,在封裝的寄生參數中,電阻和電導對信號的影響較小,電容也只有pF級,而電感達到nH級,對信號的完整性影響作用較大,而這種影響在高頻狀態下更為明顯,所以要優化寄生參數尤其是電感的寄生參數。在IC產品設計初期,封裝設計者應同步進行IC封裝寄生參數的提取分析,對封裝外殼和引線管腳的電容、電感進行評估,盡量減少封裝設計的寄生參數,提高器件的工作性能。同時,芯片的引線和封裝引線位置一旦確定,通過縮短信號線長度或增加信號線布線寬度等傳統方法優化寄生參數的作用十分有限,因此可充分考慮封裝、PCB和芯片三者協同設計的方法和理念,不斷調整和優化封裝寄生參數,以期有效改進封裝的電特性并降低封裝成本及研發周期。

[1] 陸春榮.IC封裝中寄生參數的研究[J].中國學術期刊,2007,1-4.

[2] 尹文言.高速電路饋電接地系統的電源完整性和電磁兼容研究[J].中國學術期刊,2007.

[3] 周燕,孫玲,景為平. IC封裝中引線鍵合互聯特性分析[J].中國集成電路,2006(11):55-56.

[4] 龍樂.射頻系統封裝的發展現狀和影響[J].電子與封裝,2011,11(7):9-11.

[5] 徐煬,李茂松,陳鵬,黃大志.基于CQFP64線外殼的封裝寄生參數研究[J].微電子學,2008(4):507-509.

[6] Hai-Young, Lee. Wideband Characterization of a Typical Bonding Wire for Microwave and Millimeter-wave Integrated Circuits[J]. IEEE Trans. Microwave Theory and Techniques, 1995(43): 63-68.