一種基于FPGA的多DSP數據交換方法

呂衛國,沈發江,徐 偉

(江蘇自動化研究所,江蘇 連云港 222006)

隨著數字化時代的來臨,DSP的應用幾乎遍及整個電子領域,在很多需要實時數據處理的場合,即使采用目前最先進的DSP芯片,單片處理器也無法滿足大量數據實時處理的需求,往往需要多只DSP并行工作才能完成任務。例如在某水聲信號處理系統中,由于前端有48通道的模擬信號采集數據,要完成信號的頻率檢測及方位計算,單片DSP是無法實現的。根據估算,單片DSP(TMS320C6713)只能實時計算6路信號的頻率檢測(FFT),那么48路信號做頻率檢測至少就需要8片DSP,再加上其他的一些運算,必須構建多于8片DSP的處理系統才能完成系統的需求,針對以上需求,本文建立了具有11片DSP的多DSP并行處理系統。

TMS320C6713作為一款高性能的 32-位浮點DSP,具有較強的數據處理能力,并具有低功耗、低成本的優點,適用于精度要求較高且成本控制較嚴的信號處理場合。其主頻可達300MHz,指令周期3.3ns。為了加快處理速度,其內核采用4KB的一級程序緩存(Cache)、4KB的一級數據緩存、256KB的內部存儲器,可動態分配64KB作為程序和數據共享的二級緩存。憑借二級高速緩存及VLIW架構,最高運算速度可達 2400MIPS/1800MFLOPS。同時,其內部的 2個同步緩沖串口(McBsp)作為芯片對外接口,能夠配合芯片內部的EDMA通道,大大提高其數據處理的吞吐速度。雖然該芯片具有以上的優點,但也存在著外設端口單一,多芯片之間通信方式不夠靈活等缺點,這樣不利于多 DSP系統建立后數據處理任務的分配和協作。為了解決這一問題,就必須研究多DSP并行數據處理過程中數據在不同DSP之間的交換技術,以便實現多DSP并行處理系統中的運算負載平衡,進一步提高效率。

在本文討論的多DSP系統中,由于需要對外部輸入的數據進行并行處理,并且處理的流程也不固定。因此,各處理器之間必然會存在較多的數據交換,這就需要處理器之間具有較靈活的數據交換能力。TI公司的 TMS320C6713對外的數據接口主要有外部存儲器接口(EMIF)以及多通道同步串行接口(McBSP)。使用EMIF接口擴展存儲器來實現多DSP之間數據交換是一個比較普遍的思路,但是這只適用于DSP數量較少的情況,當DSP數量增加時,一方面會占用FPGA較多的RAM資源,提高了系統成本,另一方面由于并行高速數據傳輸,抗干擾能力較差,傳輸的可靠性降低。因此,在數據交換帶寬滿足系統要求的情況下,合理利用同步串行接口進行內部數據交換具有占用FPGA資源少,數據傳輸穩定可靠、控制較簡單等優點。基于網絡交換機的設計思想,文中設計了基于FPGA的串口數據交換機,將多片DSP均通過各自的McBSP連接到串口交換機,從而實現各只DSP之間數據的靈活交換。

1 多DSP并行處理系統的硬件設計

圖1是通用多DSP并行處理系統的結構框圖,由大規模可編程器件FPGA、多只DSP及外掛SDRAM存儲器、FPGA程序FLASH、DSP程序FLASH、千兆以太網口、調試串口、數據輸入及數據輸出接口等組成。FPGA作為系統的控制核心,內嵌了 CPU(Microblaze),用來管理系統的外部設備,多只DSP作為從設備,主要完成信號處理的任務。各只DSP的主機口都映射到CPU的空間中,作為CPU的從設備。CPU可以通過主機口來訪問各只 DSP的存儲空間和資源。以太網口主要實現與外部設備的通信。

圖1 通用信號處理模塊系統結構框圖

上述數據處理系統設計的核心是如何實現多只DSP之間的通信控制及數據交換,即如何建立起多DSP之間的數據通信通道,這也是本文討論的重點。數據交換的性能、數據交換的靈活性以及可靠性是決定數據處理性能至關重要的因素。

2 FPGA內部高速串行互聯的實現

2.1 概述

隨著 DSP器件技術的發展,同步串行接口(SPORT)作為標準外設出現在各種型號的DSP中,為DSP之間的通信提供了方便。每個同步串行接口均由發送器和接收器構成,一般有6根信號線組成,分別為發送數據(DT)、接收數據(DR)、發送時鐘(TCLK)、接收時鐘(RCLK)、發送幀同步(TFS)和接收幀同步(RFS)。

圖2 系統同步串行接口交換的連接框圖

使用時,在FPGA內部通過開關將不同DSP的同步串行接口的相應信號互聯,配置相關寄存器以確保收發時鐘、同步信號和數據幀長度的正確合理,便可以實現同步串行接口的數據通信。

2.2 同步串行接口交換機在FPGA中的實現

本系統FPGA選用Xilinx 公司的XC2V3000,是Virtex-II家族的成員之一,具有64*56個邏輯陣列,1728Kbit的塊RAM、18*18的嵌入式乘法器、4個時鐘管理器,最大達720個I/O口。

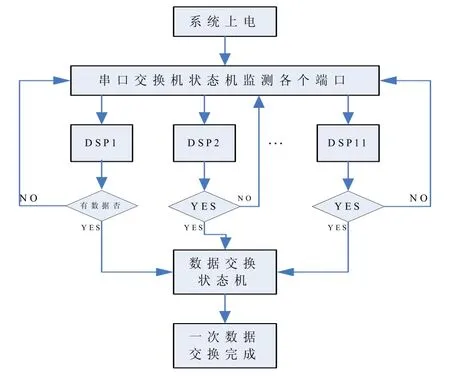

圖2所示為系統同步串行接口交換的連接框圖,串口交換機采用VHDL語言編寫,核心是一種狀態機,是系統多只DSP數據交換的核心部件。外部各片DSP都通過自己的同步串行接口連接到一個接口轉換模塊上,接口轉換模塊再鏈接到串口交換機上。接口轉換模塊主要完成同步串行接口數據的串并轉換或者并串轉換,以便和串口交換機內部進行數據通信。

圖3 串口交換機工作流程圖

串口交換機內部主要包括三個功能模塊:數據接收模塊、數據檢測和搬移模塊(串口交換機核心),以及數據發送模塊。數據接收模塊完成串行端口數據的串并轉換并將數據寫入到雙端口的緩存中;數據檢測及搬移模塊完成數據包幀頭的解析以及數據在不同串行端口緩存之間的數據搬移;數據發送模塊完成數據從雙端口緩存的讀取及數據的并串轉換,并發送到相應的串行端口。

圖4給出了串口交換機內部結構示意圖。由于所有 TMS320C6713共有兩個高速串行端口,其中串行端口0的發送和接收端都經過雙端口RAM掛接在交換機上,而串口1的發送幀標志管腳和發送數據管腳設置為通用的GPIO管腳,作為交換機的控制和狀態信號。其中,串口1的發送幀標志管腳作為DSP數據交換時的請求信號;串口1的發送數據管腳作為當前該片DSP串口0狀態指示信號。從圖4中可以看出,當DSP1要發送數據給DSP2時,DSP1先檢測其DX1的狀態,當DX1允許時,則通過FSX1向串口交換機發出數據交換請求,串口交換機接收到數據請求后,查詢DSP2的DX1狀態,當其DX1允許時,則開始把DSP1串行端口0的接收緩存(DPRAM1)的數據搬移到DSP2串行端口0的發送緩存(DPRAM4)中,通過串行端口發送到DSP2中,完成本次數據通信;以此類推,其他DSP之間進行數據交換時也采取類似的過程。

圖4 串口交換機內部結構示意圖

3 串口交換機軟件實現

本設計中的軟件基于TI公司CCS開發環境,開發環境提供了DSP芯片支持庫CSL,縮短了軟件的開發周期。具體配置和收發程序如下。

串口交換機的數據包格式為:

其中,0x5555555D為發送數據幀頭。DST是目的節點號,SRC是源節點號,CNT為發送數據長度,中間四個32位字為保留字,最后是數據區。

串口交換機初始化:

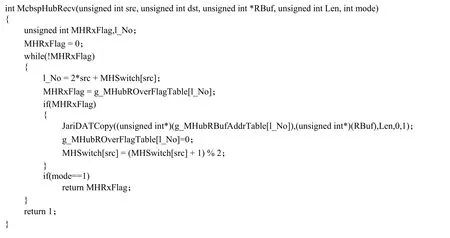

串口交換機使用串口0作為數據交換的通道,大部分參數配置都參考默認配置,需要注意的兩個地方是:在對串口0的配置中將PCR(串口控制寄存器)寄存器的 FSXM 位設置為 0(MCBSP_PCR_FSXM_EXTERNAL),即發送由外部提供幀信號;在對串口1的配置中,將 PCR寄存器的 RIOEN為設置為 1(MCBSP_PCR_RIOEN_GPIO),即將FSR和CLKR管腳作為GPIO使用,用于觸發串口0的數據發送。初始化代碼見函數McbspHubInit。

串口交換機數據接收采用雙緩沖EDMA傳輸鏈結構。EDMA控制器提供了一種靈活的傳輸機制,稱為“連接”(linking),可以將不同EDMA傳輸參數組連接起來,組成一個傳輸鏈,為同一個通道服務。在傳輸鏈中,一個傳輸的結束會導致自動從參數RAM中裝載下一次傳輸需要的事件參數。在EDMA鏈接收完數據后,會相應的置上接收標志,當用戶程序需要接受相應節點的數據時,只需判斷相應節點的數據標志位,如果標志位準備好,則應用程序可以在相應的緩沖區讀取數據,否則,等待數據接收好標志,直到標志已好,接收數據。接收函數代碼見函數McbspHubRecv。

4 結束語

基于串口進行數據交換的多DSP并行綜合處理平臺作為一種通用的數據處理平臺,在提供高性能的信號處理能力的同時,可實現多片DSP之間的較為有效的數據交互,實現過程簡單、易行,具有連線簡單、通信速度快、可靠性高等特點,是一種解決多片DSP并行處理與信息交互的有效方法。該方法在某型信號處理機中得到應用。實際應用證明該方法簡單、可靠,滿足了系統的數據實時交換要求。

[1]TMS320C6713BGDP300 data sheet [M].Texas Instrument,2005.

[2]Virtex-II Platform FPGAs complete data sheet[M].Xilinx,2007.

[3]黃飛,喬純捷,王躍科.網絡互聯型多DSP并行處理系統設計[J].計算機工程,2007,23(33):230-232.

[4]夏軍營,喬純捷,王剛.基于以太網接口的多DSP監控技術研究[J].計算機測量與控制,2007,15(7):913-915.

[5]李方慧,王飛,何佩琨,等.TMS320C6000系列 DSP原理與應用 [M].2版.北京:機械工業出版社,2000.