基于DSP Builder的偽隨機序列發生器設計及FPGA實現

楊 東,王建業

(空軍工程大學 導彈學院,陜西 三原 713800)

基于DSP Builder的偽隨機序列發生器設計及FPGA實現

楊 東,王建業

(空軍工程大學 導彈學院,陜西 三原 713800)

簡要分析了偽隨機序列中應用廣泛的m序列,Gold序列及平衡Gold碼的概念、原理和應用。提出了一種基于Altera的DSP Builder工具箱的偽隨機序列產生器設計方法,并通過設計實例,說明這種方法在簡化設計難度、提高設計速度和靈活性等方面的優點和應用價值。并提出了其仿真和FPGA實現的基本方法。

DSP Builder;m序列;Gold序列;平衡 Gold碼

在擴展頻譜通信系統中,偽隨機序列起著十分關鍵的作用。在直接序列擴頻系統的發射端,偽隨機序列擴展信息序列的頻譜,在接收端,偽隨機序列將擴頻信號恢復為窄帶信號,進而完成信息的接收。因此,偽隨機序列產生器是擴頻系統的核心單元。偽隨機序列具有理想隨機序列的性質,易于產生,具有隨機性和盡可能長的周期,使第三方難以從擴頻碼的一小段去重建整個碼序列,具有雙值自相關特性等。理想隨機序列在工程上無法應用,實際上所用的均為偽隨機序列。偽隨機序列主要有:m序列、Gold序列、R-S碼、復合碼以及混沌序列等。

1 m序列基本原理

m序列又稱最長線性反饋移位寄存器序列,它具有平衡性、移位可加性、游程特性及很好的相關性能,廣泛應用于直接序列擴頻系統。一個典型的m序列組成如圖1所示。

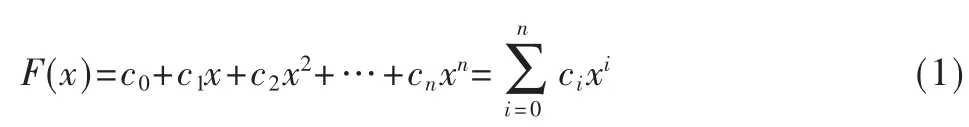

由反饋移位寄存器產生的序列,取決于反饋系數,對于此反饋移位寄存器,反饋邏輯為:

上式即為序列的特征多項式。(cn,cn-1,…,c0)為反饋系數,其取值為“0”或“1”,“1”表示該反饋支路連通,“0”表示該反饋支路斷開。m序列的反饋系數與其寄存器級數對應關系可由查表獲得,據此,便可以構造任意級m序列。

2 Gold序列基本原理

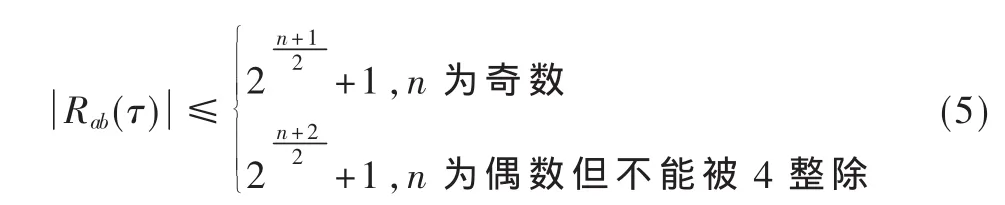

擴頻通信中,不僅要求偽隨機序列具有隨機性好、周期長、不易被敵方檢測等特性,而且要求有盡可能多的可用的偽隨機序列,以便進行多址通信和組網運用。Gold序列便具有此特性。GOLD R指出:“給定移位寄存器級數為n時,總可以找到一對互相關函數值最小的碼序列,采用移位相加的方法構成新碼,其互相關旁瓣都很小,并且自相關函數和互相關函數都是有界的”。這一對互相關函數最小的序列稱為m序列優選對,是指在m序列集中,其互相關函數最大值的絕對值小于某個值的兩個m序列。設序列{a}是對應于n階本原多項式 f(x)產生的 m序列,序列{b}對應于 n階本原多項式 g(x)產生的 m序列,當它們的互相關函數值 Rab(τ)滿足不等式(2):

則由f(x)和 g(x)產生的m序列{a}和{b}構成一優選對。m序列優選對可由查表獲得。

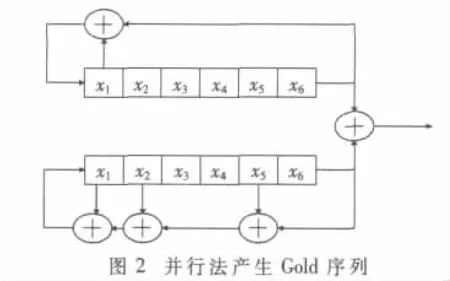

Gold序列的產生方式有并行和串行兩種方式。由兩個碼長相等、碼時鐘速率相同的m序列優選對模2和構成Gold序列的方法為并行方式,每改變兩個m序列相對位移就可得到一個新的Gold序列。將產生兩優選對m序列的本原多項式相乘,展開后,按此多項式構成2n級Gold序列產生器的方法為串行方式。以n=6級Gold序列產生器為例,其優選對m序列的本原多項式為:

并行方式如圖2所示。

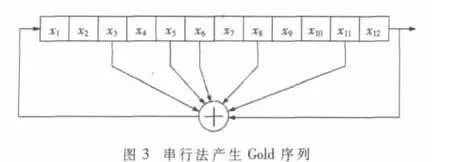

由于:

可得串行方式如圖3所示。

Gold序列族中任意兩個Gold序列滿足如下的互相關特性:

這一特性使得Gold序列中的任意碼都可以作為地址碼,因而大大增加了地址碼的數量。

3 平衡Gold碼

擴頻通信系統中,對系統質量影響因素之一就是偽碼的平衡性(即序列中的“0”、“1”均勻性),平衡碼具有更好的頻譜特性。在DS系統中,碼的平衡性對載波抑制有密切的關系,碼不平衡會造成載波泄漏,破壞擴頻通信系統的保密性、降低其抗偵破能力。序列中“1”和“0”的碼元數量相差等于1時為平衡碼,而大于 1時為非平衡碼。為尋找平衡Gold碼,首先要確定特征相位,當序列處于特征相位時,序列每隔一位抽樣后得到的序列與原序列完全一樣。設序列特征多項式f(x)為n級線性移位寄存器產生m序列的本原多項式,序列的特征相位由g(x)/f(x)的比值確定。g(x)計算如下:

d(x)的階數為 n,c(x)的階數小于 n,長除后的結果為 1+d1x+d2x+…的形式。

因此,處于特征相位上的序列{a}和{b},以{a}序列為參考序列,移動{b}序列,使之第一位為“0”,對應于{a}序列第一位為“1”。兩序列相加后得到的序列必定是平衡Gold碼。那么,移動{b}序列的第一位為“0”的序列的前k位為相對相位。

產生平衡Gold碼的一般步驟為:

(1)選一參考序列,其本原多項式為 fa(x),求出其生成多項式ga(x);

(2)由 G(x)=ga(x)/fa(x),求出序列多項式,使序列{a}處于特征相位上;

(3)求位移序列{b},使位移序列的初始狀態的第一位為“0”,即處于相對相位,對應于序列{a}第一位“1”;

(4)將處于特征相位的序列{a}和處于相對相位的序列{b}模2加,就得到平衡Gold序列。

4 利用DSP Builder設計偽隨機序列發生器

4.1 DSP Builder介紹

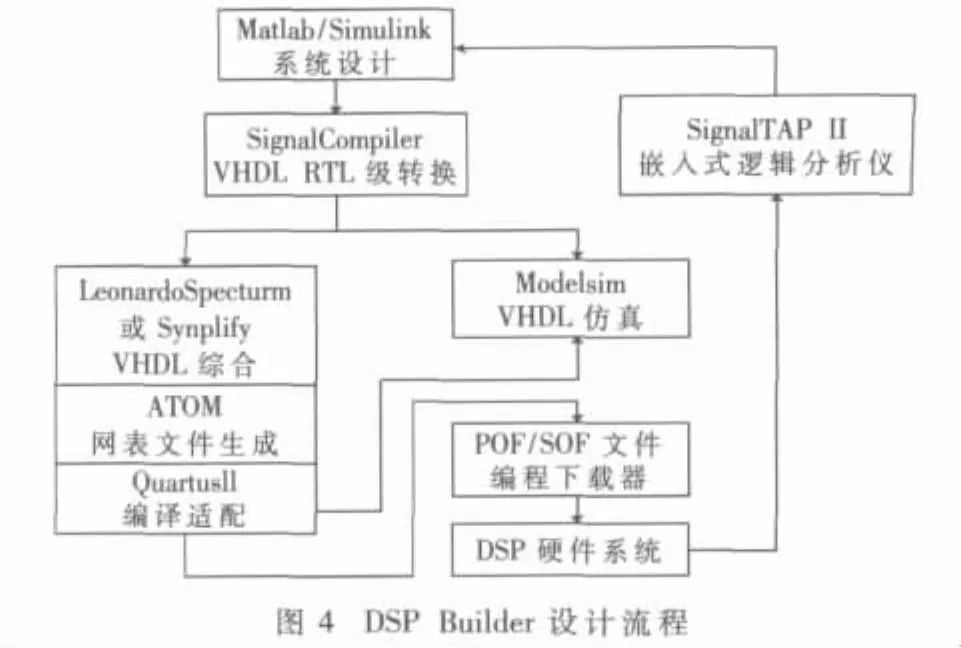

Matlab工具一般作為DSP算法的建模和基于純數學的仿真,其數學模型無法為硬件DSP應用系統直接產生實用程序代碼,仿真測試結果也僅僅是基于數學算法結構。而傳統的FPGA基于硬件描述語言(HDL)的設計由于需要考慮FPGA的硬件延時、VHDL的遞歸算法的銜接、補碼運算和乘積結果截取等問題,相當繁雜。DSP Builder是美國Altera公司推出的一個面向DSP開發的系統級工具,為Matlab的一個Simulink工具箱,以幫助設計者完成基于FPGA的DSP系統設計的整個流程,它充分體現了現代電子技術自動化開發的特點與優勢。基于DSP Builder的設計流程如圖4所示。

4.2 利用Simulink建立各序列模型

DSP Builder設計中首先是在Matlab/Simulink中進行設計輸入,即在Matlab的Simulink環境建立一個MDL模型文件,用圖形方式調用Simulink庫中的模塊,構成系統級或算法級設計框圖(或稱Simulink建模)。建立的m序列、Gold序列和平衡Gold序列產生器模型如圖5所示。

圖5中主要模塊功能為:

(1)The Delay block:延遲模塊,起延時作用,在硬件上可以采用寄存器來實現。此模塊可接受任意類型的數據輸入。

(2)The Logical Bit Operator block:位邏輯運算模塊,能實現單個位輸入數之間的邏輯運算,能實現多種功能:AND,NAND,OR,XOR,NOR,NOT。

(3)SignalCompiler:DSP Buider的核心,將 Simulink設計轉換成可綜合的RTL級VHDL代碼,并產生各種測試和仿真矢量文件。

(4)The Testbench block:通過測試平臺模塊,可自動運行Modelsim,對比仿真結果。

5 各模型仿真及FPGA實現

5.1 Simulink模型系統級仿真

Simulink中進行的仿真屬于系統驗證性質的,是對mdl文件進行的仿真,而對VHDL代碼進行仿真則需要使用ModelSim,如圖6所示。

5.2 使用ModelSim進行RTL級仿真

ModelSim是一個基于單內核的Verilog/VHDL混合仿真器,是Mentor Graphic的子公司ModelTechnology的產品。主要用于對生成的RTL級VHDL代碼進行功能仿真。 對應圖 5中(b)、(d),經過 ModelSim功能仿真的波形如圖7所示。

5.3 FPGA實現

在Matlab/Simulink中對設計模型進行編譯,再用DSP Builder的Signal Compiler工具直接生成QuartusⅡ工程文件,再調用QuartusⅡ完成綜合、網表生成和適配,直至完成FPGA的配置下載。本設計使用的FPGA芯片是Altera公司的Cyclone系列芯片EP2C35F672C6。

設計表明,在利用FPGA進行偽隨機序列發生器設計時,利用DSP Builder能簡化設計難度,加快設計速度,靈活選取精度,實現優化設計;DSPBuilder與QuartusⅡ軟件的融合,實現了自頂向下的設計流程,充分顯示了現代EDA開發的特點與優勢。然而,該方法的應用在精度、速度和器件選擇等方面也受到一定限制。

[1]何世彪,譚曉衡.擴頻技術及其實現[M].西安:電子工業出版社,2006.

[2]潘松,黃繼業,王國棟.現代 DSP技術[M].西安:西安電子科技大學出版社,2003.

[3]楮振勇,齊亮,田紅心,等.FPGA設計及應用.西安電子科技大學出版社,2006.

[4]張洪潤,張亞凡.FPGA/CPLD應用設計200例[M].北京:北京航空航天大學出版社.2007.

A DSP builder-based pseudo-random sequence and its FPGA implementation

Yang Dong,Wang Jianye

(The Missile Institute,Air Force Engineering University,Sanyuan 713800,China)

This text synopsisly analyzed the concept,principle and application of the m sequence,the Gold sequence and the equilibrium Gold code in the pseudo-random sequence.It put forward a designing way of pseudo-random sequence which based on the tool box of DSP builder in the Altera,and explained the advantages and values on simplifying the designing difficulty and advancing the designing speed and vivid through a solid example.It also put forward the basic method of imitating and carring out with FPGA.

DSP builder;m sequence;Gold sequence;equilibrium Gold code

TP331.1

A

1674-7720(2011)02-0096-04

2010-01-16)

楊東,男,1986年生,碩士研究生,主要研究方向:數字專用集成電路設計。