基于VHDL的圖像傳感器TCD1206的驅動設計

崔朋朋,劉艷萍,楊玉芝

(河北工業大學 信息工程學院,天津 300401)

基于VHDL的圖像傳感器TCD1206的驅動設計

崔朋朋,劉艷萍,楊玉芝

(河北工業大學 信息工程學院,天津 300401)

介紹圖像傳感器TCD1206的主要特點、結構原理、引腳功能,并詳細分析其驅動時序。通過研究采用VHDL實現TCD1206驅動脈沖的方法及邏輯設計原理,完成了驅動脈沖的VHDL程序設計和時序仿真。仿真結果證明了該驅動電路的可行性。

TCD1206;線陣CCD;驅動時序;VHDL

電荷耦合器件CCD(Charge Couple Device)是集光電轉換、電荷儲存、電荷轉移為一體的新型光電傳感器件。該器件的主要功能是將光學圖像轉換為電信號。當對其施加特定時序脈沖時,其存儲電荷能在CCD內作定向移動,從而實現自掃描,輸出電壓信號的大小與CCD單元存儲的電荷多少成正比,CCD單元存儲電荷多少與光的強度和CCD單元光積分時間成正比。與傳統的光電傳感器相比,CCD圖像傳感器具有輸出噪聲小,動態范圍大,光譜響應范圍寬,分辨率高,輸出信號線性度好,功耗低,體積小,壽命長等優點[1-2]。而CCD應用的關鍵就是獲取驅動脈沖,這里分析線陣CCDTCD1206的工作原理和對驅動時序的要求,在此基礎上設計合理的脈沖產生方案。該設計采用復雜可編程邏輯器件CPLD作為硬件設計平臺,通過超高速硬件描述語言VHDL描述驅動方案,采用Altera公司的仿真軟件QUARTUS II對其驅動脈沖進行仿真。

1 TCD1206的主要特點

TCD1206是一款高靈敏度、低暗電流、2 160像元的雙溝道線陣CCD圖像傳感器。由2 236個PN結光電二極管構成光敏元陣列,其中前64個和后12個是用作暗電流檢測而被遮蔽的,中間2 160個光電二極管是曝光像敏單元,每個光敏單元的尺寸為長 14 μm、高 14 μm,中心距亦為14 μm。光敏元陣列總長為30.24 mm。

TCD1206的主要特性有[3]:1)光敏像元數為2 160像元;2)像敏單元為:14 μm×1 414 μm(相鄰像元中心距為 14 μm);3)光譜范圍為250~1 100 nm;4)光敏區域采用高靈敏度 PN結作為光敏單元;5)時鐘為二相(5 V);6)內部電路包含采樣保持電路,輸出預放大電路;7)采用22引腳DIP封裝。

2 TCD1206的結構原理和引腳功能

2.1 結構原理

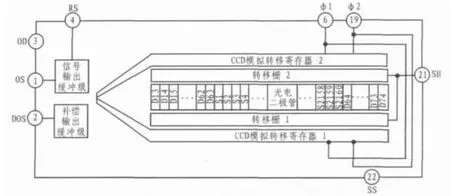

TCD1206是二相電極的雙溝道線型CCD,其結構原理如圖1所示。中間一排是由多個光敏二極管構成的光敏陣列,有效單元為2 160位,其作用是接收照射到CCD硅片的光,并將其轉化成電荷信號,光敏元兩側是存儲其電荷的MOS電容列—存儲柵。MOS電容列兩側是轉移柵電極SH。轉移柵的兩側為CCD模擬移位寄存器,其輸出部分由信號輸出單元和補償單元構成[4]。

圖1 TCD1206的結構原理圖

2.2 引腳功能

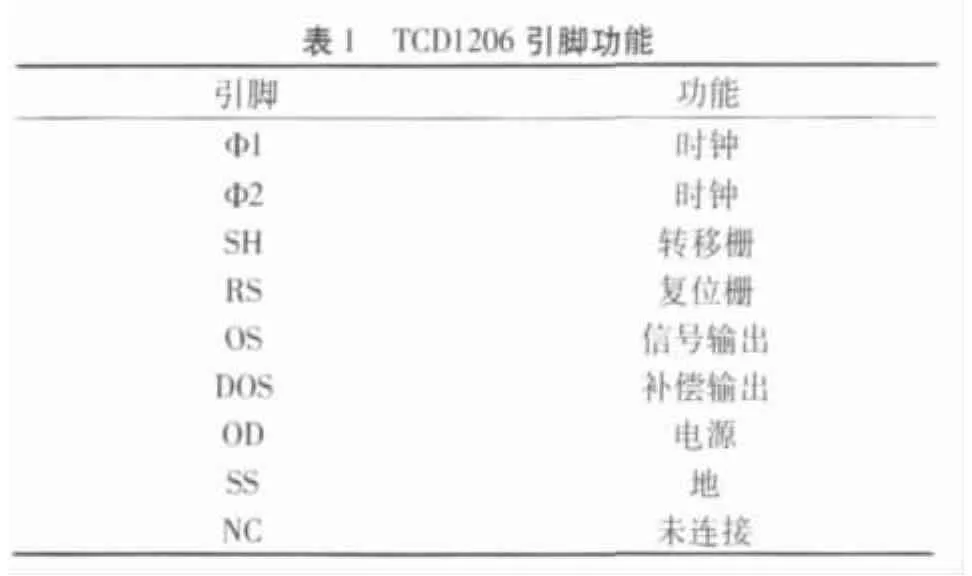

TCD1206器件采用DIP封裝,各引腳功能如表1所示。

?

3 驅動時序及驅動設計

3.1 驅動時序分析

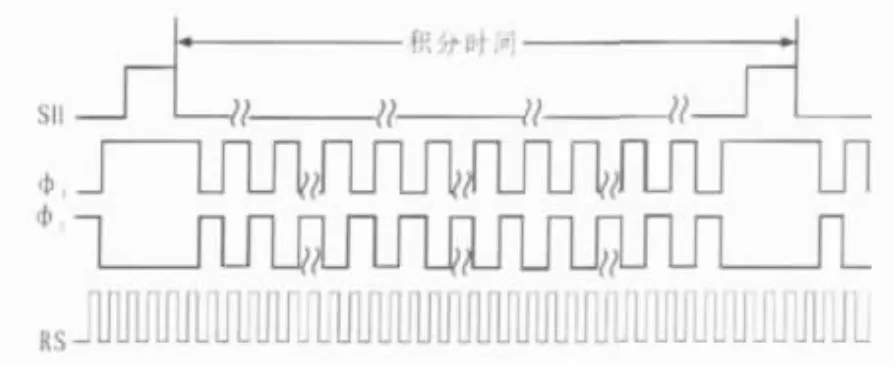

TCD1206在圖2所示的驅動脈沖作用下工作[5-6]。當SH脈沖高電平到來時,φ1脈沖為高電平,其下形成深勢阱,同時SH的高電平使φ1電極下的深勢阱與MOS電容存儲勢阱溝通。MOS電容中的信號電荷包通過轉移柵轉移到模擬移位寄存器的φ1電極下的勢阱中。當φSH由高變低時,φSH低電平形成的淺勢阱將存儲柵下的勢阱與φ1電極下的勢阱隔離開。存儲柵勢阱進入光積分狀態,而模擬移位寄存器將在φ1與φ2脈沖的作用下驅使轉移到φ1電極下的勢阱中的信號電荷向左轉移,并經輸出電路由OS電極輸出。DOS端輸出補償信號。

圖2 TCD1206驅動脈沖波形圖

由于結構上的安排,OS端首先輸出13個虛設單元信號,再輸出51個暗信號,然后才連續輸出S1到S2160的有效像素單元信號。第S2160信號輸出后,又輸出9個暗信號,再輸出2個奇偶檢測信號,以后是空驅動。空驅動的數目可以是任意的。由于該器件是兩列并行分奇偶傳輸的,所以在一個SH周期中至少要有1 118個φ1脈沖。RS為復位級的復位脈沖,復位一次輸出一個信號。

3.2 驅動電路設計

驅動電路的作用是給CCD提供正常工作所需要的邏輯時序脈沖和偏置工作電壓,并在CCD的輸出端把光電轉換得到的電荷量轉變成電壓量輸出。驅動脈沖信號的波形、相位、前后沿時間等對器件工作有很大影響。

為了保證CCD工作穩定可靠,必須設計符合CCD正常工作要求的時序脈沖和驅動控制電路,驅動控制脈沖與CCD良好配合,才能充分發揮CCD的光電轉換、電荷存儲和電荷轉移等功能。不同型號的CCD要求的工作參數不同,很難設計一種驅動控制電路同時滿足多種CCD工作需要,即使是相同像元數的CCD器件,若型號不同也不具有互換性。

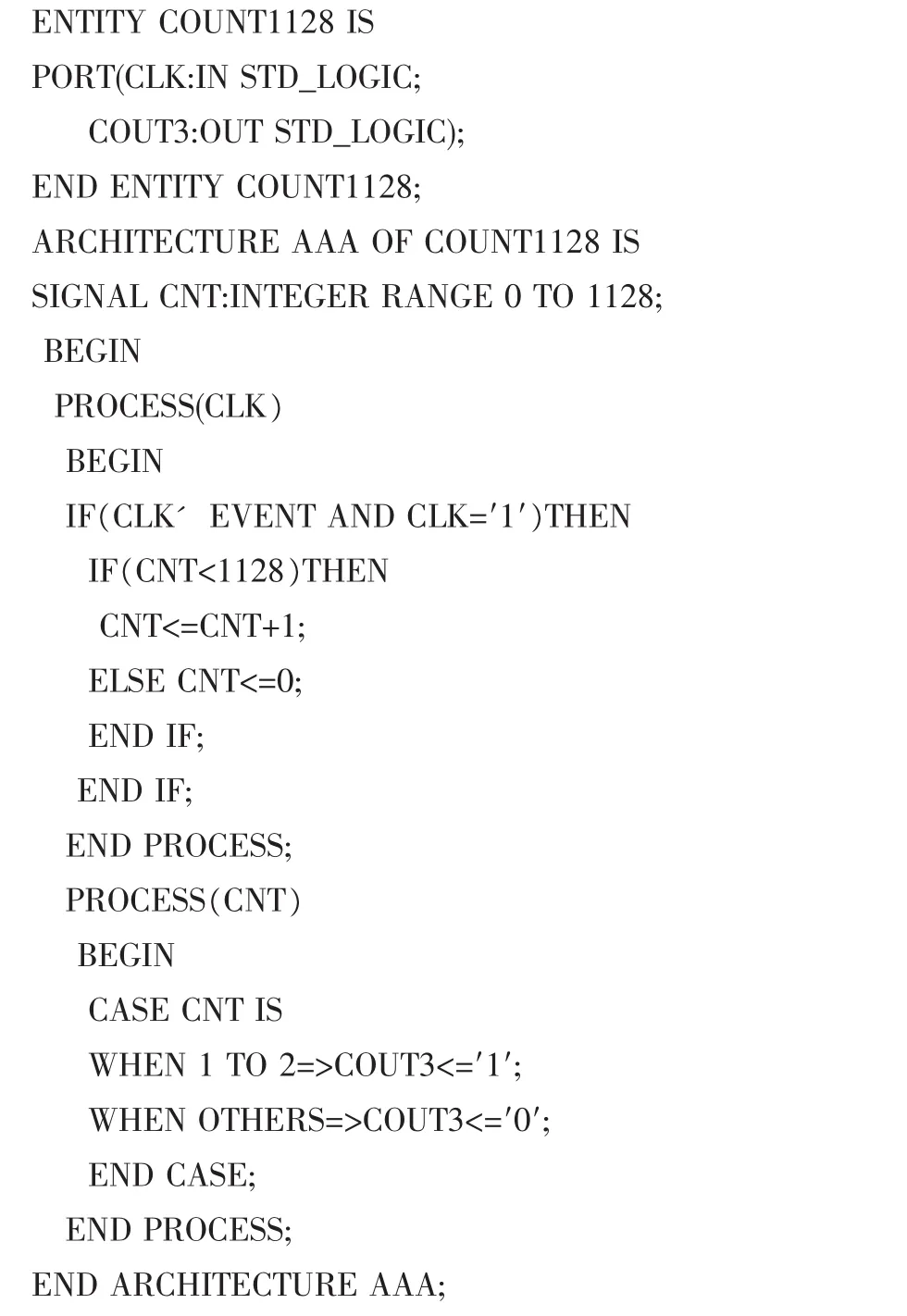

TCD1206傳感器的驅動脈沖都為周期性方波,但周期和占空比不同。其4路驅動脈沖之間需要滿足特定的時序關系:根據驅動脈沖時序圖可知在1個SH周期中至少有1 118個φ1脈沖。即TSH>1 118T1,T1為驅動脈沖φ1的周期。這里選擇TSH=1 128T1。在SH為高電平期間,要求 φ1與φ2有一個大于SH=l持續時間的寬脈沖,這是由于此時像元中的電荷正在向兩列寄存器中轉移,如果在此期間φ1與φ2有上升或下降沿出現,則會造成電荷轉移不完全的情況。時鐘脈沖 φ1,φ2頻率的最大值是1 MHz,典型值是0.5 MHz。復位脈沖RS頻率的最大值是2 MHz,典型值是1 MHz。本設計中都選用典型值。而且 φ1、φ2必須反相,占空比1:1;SH的高電平脈沖寬度要小于φ1,φ2;RS與 CLK時鐘的占空比為 1:4。

3.2.1 原理圖設計

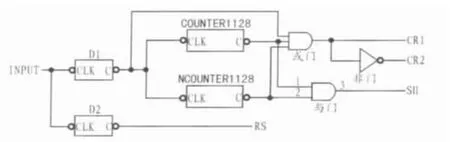

確定SH、φ1、φ2和RS的參數后,則可根據它們之間的時序關系設計硬件邏輯圖,如圖3所示。

圖3 TCD1206驅動電路邏輯圖

本設計利用CPLD作為硬件設計平臺,它具有較高的靈活性,電子電路設計完成后,如果需修改時序邏輯,只需重寫CPLD內部邏輯電路即可。因此,CPLD非常適合用于設計CCD驅動電路[7-8]。

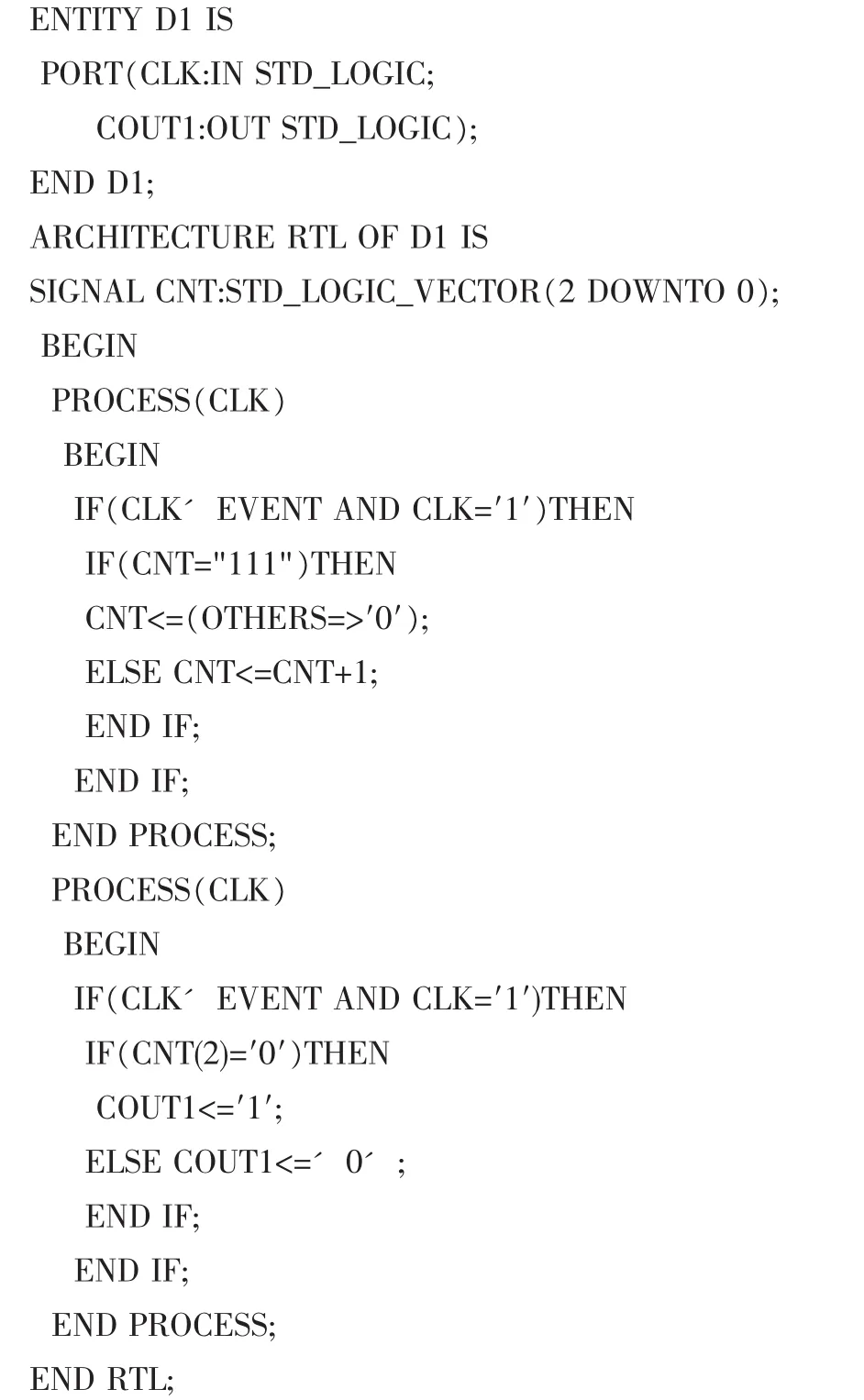

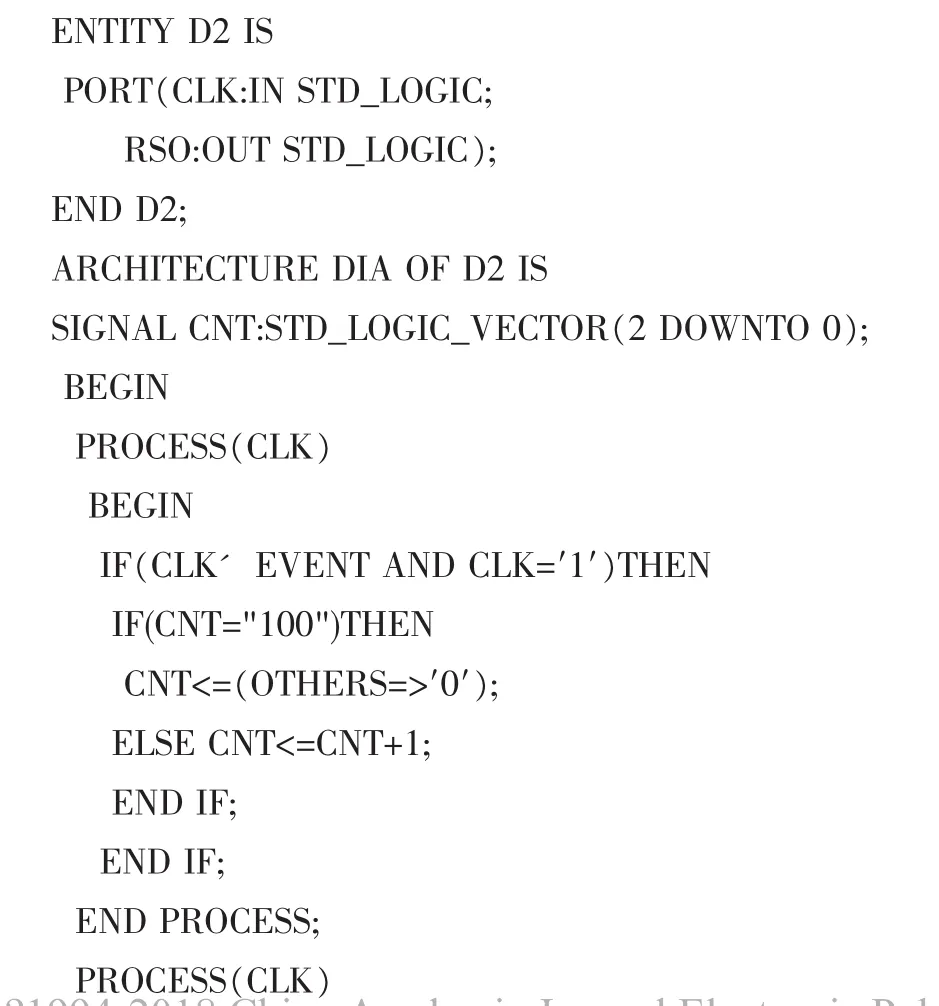

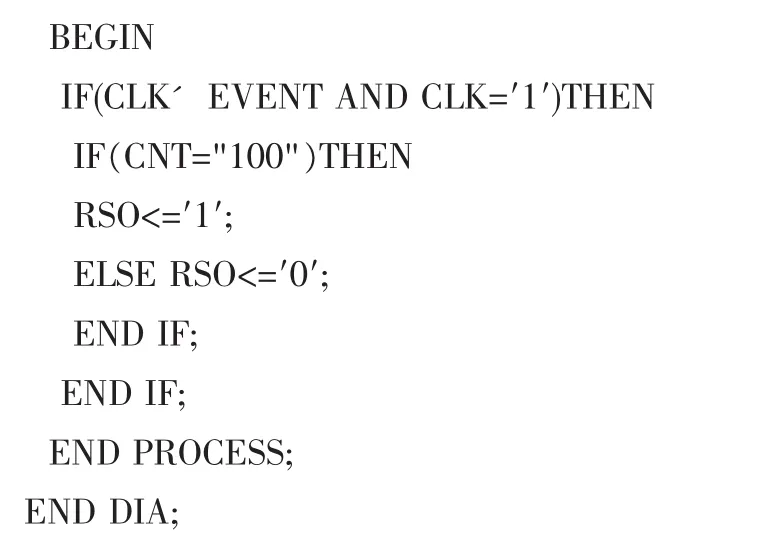

各個模塊的設計采用VHDL語言描述。采用4 MHz的時鐘CLK作為輸入的時鐘,D1模塊用于將時鐘信號進行8分頻,將4 MHz的時鐘頻率分成0.5 MHz。D2模塊是將時鐘頻率分成 1 MHz,占空比為 1:4。COUNTER1128模塊和NCOUNTER1128模塊分別是上升沿和下降沿計數,計數范圍在0~1128之間循環,在前兩個時鐘為高電平,其余時間都為低電平。

電路實現是先用Dl模塊將4 MHz的時鐘頻率分成0.5 MHz,用0.5 MHz的脈沖作為COUNTER1128和NCOUNTER1128的輸入端,將COUNTER1128和NCOUNTER1128的輸出相與,輸出結果就是SH,將D1和COUNTER1128以及NCOUNTEER1128的輸出進行邏輯或,則得到φ1,再將φ1反相,得到φ2,由D2模塊可直接得到RS。

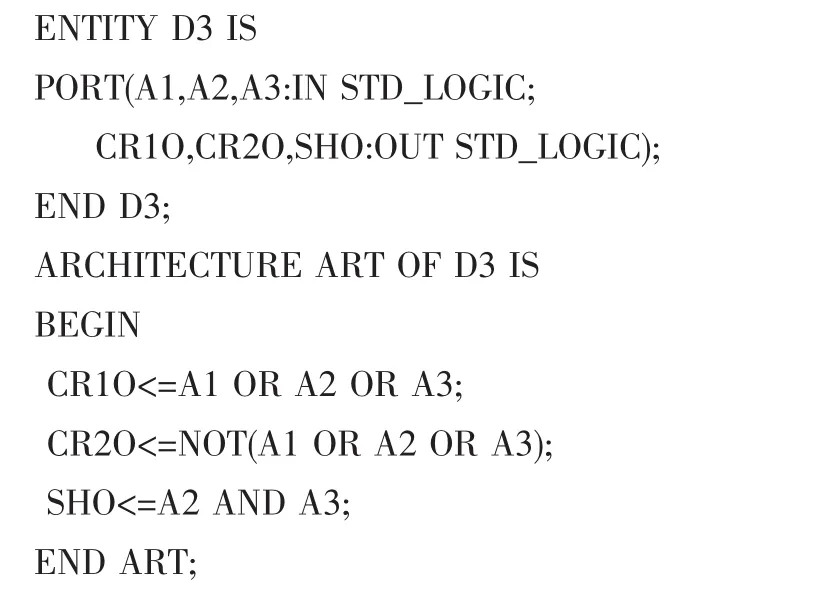

3.2.2 模塊電路的VHDL設計

每個模塊的VHDL設計都包括如下部分:1)定義所需的庫函數;2)定義輸入、輸出端口;3)對設計所需預置數初始化;4)相關功能的實現語句[9-10]。CCD驅動程序主體部分設計如下:

1)D1模塊的8分頻設計

2)D2模塊與CLK占空比為1:4的分頻設計

3)計數器COUNTER1128設計

4)D1模塊、COUNTER1128模塊與 NCOUNTER1128模塊綜合后產生φ1,φ2,SH 設計

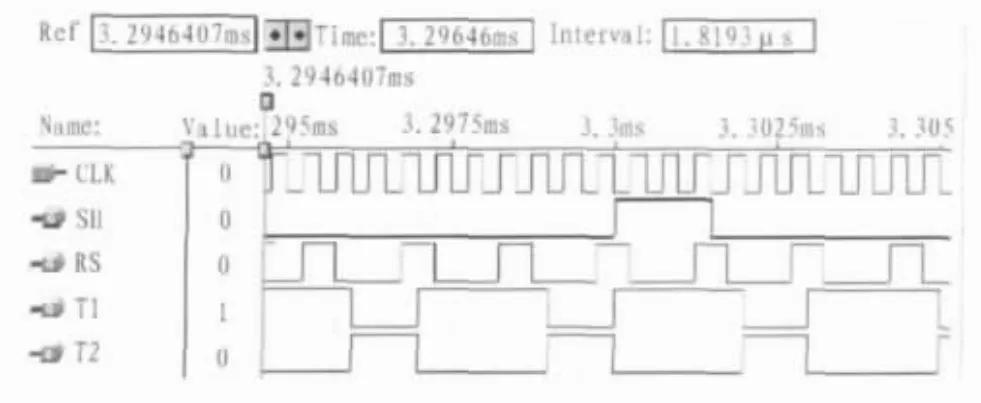

4 設計結果仿真

圖4是在Altera公司的QUARTUS II開發系統中仿真的波形,從圖中可以看出,產生的4路驅動脈沖完全滿足TCD1206所需的時序脈沖,達到驅動要求。

圖4 CCD驅動時序仿真波形

5 結束語

VHDL是一種自上向下設計的硬件描述語言,同時又具有高級語言的特性,這使得用這種硬件描述語言設計的邏輯功能比較容易實現。同時VHDL語言具有很好的可重用性和可移植能力,能夠減輕工作量。利用VHDL設計整個傳感器的驅動,并與硬件原理圖相結合,不同于以往以單純的硬件設計實現,這樣不僅利于修改而且設計周期短。因此,基于VHDL對TCD1206驅動電路的設計是一種較實用的設計方案。

[1]Wang Qingyou.Study on vibration measurement with the use of CCD[J].SPIE,1999(3):339-341.

[2]唐賢遠.傳感器原理及應用[M].北京:電子工業出版社,2000.

[3]蔡文貴.CCD技術及應用[M].北京:電子工業出版社,1992.

[4]劉文耀.數字圖像采集與處理[M].北京:電子工業出版社,2007.

[5]王慶有.CCD應用技術[M].天津:天津大學出版社,2002.

[6]孟立凡.傳感器原理及應用[M].北京:電子工業出版社,2007.

[7]常丹華.基于CPLD技術的CCD驅動時序產生方法[J].儀表技術與傳感器,2001(3):26-28.

[8]姜雪松,吳鈺淳,王 鷹,等.VHDL設計實例與仿真[M].北京:機械工業出版社,2007.

[9]劉愛榮,王振成.EDA技術與CPLD/FPGA開發應用簡明教程[M].北京:清華大學出版社,2007.

[10]侯伯亨,顧 新.VHDL硬件描述語言與數字邏輯電路設計[M].西安:西安電子科技大學出版社,2004.

Driver design of image sensor TCD1206 based on VHDL

CUI Peng-peng,LIU Yan-ping,YANG Yu-zhi

(School of Information Engineering,Hebei University of Technology,Tianjin300401,China)

The main features,structural principle,pin functions of TCD1206 are introduced and its drive cycle time is analysed particularly.Through researching the implementation of image sensor TCD1206 driver pulse by VHDL and logical design principle,the VHDL programming of drive pulse and the timing simulation of waveform are completed.The simulation result shows that the driving circuit is feasible.

TCD1206;linear CCD;drive cycle;VHDL

TP18

A

1674-6236(2010)01-093-04

2009-05-08 稿件編號:200905013

崔朋朋(1984—),女,河南平頂山人,碩士。研究方向:通信測控技術。