基于MATLAB-FDATool的數字濾波器FPGA實現

鄭州輕工業學院計算機與通信工程學院 李祖賀 陳慶南

基于MATLAB-FDATool的數字濾波器FPGA實現

鄭州輕工業學院計算機與通信工程學院 李祖賀 陳慶南

隨著數字技術的不斷發展,數字信號處理技術(DSP,DigitalSignalProcessing)已飛速擴展到移動通信、雷達衛星通信、多媒體系統、圖像識別與處理系統等諸多應用領域。不同領域對功能實現、性能指標與成本方面的要求也在不斷增加。DSP處理器(如TI的TMS320系列)曾經是系統核心器件的唯一選擇,但由于當今DSP應用市場的迅速變化,它已不能滿足全部的要求。隨著現代FPGA(FieldProgrammableGateArray,現場可編程門陣列)的出現,彌補了DSP處理器的一些不足。用FPGA來實現數字信號的處理就很好地解決了并行性和速度的問題,而且由FPGA構成的DSP系統非常易于修改、測試和升級。FPGA已經廣泛地應用于信息通信、自動控制等諸多領域。但是傳統的DSP開發者只能直接使用VHDL或VerilogHDL語言進行FPGA的設計,因而開發難度較大。

現在已經出現了許多新的基于FPGA的DSP開發工具,工作效率大為提高。本文就是在這種背景下,以在語音、圖像處理和數字通信等各種系統中起作用的數字濾波器為切入點,嘗試利用MATLAB信號處理工具箱下的濾波器設計工具FDATool進行數字濾波器的設計及FPGA實現。

一、MATLAB-FDATool及數字濾波器基礎

FDATool(FilterDesign&AnalysisTool)是MATLAB軟件信號處理工具箱里的濾波器設計分析工具,它幾乎可以設計所有的常規濾波器,包含FIR和IIR的各種設計方法,操作簡單方便。

FDATool設計界面可分為2大部分:一部分是Design Filter,位于界面下半部,用于設置濾波器的各項設計參數;另一部分則是特性區,位于界面的上半部,用于顯示濾波器的各項特性,如幅頻、相頻特性等,且在設計過程中實時顯示,方便參數的選擇。DesignFilter部分主要分為:FilterType(濾波器類型)選項,DesignMethod(設計方法)選項,FilterOrder(濾波器階數)選項,FrenquencySpecifications選項,MagnitudeSpecifications選項,WindowSpecifications選項。

數字濾波器是輸入輸出均為數字信號,經過一定運算關系改變輸入信號所含頻率成分的相對比例或者濾除某些頻率成分的器件。數字濾波器根據其沖激響應函數的時域特性,分為無限長沖激響應(IIR)和有限長沖激響應(FIR)濾波器。IIR濾波器具有無限持續時間沖激響應,一般需要用遞歸模型來實現。FIR濾波器的沖激響應只能延續一定時間,在工程實際中可以采用遞歸的方式來實現,也可以采用非遞歸的方式來實現。數字濾波器的設計方法有多種,如雙線性變換法、窗函數設計法、插值逼近法等。

數字濾波器的實現分為軟件實現和硬件實現2種方式,硬件主要利用通用數字濾波器集成電路、DSP處理器和FPGA來實現。由于現代實時性信號處理系統,特別是圖像、視頻系統,對處理速度的要求非常高,因此FPGA以其運算速度高的特點成為首選。傳統方法實現FPGA有一定難度。然而在用FPGA進行DSP系統開發應用的已有全新的設計工具和設計流程,給開發人員提供了很大的便利。

二、MATLAB-FDATool下的FIR濾波器設計及實現

基于FDATool的濾波器設計方法真正實現了從參數設計到硬件FPGA實現的完全自動化,這也是真正意義上的EDA。

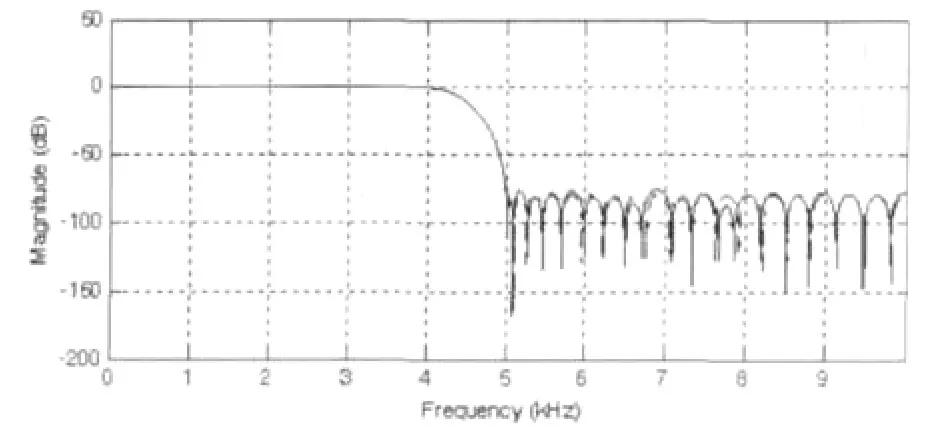

下面以Equiripple法設計FIR低通濾波器為例說明,該濾波器參數為:采樣頻率20KHz,通帶截止頻率4KHz,阻帶截止頻率5KHz,通帶最大衰減0.1dB,阻帶最小衰減80dB。

在MATLAB命令窗鍵入fdatool命令啟動設計向導界面,對其各項參數進行設置。完成設計后可在特性區查看各項性能指標。見圖1。

圖1 濾波器幅頻性能

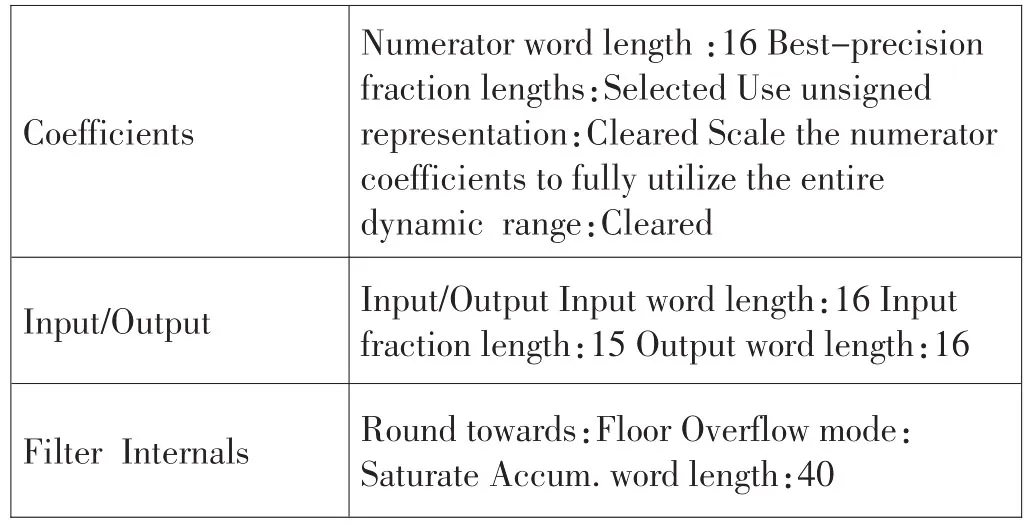

然后進行量化設置,點擊界面左側的量化參數設置按鈕,進入量化參數設置界面。設置Filterarithmetic為Fixed-point,Filterprecision設置為Specifyall,量化參數設置見表1。

表1 量化參數設置

在FDATool界面菜單下點擊Targets>GenerateHDL進入HDL代碼生成界面,選擇相應參數,在work目錄下生成濾波器及其測試向量的VHDL代碼。其定義主要端口為:數據輸入—data_in,數據輸出—data_out,時鐘—clk,使能輸入—clk_enable,復位輸入—reset。

三、MODELSIM下的結果驗證

這里我們選擇利用Modelsim軟件進行驗證,當然也可以選擇QuartusⅡ等軟件。ModelSim是優秀的HDL語言仿真器,它提供最友好的調試環境,是唯一的單內核支持VHDL和Verilog混合仿真的仿真器,是作FPGA/ASIC設計RTL級和門級電路仿真的首選。

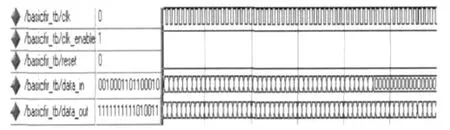

選擇前面濾波器代碼的生成路徑,進行編譯仿真,圖2為wave窗口下仿真波形的部分解圖,使端clk_enable為1時濾波器工作,data_in和data_out為16位并行數據。可以進行下載實現,并可進行硬件調試。

圖2 Modelsim下的仿真波形

四、結束語

本文以FIR數字濾波器為例,進行了基于FDATool的濾波器設計及其FPGA自動實現。在后續驗證滿足性能指標的前提下,該設計流程實現了整個設計的自動化,大大縮短了開發周期,提高了開發效率。隨著現代基于FPGA的DSP開發工具如DSP Builder、SOPCBuilder、SystemGenerator等的出現,設計者可以按照流程化軟件設計的開發方法進行FPGA的設計。