等精度頻率計的實現

夏振華

(長江大學 電信學院,湖北 荊州 434023)

頻率測量在電子設計和測量領域中經常用到,因此對頻率測量方法的研究在實際工程應用中具有重要意義。常用的頻率測量方法有兩種:頻率測量法和周期測量法。頻率測量法是在時間t內對被測信號的脈沖數N進行計數,然后求出單位時間內的脈沖數,即為被測信號的頻率。周期測量法是先測量出被測信號的周期T,然后根據頻率f=1/T求出被測信號的頻率。但是上述兩種方法都會產生±1個被測脈沖的誤差,在實際應用中有一定的局限性。根據測量原理,很容易發現頻率測量法適合于高頻信號測量,周期測量法適合于低頻信號測量,但二者都不能兼顧高低頻率同樣精度的測量要求[1]。

1 等精度測量原理

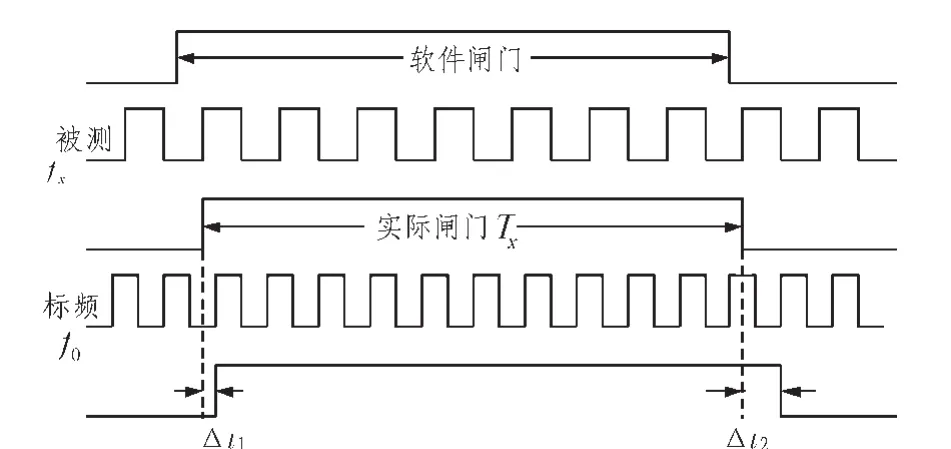

等精度測量的一個最大特點是測量的實際門控時間不是一個固定值,而是一個與被測信號有關的值,剛好是被測信號的整數倍。在計數允許時間內,同時對標準信號和被測信號進行計數,再通過數學公式推導得到被測信號的頻率。由于門控信號是被測信號的整數倍,就消除了對被測信號產生的±1周期誤差,但是會產生對標準信號±1周期的誤差[2]。等精度測量原理如圖1所示。

圖1 等精度測量原理

從以上敘述的等精度的測量原理可以很容易得出如下結論:首先,被測信號頻率fx的相對誤差與被測信號的頻率無關;其次,增大測量時間段“軟件閘門”或提高“標頻”f0,可以減小相對誤差,提高測量精度;最后,由于一般提供標準頻率f0的石英晶振穩定性很高,所以標準信號的相對誤差很小,可忽略。假設標準信號的頻率為100 MHz,只要實際閘門時間大于或等于1 s,就可使測量的最大相對誤差小于或等于10-8,即精度達到1/100 MHz。

2 等精度測頻的實現

等精度測量的核心思想在于如何保證在實際測量門閘內被測信號為整數個周期,這就需要在設計中讓實際測量門閘信號與被測信號建立一定的關系[4]。基于這種思想,設計中以被測信號的上升沿作為開啟門閘和關閉門閘的驅動信號,只有在被測信號的上升沿才將圖1中預置的“軟件閘門”的狀態鎖存,因此在“實際閘門”Tx內被測信號的個數就能保證整數個周期,這樣就避免普通測量方法中被測信號的±1的誤差,但會產生高頻的標準頻率信號的±1周期誤差,由于標準頻率f0的頻率遠高于被測信號,因此它產生的±1周期誤差對測量精度的影響十分有限,特別是在中低頻測量的時候,相較于傳統的頻率測量和周期測量方法,可以大大提高測量精度[5]。

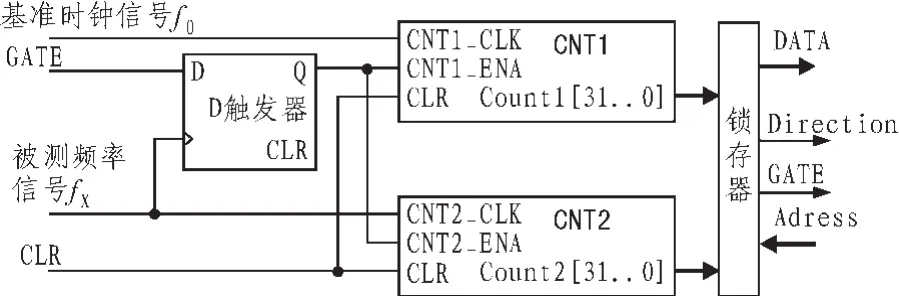

等精度測頻的原理圖如圖2所示。圖中,預置軟件閘門信號GATE是由FPGA的定時模塊產生,GATE的時間寬度對測頻精度的影響較少,故可以在較大的范圍內選擇。這里選擇預置閘門信號的長度為1 s[3]。圖中的CNT1和CNT2是2個可控的32位高速計數器,CNT1_ENA和CNT2_ENA分別是其計數使能端,基準頻率信號f0從CNT1_CLK輸入,待測信號fx從CNT2的時鐘輸入端CONT2_CLK輸入,并將fx接到D觸發器的clk端。測量時,由FPGA的定時模塊產生預置的GATE信號,在GATE為高電平,并且fx的上升沿時,啟動2個計數器,分別對被測信號和基準信號計數,關閉計數閘門必須滿足,GATE為低電平,且在fx的上升沿。若在一次實際閘門時間Tx中,計數器對被測信號的計數值為Nx,對標準信號的計數值為N0,而標準信號的頻率為f0,則被測信號的頻率為fx,則fx=(N0/Ns)f0[6]。 圖2中的所有功能都在FPGA端實現。

圖2 FPGA實現的功能的原理圖

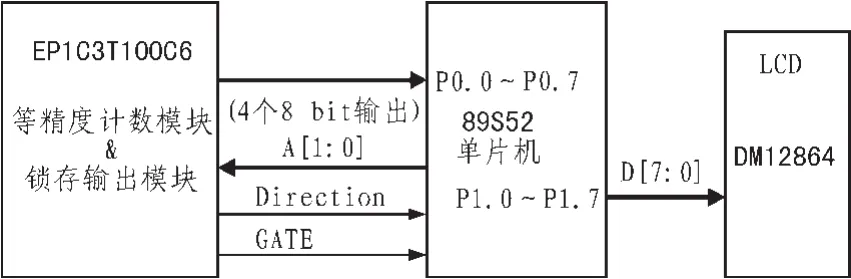

圖2所示的單元完成了等精度測頻的核心部分,在實際應用中多數時候需要將測量的結果通過顯示設備進行顯示。從圖2可以看出本設計由于設計了鎖存單元,將計數結果和一些控制信號進行了鎖存處理,便于與單片機或者其他的單片機(MCU)相連,因此在該FPGA實現的核心單元基礎上連接MCU,容易實現計數值到實際頻率值以及相應的周期值之間的轉換,并通過MCU控制顯示設備將最終需要顯示的結果信息進行顯示。FPGA器件與單片機硬件接口電路框圖如圖3所示。圖3中的等精度頻率測量模塊和鎖存模塊都由Altera公司的FPGA器件EP1C3T100C6實現,等精度計數模塊的輸出結果為2個32 bit的數據,為了方便與單片機連接,該2個32 bit數據由在FPGA器件內部的鎖存器分8次鎖存輸出,單片機每次讀取8 bit,連續讀取8次即可,讀取的Nx和N0的計數值經過單片機按照等精度頻率計算公式換算成實際頻率值,最后通過DM12864進行顯示。

圖3 硬件接口框圖

3 測量結果的誤差分析

采用高精度信號源輸出不同頻率的正弦波信號,經過信號調理電路,整形得到的方波信號提供給FPGA進行計數測量,將測量結果與高精度信號源輸出的頻率相比較,計算其誤差,如表1所示。

表1 頻率和周期測試數據

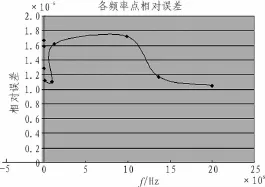

表1給出了各種頻率的測量結果和誤差。結果顯示,本設計在1 Hz~20 MHz全范圍內的測量誤差小于2×10-6。 從圖4可以看出測量結果的誤差分布在同一個數量級附近,達到了等精度測量的目的。在實際測試中發現,如果提高系統晶振的頻率或者提高晶振的精度級別,頻率測量的誤差還會進一步降低。

圖4 各個頻率點的測量誤差分布圖

4 結束語

詳細介紹了等精度測量的原理,并給出等精度測量的思想在FPGA上實現的方法。測試結果表明該等精度測量方案誤差非常小,在測量范圍內誤差恒定。該設計方案對測量頻率實現設計具有一定的借鑒。

[1]莫琳.基于FPGA的等精度頻率計的設計與實現[J].現代電子技術,2004,10(10):81-82.

[2]李紅剛.基于FPGA的高速等精度頻率測量系統設計[J].微計算機信息,2008,24(11):218-220.

[3]毛智德.基于FPGA的等精度頻率計設計[J].電子測量技術,2007,29(4):85-86.

[4]陳明杰.利用CPLD設計高速等精度頻率測量儀[J].重慶工商大學學報,2004,21(4):32-34.

[5]李麗娟,張壽明.基于CPLD/FPGA的等精度頻率計設計[J].工業控制計算機,2008,21(8):73-74.

[6]楊瀟,翟玉文,艾學忠.基于CPLD和VHDL的等精度頻率裝置[J].吉林化工學院學報,2004,21(3):49-51.