基于千兆以太網的圖像采集系統設計

馬騰飛 ,高世杰 ,吳志勇

(1.中國科學院長春光學精密機械與物理研究所,吉林 長春 130033;2.中國科學院研究生院,北京 100039)

隨著光學測量技術的提高,測控設備不僅要獲得目標的飛行軌跡等參數,同時還要獲得飛行姿態參數、瞬時速度等目標特性參數。這些參數的測量必須依賴于高幀頻、高分辨率成像器件,因此對圖像采集系統的硬件和軟件結構設計、特別是在數據傳輸和提高圖像處理速度方面都提出了較高的要求[1]。

傳統的光電經緯儀圖像采集系統分立的圖像和測量信息采集模塊使得同步采集不易實現,而且受到圖像傳輸線距離的限制,使得數據采集前端與存儲計算機必須處在同一地點,限制了系統的靈活性。因此需要一種集成的、可遠程傳輸的采集系統。本文針對Camera Link數字圖像接口的紅外相機設計了圖像采集及傳輸系統,同步采集圖像及測量信息通過千兆網實時傳輸至存儲計算機,并通過軟件對圖像進行恢復及判讀。

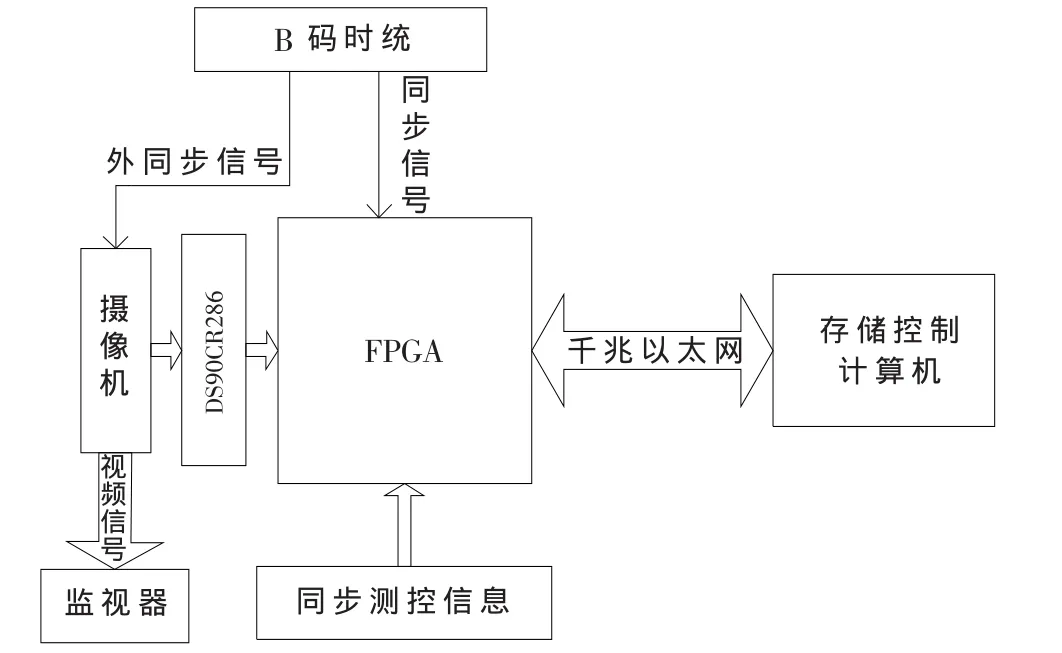

1 采集系統組成

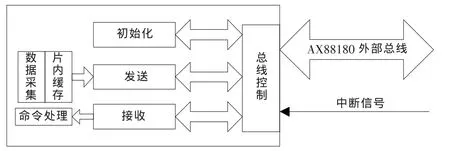

圖像采集系統由基于FPGA的采集前端、存儲控制計算機、攝像機、B碼時統等組成。計算機通過千兆以太網對采集前端發送控制命令,FPGA采集數字圖像并進行適當的組合,通過千兆網發送至存儲控制計算機,B碼時統輸出各類同步信號完成整個系統的高精度同步。系統組成由圖1所示。

圖1 圖像采集系統組成框圖

2 采集系統設計

2.1 圖像采集

Camera Link 接口是現階段高速相機普遍采用的圖像輸出接口,它是由美國國家半導體實驗室提出的一種channel link技術標準發展而來的,在傳統低壓差分信號(LVDS)傳輸數據的基礎上又增加了并轉串發送器和串轉并接收器[2]。DS90CR286的主要作用是把相機按照Camera Link標準輸出的LVDS信號轉換成TTL電平信號。轉換后的TTL信號包含像素時鐘及28位的并行數據(包括像素數據、幀同步信號、行同步信號和其他的控制信號)。

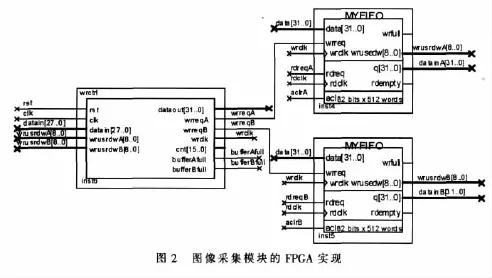

實驗采用分辨率為 320(H)×256(V)、14位像素、50 Hz或100 Hz拍攝的紅外相機,而千兆以太網接口芯片AX88180的數據總線為32位。為了提高總線利用率,在行同步信號及幀同步信號的控制下,將兩個相鄰的14位像素組合成32位數據后緩存入FPGA片內FIFO。采用片內FIFO可以減少緩存帶來的延時并節省系統成本。

出于網絡效率的考慮應采用較大的數據包,緩存圖像以兩行為單位,這樣每個FIFO中緩存的數據量為1 280字節。由于片內FIFO信號的延時導致滿空狀態并不準確,并且持續對已滿FIFO寫請求以及已空FIFO讀請求很容易導致片內FIFO崩潰[3],所以采用容量為2 048字節的 FIFO,根據 FIFO的 wrusedw[8:0]標志產生 bufferfull信號,并且在每次讀操作完成后異步清空FIFO,使得前一次操作后的狀態不會影響到下一次操作,較好地解決了狀態不準確的問題。

乒乓操作是數據采集和數據處理應用中最常采用的技巧之一,通過輸入數據選擇單元和輸出數據選擇單元按節拍相互配合切換,將過緩沖的數據流及時送到處理單元,實現了采集模塊與發送模塊的異步操作。采用FPGA內部存儲資源建立兩塊FIFO對乒乓的圖像緩存,由FPGA控制更新FIFO標記。乒乓FIFO的FPGA實現如圖2所示。

2.2 測控信息的同步采集

圖像采集系統要求所有設備高精度同步工作,這樣才能保證圖像和對應的角度信息、時間信息的一致性,從而保證數據處理的精度。系統采用的B碼終端同步精度可以達到100 ns,可產生各種頻率的同步信號,并以此作為系統的同步源完全可以滿足高精度采集系統之間以及系統內部信號的同步精度要求。

測控信息采集主要是測量角度信息和時間信息的采集以及采樣時刻的控制。本系統采用RS-422接口通信,將測控信息的采集與圖像采集在單塊電路板上完成,可以保證信息的嚴格同步。為了保證測量精度,高速測量設備都應與控制信號實現同步工作,測控信息采集時刻應與攝像機曝光時間中心對齊。采集到的測控信息緩存至專用FIFO中,幀同步信號無效時,在FPGA的控制下,加上測量信息標記后通過千兆以太網發送。

3 千兆以太網傳輸系統設計

3.1 千兆以太網結構

千兆以太網是開放系統互連(OSI)參考模型中數據鏈路層和物理層的技術,物理層負責用戶設備和網絡端設備之間物理與電氣的接口,為鏈路層提供在兩個通信系統之間發送序列位流的途徑。數據鏈路層的主要組成部分是媒體無關子層(MAC)和網絡驅動程序,負責在兩個相鄰終端間的線路上無差錯地傳輸以幀為單位的數據,每一幀由控制信息和數據組成[4]。

在千兆以太網標準集中,1000BASE-T標準在桌面領域占據主流地位。1000BASE-T采用復雜的、效率很高的4D-PAM5編碼方式,在每對5類非屏蔽雙絞線(UTP-5)上以125 MHz的線路頻率實現250 Mb/s的傳輸速度。考慮到實際應用環境,本系統設計符合1000BASE-T標準的千兆以太網傳輸系統。

3.2 硬件設計

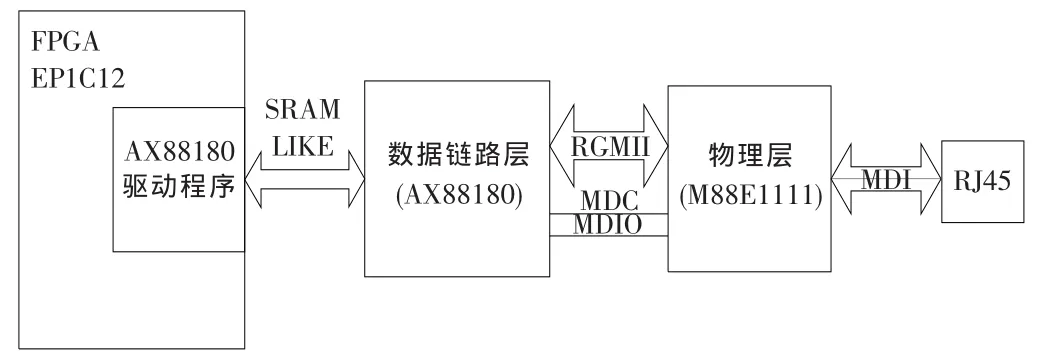

AX88180是臺灣ASIX公司針對嵌入式應用推出的千兆以太網數據鏈路層(MAC)芯片,提供16/32位類SRAM主機接口,內置40 KB的SRAM數據緩存,可用于多種需要高速接入網絡的嵌入式系統,在串流媒體、多媒體網絡、高頻寬帶傳輸等領域有廣泛的應用前景。Marvell公司的m88e1111是一款應用廣泛的千兆以太物理層(PHY)芯片,其在內部實現4D-PAM5編解碼及一系列的硬件信號處理技術、在實際應用中具有優秀的表現。

圖3所示為千兆以太網硬件組成圖,采用Cyclone EP1C12系列FPGA作為主控制器。FPGA與AX88180之間采用SRAM LIKE接口連接,通過編程實現對其控制寄存器及內部緩存的訪問。物理層芯片M88E1111與AX88180之間通過簡化千兆媒體無關接口(RGMII)互連。

圖3 千兆以太網硬件設計

3.3 千兆以太網控制驅動程序

數據采集前端要通過千兆以太網與計算機交換數據,必須實現針對AX88180的控制驅動程序。本文設計的采集系統具有圖像傳輸及命令接收功能,所以驅動程序需要實現千兆以太網雙向通信。設計中采用模塊化設計思想,驅動程序被分為4個模塊,分別是初始化模塊、發送模塊、總線控制模塊和接收模塊。

其中初始化模塊在系統上電時運行,完成網絡初始設置、狀態判斷后阻塞。數據發送模塊主要產生數據發送所需要的時序,對AX88180發送相關寄存器進行設置,將數據寫入芯片的發送緩存,等待發送成功后返回。總線控制模塊根據程序運行狀態控制數據總線與地址總線在初始化模塊、發送模塊、接收模塊之間切換。場同步信號無效后,總線控制模塊判斷AX88180中斷狀態,如果接收中斷有效則將總線交給接收模塊,接收模塊從AX88180接收緩存中讀取數據幀并且更新接收緩存指針地址后返回,場無效時間足夠完成數據包接收及命令解析的操作。各模塊之間的關系如圖4所示:

圖4 各模塊之間的關系

4 軟件設計

4.1 網絡協議

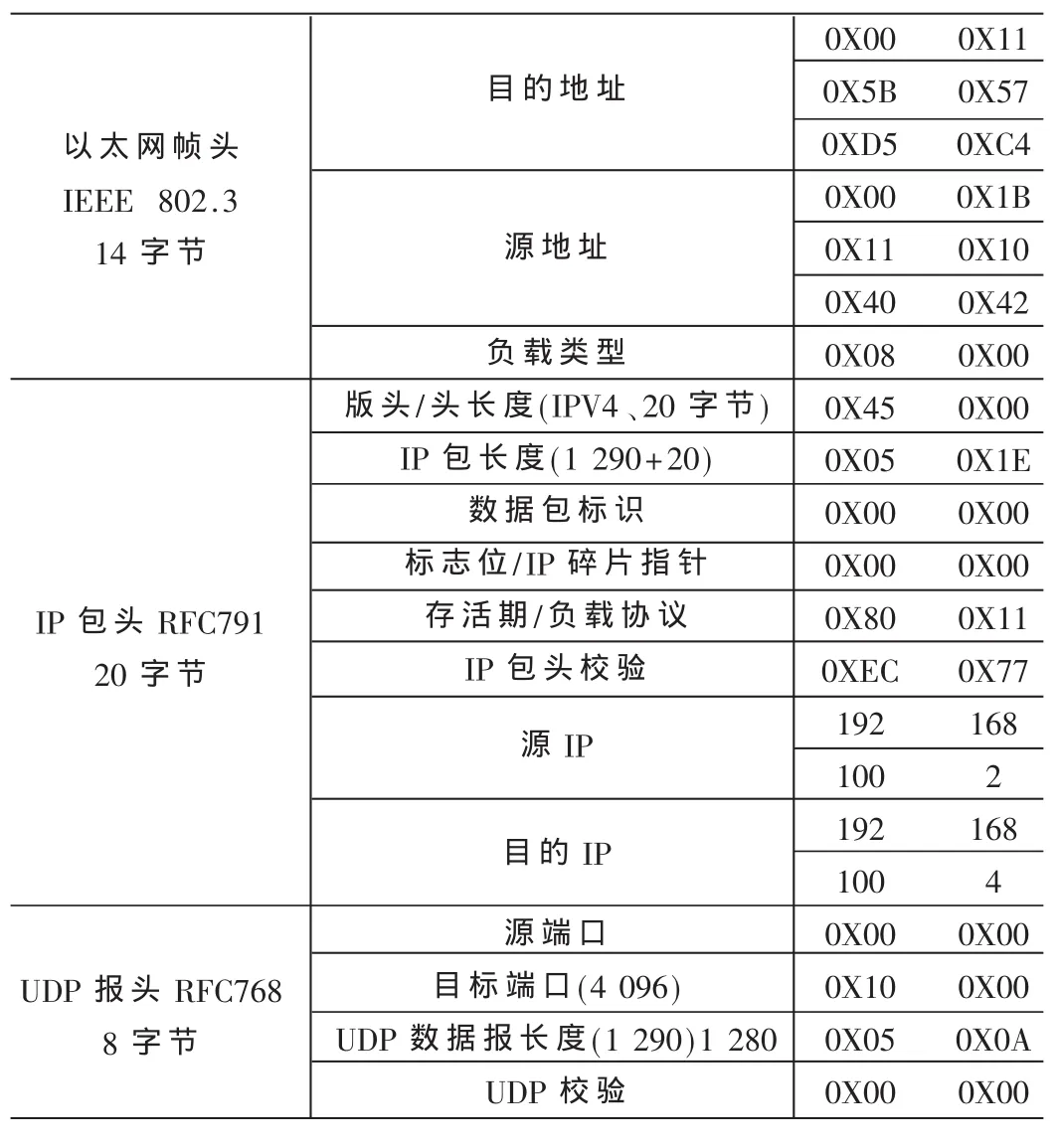

數據要經過計算機網絡傳輸,必須經過網絡協議的封裝,即在數據前面加上各層協議的信息首部。考慮到系統應用在點對點通信環境下,并且生成協議首部的所有信息(包括MAC地址、IP地址、UDP端口號、數據包長度等)都可以事先確定。所以提前將協議首部生成,附加在數據前面直接發送即可。數據幀由接收計算機端網卡及系統協議棧后去掉各層信息頭后到達應用程序。實驗采用各層協議格式如表1所示。

4.2 存儲軟件設計

由于傳輸的數據量很大,而且存盤時間除了主要依賴于存儲系統的硬件性能外還有很大的隨機性,所以必須設計良好的緩存結構,以防止因存盤導致數據丟失。本系統采用不定常隊列式緩存結構,將每個隊列單元設置為1 282×1 024字節(1 024個數據包為一個緩存單元),采用較大的數據單元可以有效減少寫磁盤請求次數。

表1 采用的協議格式

采用多線程程序設計,動態分配緩存單元。網絡接收線程將緩存接收滿后訪問隊列并且將緩存掛載至隊列尾。存儲線程在隊列不空時,從隊列中取出緩存單元后存盤。使用互斥信號量實現網絡接收線程與存盤線程之間的同步。接收數據包與存盤操作均采用異步模式,以提高程序的效率,降低系統負荷。系統可以做到只要平均寫磁盤速度大于數據采集速度,就可以保證無丟幀的存儲圖像數據。

本文設計的圖像采集系統,較好地解決了圖像與測量信息的同步采集問題。經過實際測試,系統可以穩定在600 Mb/s的傳輸速度下運行,滿足大多數紅外相機的數據傳輸需求,在實際應用中取得了良好的效果。對于其他需要遠程傳輸數據的采集系統,也有一定的參考價值。

[1]張昊.高速視頻中運動目標姿態自動判讀方法的研究[D].天津:天津大學,2005.

[2]王小艷,張會新,孫永生.Camera Link協議和FPGA的數字圖像信號源設計[J].國外電子元器件,2008(7):59-61.

[3]王智,羅新民.基于乒乓操作的異步FIFO設計及VHDL實現[J].電子工程師,2005,31(6):13-16.

[4]謝希仁.計算機網絡(第四版)[M].北京:電子工業出版社,2003.