在FPGA設(shè)計(jì)中ChipScope與MATLAB的應(yīng)用

李 輝,岳 田

(中國(guó)電子科技集團(tuán)公司第五十四研究所,河北石家莊050081)

0 引言

現(xiàn)場(chǎng)可編程門陣列(FPGA)具有規(guī)模大、邏輯復(fù)雜度高、配置靈活以及可完成復(fù)雜時(shí)序功能等特性,在當(dāng)今的數(shù)字信號(hào)處理領(lǐng)域被廣泛采用,且其速度、集成度越來(lái)越高,功耗卻越來(lái)越小。通過(guò)對(duì)FPGA加載不同的程序可以實(shí)現(xiàn)不同的功能,達(dá)到設(shè)計(jì)重用的目的,從而可以大大縮短開(kāi)發(fā)時(shí)間。在進(jìn)行FPGA內(nèi)部設(shè)計(jì)時(shí),如果要觀察FPGA內(nèi)部節(jié)點(diǎn)的信號(hào),傳統(tǒng)方法是通過(guò)編程,把內(nèi)部節(jié)點(diǎn)信號(hào)連接到FPGA的外部管腳上,通過(guò)示波器或邏輯分析儀觀察,但這種方法存在很大局限性。為解決這些問(wèn)題,Xilinx公司推出虛擬邏輯分析儀ChipScope Pro工具將硬件邏輯分析模塊和源設(shè)計(jì)都集成到FPGA中。不需額外的測(cè)試管腳,通過(guò)JTAG(Joint Test Action Group)口就可看到內(nèi)部節(jié)點(diǎn)信號(hào),改變了傳統(tǒng)的測(cè)試方法,縮短了開(kāi)發(fā)周期。

1 與MATLAB結(jié)合應(yīng)用

1.1 問(wèn)題提出

在ChipScope中對(duì)信號(hào)采樣的數(shù)據(jù)為邏輯值,可以將ChipScope作為邏輯分析儀來(lái)使用,用以觀測(cè)信號(hào)的邏輯變化是否滿足實(shí)際要求。或者將多個(gè)信號(hào)的采樣數(shù)據(jù)設(shè)置為總線形式觀測(cè),將ChipScope作為一個(gè)簡(jiǎn)易示波器來(lái)使用,用以觀測(cè)信號(hào)的幅度范圍、直流點(diǎn)變化等信號(hào)特性。但是這種觀測(cè)只是一種直觀的觀測(cè),數(shù)據(jù)量較小時(shí),可以對(duì)數(shù)據(jù)一一對(duì)比,確定是否正確,但若想得到觀測(cè)數(shù)據(jù)的準(zhǔn)確特性,就需要對(duì)采樣數(shù)據(jù)做進(jìn)一步分析,而這是ChipScope不能做到的。尤其當(dāng)采樣數(shù)據(jù)量非常大、需要對(duì)數(shù)據(jù)做統(tǒng)計(jì)分析時(shí),單純采用ChipScope就無(wú)能為力了。而目前在數(shù)字信號(hào)處理方面應(yīng)用最廣泛的數(shù)據(jù)分析及仿真軟件是MATLAB,于是產(chǎn)生是否可將采樣數(shù)據(jù)導(dǎo)入MATLAB進(jìn)行進(jìn)一步分析的想法。通過(guò)筆者進(jìn)行實(shí)驗(yàn),發(fā)現(xiàn)這是可行的,而且效果很好,并且還可以作為一種測(cè)試手段使用。下面以數(shù)字白噪聲產(chǎn)生模塊為例說(shuō)明如何將ChipScope與MATLAB結(jié)合應(yīng)用。

1.2 解決方法

首先白噪聲產(chǎn)生模塊采用的是Box-Muller算法與中心極限定理,具體描述如下:

式中,x1和x2為2個(gè)獨(dú)立的在(0,1)上服從均勻分布的隨機(jī)變量,利用上述公式進(jìn)行變換后產(chǎn)生的n1和n2即為服從N~(0,1)的白色高斯隨機(jī)數(shù)。上述變換即為Box-Muller變換。

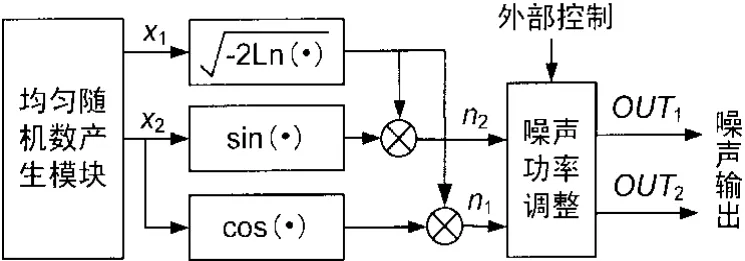

數(shù)字白噪聲算法的FPGA實(shí)現(xiàn)原理如圖1所示。

圖1 隨機(jī)噪聲產(chǎn)生示意圖

在進(jìn)行算法的FPGA設(shè)計(jì)時(shí),一般情況分為3個(gè)階段:①在MATLAB下進(jìn)行算法仿真,分析各模塊的性能,確定各模塊采用的算法及量化比特;②FPGA硬件描述實(shí)現(xiàn),功能及時(shí)序仿真;③FPGA設(shè)計(jì)程序編譯,下載程序文件產(chǎn)生,實(shí)際數(shù)據(jù)輸出測(cè)試。第1步算法仿真完成后硬件的實(shí)現(xiàn)模型也就建立完成了,剩下的任務(wù)就是在FPGA中實(shí)現(xiàn)算法,并且驗(yàn)證算法的正確性。在FPGA實(shí)現(xiàn)過(guò)程中,第2步的功能及時(shí)序仿真都可以通過(guò)仿真軟件將仿真結(jié)果存成文件交到MATLAB中進(jìn)行輸出數(shù)據(jù)的比較及分析,以驗(yàn)證仿真結(jié)果是否與MATLAB仿真吻合,不斷修正算法的FPGA設(shè)計(jì),最終完成算法的實(shí)現(xiàn)。而在最后的程序下載到FPGA階段,對(duì)最終實(shí)現(xiàn)的模塊輸出數(shù)據(jù)的驗(yàn)證只能通過(guò)ChipScope對(duì)輸出數(shù)據(jù)采樣來(lái)實(shí)現(xiàn)。在對(duì)類似于數(shù)字白噪聲產(chǎn)生模塊這種FPGA設(shè)計(jì),尤其需要對(duì)最終實(shí)現(xiàn)結(jié)果進(jìn)行大量的數(shù)據(jù)采樣、統(tǒng)計(jì)分析,驗(yàn)證結(jié)果是否正確,而不能只靠很少的采樣就認(rèn)為模塊設(shè)計(jì)符合要求。對(duì)最終模塊設(shè)計(jì)進(jìn)行數(shù)據(jù)統(tǒng)計(jì)分析操作步驟如下:

①在完成功能及時(shí)序仿真的FPGA設(shè)計(jì)中,加入ChipScope調(diào)試工具的ICON核(集中控制核)、ILA核(集成邏輯分析核)及VIO(虛擬輸入輸出核),選擇需要采樣的感興趣信號(hào),如白噪聲模塊中的n1和n2以及噪聲輸出OUT1和OUT2。其中VIO核用以模擬外部控制信號(hào),在例子中模擬的是信噪比的量化值。然后對(duì)整個(gè)工程進(jìn)行編譯產(chǎn)生比特流文件,通過(guò)JTAG口下載到FPGA中;

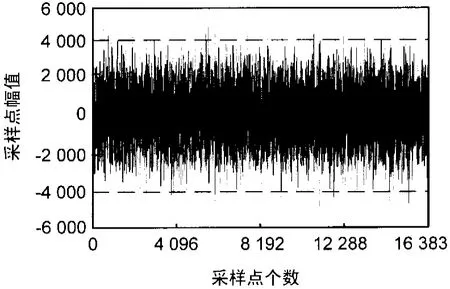

②打開(kāi)ChipScope Pro Analyzer,可自動(dòng)檢測(cè)到設(shè)計(jì)中包含的ICON核、ILA核及VIO核,選擇感興趣的信號(hào),建立總線形式,根據(jù)實(shí)際信號(hào)形式選擇有符號(hào)數(shù)還是無(wú)符號(hào)數(shù),通過(guò)VIO配置模擬的信噪比值,然后采樣,選擇Bus Plot項(xiàng),即可觀測(cè)到采樣的波形,類似于在示波器上觀測(cè)信號(hào)。例如在數(shù)字白噪聲產(chǎn)生模塊中選擇對(duì)OUT1采樣,采樣長(zhǎng)度為16 384(可設(shè)置的最大長(zhǎng)度),信噪比配置為 6 dB,在ChipScope Pro Analyzer中信號(hào)波形顯示如圖2所示。

圖2 ChipScope對(duì) OUT1采樣波形圖

MATLAB仿真的結(jié)果在信噪比為6 dB時(shí),噪聲幅度大致分布在[-1.5,1.5]區(qū)間之內(nèi)。而在數(shù)字白噪聲產(chǎn)生模塊設(shè)計(jì)時(shí),規(guī)定信號(hào)為1,設(shè)定1量化為4 096,從圖中可以看出,數(shù)據(jù)大致分布在[-6 000,6 000]區(qū)間當(dāng)中,歸一化后,噪聲輸出大致分布在[-1.5,1.5]區(qū)間當(dāng)中,與仿真結(jié)果吻合。這只是從采樣波形上的一個(gè)直觀判斷,而具體的數(shù)據(jù)特性如何,是否符合高斯白噪聲特性,在ChipScope Pro Analyzer中無(wú)法得到。

如此大量的采樣數(shù)據(jù)靠肉眼是無(wú)法判斷結(jié)果是否與MATLAB算法結(jié)果吻合。測(cè)試步驟為:首先在ChipScope Pro Analyzer中選擇File菜單中的Export…,選擇文件格式為ASCII,然后在Core欄中選擇感興趣的ILA單元,在Signals Export中選擇要導(dǎo)出的信號(hào)形式。例如筆者感興趣圖2中所示波形,因此選擇Bus Plot Buses項(xiàng),然后點(diǎn)擊Export按鈕,選擇保存的目錄及文件名,然后可得到一個(gè)擴(kuò)展名為*.prn的ASCII文件。在MATLAB中可以將此ASCII文件直接打開(kāi),可看到文件格式如表1所示。

表1 ASCII文件格式

從表中可以看出,第1行表示變量名稱,其他行為數(shù)據(jù),文件的前2列為采樣計(jì)數(shù),實(shí)際意義不大,數(shù)據(jù)處理時(shí)可不用考慮,最后一列對(duì)應(yīng)DataPort(即OUT1)的采樣值。在MATLAB中編輯此文件,將第1行刪除,只留下數(shù)據(jù),然后保存。在MATLAB里面利用[load ASCII文件名]指令即可將采樣值導(dǎo)入到MATLAB工作空間中,得到的數(shù)據(jù)為16 384行、3列的矩陣變量,變量的第3列即為采樣數(shù)據(jù)。然后可以利用MATLAB工具箱的各種數(shù)據(jù)處理及分析函數(shù)對(duì)采樣數(shù)據(jù)進(jìn)行處理和分析。

2 實(shí)例分析

本文采用此方法對(duì)所設(shè)計(jì)的高斯白噪聲產(chǎn)生模塊的輸出進(jìn)行分析,以驗(yàn)證所設(shè)計(jì)的白噪聲輸出是否正確。我們知道,高斯白噪聲的概率分布由其均值μ和標(biāo)準(zhǔn)差σ唯一確定,需要對(duì)采樣數(shù)據(jù)進(jìn)行統(tǒng)計(jì)分析,得到均值和標(biāo)準(zhǔn)差。設(shè)定信噪比為6 dB(此時(shí)高斯白噪聲標(biāo)準(zhǔn)差 σ為 0.354 4),采樣點(diǎn)為16 384,采樣波形如圖2所示。由于設(shè)定1量化為4 096,所以將得到的采樣數(shù)據(jù)除以4 096得到幅值歸一化的數(shù)據(jù),然后對(duì)幅值歸一化后的數(shù)據(jù)導(dǎo)入到MATLAB后利用統(tǒng)計(jì)函數(shù)MEAN(求均值)和STD(求標(biāo)準(zhǔn)差)對(duì)數(shù)據(jù)進(jìn)行分析得到如下結(jié)果:

mean is……-9.031296e-004

std is……3.548564e-001

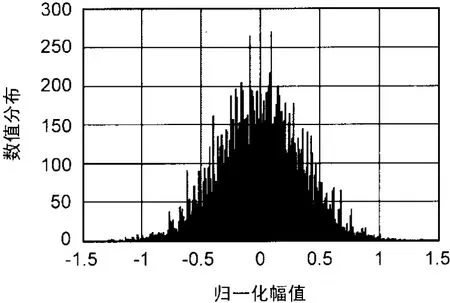

可以看出,輸出結(jié)果的均值近似為0,標(biāo)準(zhǔn)差接近設(shè)定的標(biāo)準(zhǔn)差,出現(xiàn)的小偏差是由于統(tǒng)計(jì)數(shù)據(jù)量較小的原因,設(shè)計(jì)輸出結(jié)果滿足要求。為了更直觀地觀察產(chǎn)生數(shù)據(jù)的分布,在[-1.5,1.5]歸一化幅值區(qū)間上做二維直方圖,如圖3所示。可以看到數(shù)值的分布接近正態(tài)高斯分布。對(duì)數(shù)字白噪聲產(chǎn)生模塊設(shè)置不同的信噪比值,得到不同的數(shù)據(jù)采樣,采用以上方法估計(jì)得到不同信噪比條件下的均值與標(biāo)準(zhǔn)差,均得到與MATLAB仿真吻合的結(jié)果。根據(jù)均值及標(biāo)準(zhǔn)差的統(tǒng)計(jì)結(jié)果可以得出以下結(jié)論:設(shè)置不同的信噪比值,得到符合設(shè)置條件的數(shù)字白噪聲輸出,數(shù)字白噪聲輸出模塊滿足設(shè)計(jì)要求,工作狀態(tài)可靠。

圖3 白噪聲數(shù)據(jù)的歸一化二維直方圖

3 結(jié)束語(yǔ)

隨著FPGA規(guī)模的不斷增大,通過(guò)示波器或邏輯分析儀觀察FPGA內(nèi)部節(jié)點(diǎn)信號(hào)的傳統(tǒng)方法已越來(lái)越凸現(xiàn)其局限性。ChipScop作為內(nèi)嵌的IP核,為設(shè)計(jì)者提供了一種可以觀測(cè)FPGA內(nèi)部節(jié)點(diǎn)信號(hào)的方法,而且通過(guò)與MATLAB相結(jié)合使用,極大方便了設(shè)計(jì)者對(duì)FPGA的調(diào)試、結(jié)果分析和故障判斷,大大縮短了設(shè)計(jì)開(kāi)發(fā)時(shí)間,提高了FPGA設(shè)計(jì)的可靠性,并且提供了一種對(duì)FPGA中模塊輸出數(shù)據(jù)進(jìn)行統(tǒng)計(jì)分析的有效方法。可以預(yù)見(jiàn)到,在今后的FPGA設(shè)計(jì)中,ChipScope與MATLAB結(jié)合應(yīng)用將是一個(gè)趨勢(shì)。

[1]UG029.ChipScope Pro 10.1 Software and Cores User Guide[S],2008.

[2]GHAZEL A,BOUTILLON E,DANGER J L,et al.Design and Performance Analysis of a High Speed AWGN Communication Channel Emulator[C].IEEEPACRIM Conference,Victoria,B.C.,2001:374-377.

[3]萬(wàn) 翔.ChipScope Pro在FPGA調(diào)試中的應(yīng)用[J].計(jì)算機(jī)與網(wǎng)絡(luò),2005,31(21):58-59.

[4]薛小剛,葛毅敏.Xilinx ISE 9.X FGPA/CPLD設(shè)計(jì)指南[M].北京:人民郵電出版社,2007.

[5]董長(zhǎng)虹.Matlab信號(hào)處理與應(yīng)用[M].北京:國(guó)防工業(yè)出版社,2005.