一種雙核SoC調試系統的設計與驗證

虞致國,魏敬和

(中國電子科技集團公司第58研究所,無錫 214035)

1 引言

傳統的SoC構架在提高系統整體性能上已出現了一些瓶頸,多核SoC 正成為集成電路設計的研究熱點之一[1]。多核SoC指的是一個SoC中包含2個或2個以上的處理器核,這些處理器的類型可能是異構的[2]。由于性能和功耗等方面的原因,高性能嵌入式系統多采用片上異質多處理器系統。在開發復雜SoC應用時,芯片的調試手段直接關系到開發的效率和進度,決定了應用的質量。沒有調試硬件環境支持的追蹤調試已經不能勝任復雜SoC的應用[3]。

另一方面,在SoC開發過程中,調試系統本身的驗證非常重要。對于調試系統的驗證,由于沒有相應的RTL驗證環境,一般都放在FPGA原型驗證階段進行,并借助于一些邏輯分析儀對仿真波形進行采樣分析,延長了系統驗證時間且降低了驗證效率[4-5]。

在某控制雙核SoC的硬件設計基礎上,提出了一種基于JTAG的片上調試系統設計方案;基于SystemVerilog DPI[7]和Real View調試器,提出了一種雙核SoC的片上調試系統虛擬驗證環境。在該驗證環境中,利用DPI將軟件調試器集成到驗證過程中,可完成RTL級的JTAG調試接口仿真與驗證。該方法能夠將以前FPGA原型驗證發現的調試系統錯誤提前到系統仿真驗證階段,縮短了系統周期,提高了驗證效率。

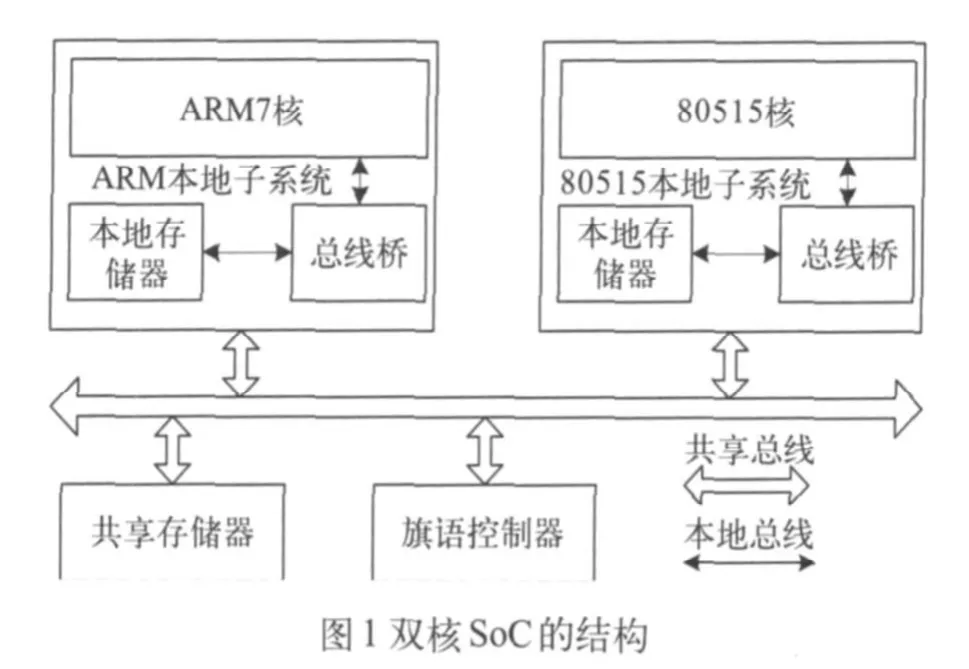

2 異構雙核SoC的結構

某異構雙核SoC面向工業控制、多媒體應用及其他消費類電子設計,其結構如圖1所示。該SoC包括一個高性能具有較強運算能力的ARM7以及一個控制能力較強但占用資源較小的80515處理器核。整個SoC有以下幾個主要部分:ARM7子系統、80515子系統、共享總線以及共享存儲器。另外,SoC還包括PLL、時鐘及復位模塊和相關的配置單元。雙核通過共享固定內存單元的機制進行通訊,來協調完成各種操作。

3 調試系統設計

3.1 調試系統軟件

ARM調試軟件采用RealView[6]調試器,該調試器在綜合性能調試環境下提供最合適的調試功效。80515調試軟件采用Keil公司開發的Keil C51。Keil uVision集成開發環境開放了調試器與目標硬件接口,即Advanced Generic Debug Interface(AGDI)。器件廠商只要為它們自己的8051產品設計專用的驅動程序(動態鏈接庫DLL),就可以使Keil IDE的調試器在不改變圖形界面的情況下支持不同的硬件鏈接方法。

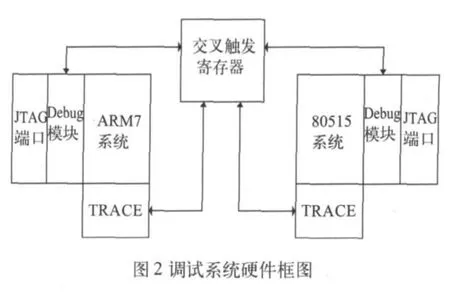

3.2 調試系統硬件

調試硬件設計如圖2所示,包括ARM和80515各自的調試系統、交叉觸發模塊。該SoC的同步調試主要分為兩類[8]:(1)單步、運行和停止(由用戶操作發出的命令);(2)交叉觸發(處理器運行過程中被觸發,需要在片內預設配置寄存器進行控制)。對寄存器和存儲空間的訪問,沒有采用同步機制,而是采用單核機制實現。

調試同步的寄存器在交叉觸發模塊(C r os s Trigger)中集中控制實現。Cross Trigger包含三個寄存器:交叉觸發命令廣播寄存器、軟件斷點同步配置寄存器、硬件斷點同步配置寄存器。交叉觸發模塊向CPU核發布命令來實現單步/運行/停止的同步執行功能、軟/硬件斷點的同步。

4 調試系統的驗證

4.1 調試驗證環境

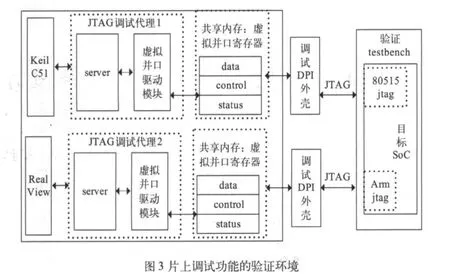

結合集成調試環境和目標芯片,可構成一個片上調試功能的驗證環境(如圖3所示)。該環境在UNIX環境中運行。集成調試環境為軟件調試器,包括RealView調試器、Keil C51調試器,JTAG調試代理、虛擬并口驅動、共享內存區。為了實現驗證Tes t b en ch和集成調試環境的連接,我們基于SystemVerilog DPI編寫了一個調試DPI外殼。通過DPI,SystemVerilog可以調用所有的C/C++/System C的功能函數,實現對共享內存區的數據訪問。

在調試驗證環境中,我們用C語言開發了一組程序,用以實現對并口內存區的訪問。在調試外殼中,使用簡單的i m p o r t聲明把C函數導入到SystemVerilog中。驗證環境中利用C語言函數調用共享內存中的數據。調試DPI外殼和驗證Testbench一起采用VCS進行編譯。

4.2 驗證Testbench的設計

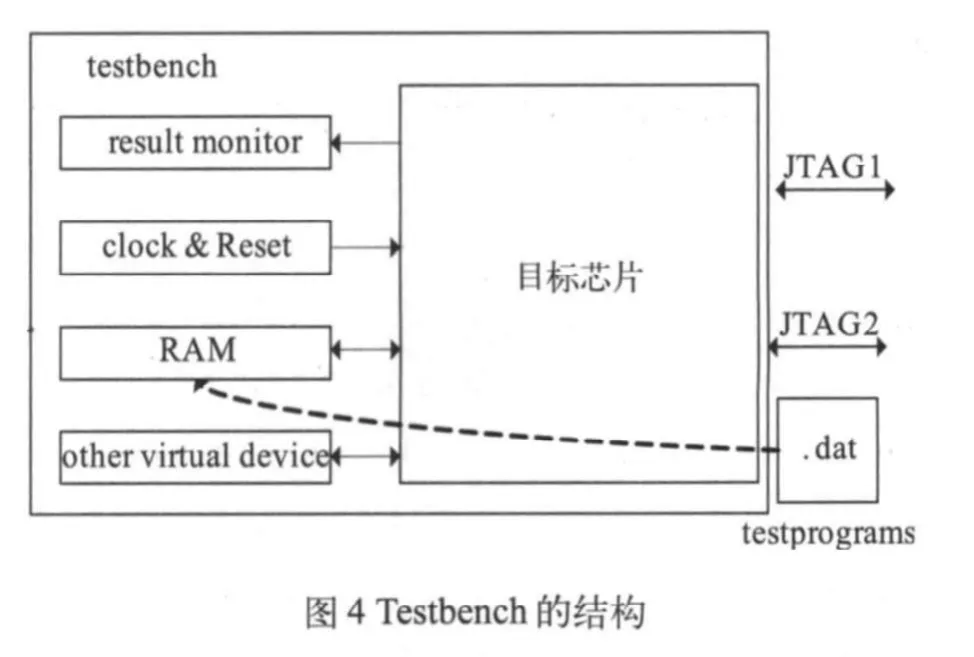

驗證Testbench采用SystemVerilog[7]實現,驗證Testbench結構如圖4所示。驗證Testbench模擬目標芯片及芯片外圍環境,包括目標SoC、外部存儲器、時鐘、復位等,采用RTL代碼及其他行為模型描述。在驗證過程中,用HDL函數$readmem讀入功能仿真程序的十六進制文件(.dat)。

4.3 驗證過程

仿真軟件采用Synopsys公司的VCS軟件。該軟件是編譯器、仿真器和其他一些工具組成的工具集。調試DPI必須編譯并鏈接到Verilog仿真器。

仿真中,RealView和Keil C51界面把數據寫到內存中的虛擬并口數據區,TAP中調用調試DPI外殼從這個數據區中交換數據,這樣就在仿真器上實現了與主機調試軟件的通信。RealView和Keil C51本身支持源碼級調試,只要調試代理正確地實現了RealView及Keil C51的遠程調試協議,本驗證系統就可實現源碼級調試。

5 結論

調試接口的設計是多核SoC設計中的重要環節,調試系統驗證對于SoC的設計非常重要。基于JTAG接口和操作系統的基礎,文中實現了某控制多核SoC片上調試功能,可實現芯片的調試控制和存儲訪問。在此基礎上,提出和設計了一種基于SystemVerilog DPI和Real View、Keil C51已有調試功能的SoC調試系統驗證環境。利用該平臺,在RTL仿真驗證時便可以通過JTAG對基于ARM核 的SoC進行調試,這使對SoC的調試從以往的FPGA驗證提前到RTL仿真驗證階段進行,可有效縮短集成SoC設計周期,并提高SoC驗證效率。

[1]成杏梅,劉鵬,鐘耿,等. 嵌入式MPSoC的調試功能實現[J]. 計算機輔助設計與圖形學學報,2008,20(4):438-445.

[2]邵利群,張文婷. 異構多處理器系統芯片的設計與研究[J].中國集成電路,2008,17(3):49-52.

[3]凱思·諾頓. 嵌入式系統的挑戰[J]. Information Quartely,2004,1:45-46.

[4]韓可,鄧中亮,施樂寧,等.針對JTAG調試的RTL驗證環境設計原理[J].電子測量技術,2008,31(1):72-76.

[5]虞致國,魏敬和. 一種基于JTAG的SoC片上調試系統的設計[J].微電子學與計算機,2009,26(5):5-8.

[6]ARM Limited.RealView Debugger Version 3.0TraceUser Guide[EB/OL].http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0322a/Babgijgj.html/ARM DUI 0322A.pdf.

[7]Standard for SystemVerilog-Unified Hardware Design[C].Specification and Verification Language.IEEE Std 1800-2005.

[8]扈嘯,李杰,陳莉麗,等. 多核處理器YHFT-QDSP的調試系統[J].計算機工程,2008,30(9):116-118.