基于FPGA嵌入式系統的研究與應用

崔 健,劉 晉

(遼寧師范大學 計算機與信息技術學院,遼寧 大連 116081)

半導體工業和嵌入式領域所面臨的主要課題之一就是設計片上系統,片上系統可以在單芯片上集成嵌入式CPU、DSP、存儲器和其他控制功能,從而可大大降低產品的開發周期,提高產品的安全性、可靠性,縮小產品的物理尺寸,降低成本[1]。片上系統:(1)可以包含:微處理器,數字信號處理器,數字、模擬及混合電路模塊,總線,時鐘,電源分布,測試結構等;(2)支持標準的工業接口和通信協議。基于現場可編程門陣列器件(FPGA)的片上系統與基于ASIC的片上系統相比,具有風險小、開發周期短、成本低、可擦寫等優點,是當今業界在快速原型技術和系統解決方案上的流行趨勢之一。目前,FPGA器件不僅是邏輯門、布線資源和I/O可編程,而且隨著半導體工藝的發展,在FPGA中還增加了許多硬件核,如存儲器、時鐘管理和算法功能,甚至增加了嵌入式處理器硬核和軟核等,即在DSP和嵌入式處理器等關鍵領域發展可編程技術,FPGA已經成為在單片器件上同時提供可編程邏輯、高性能DSP和嵌入式處理器的系統芯片[2]。在密度和性能提高的同時,極大地降低了成本和功耗,使得FPGA在更多的應用領域成為市場的主流。

1 FPGA嵌入式系統

1.1 基本原理

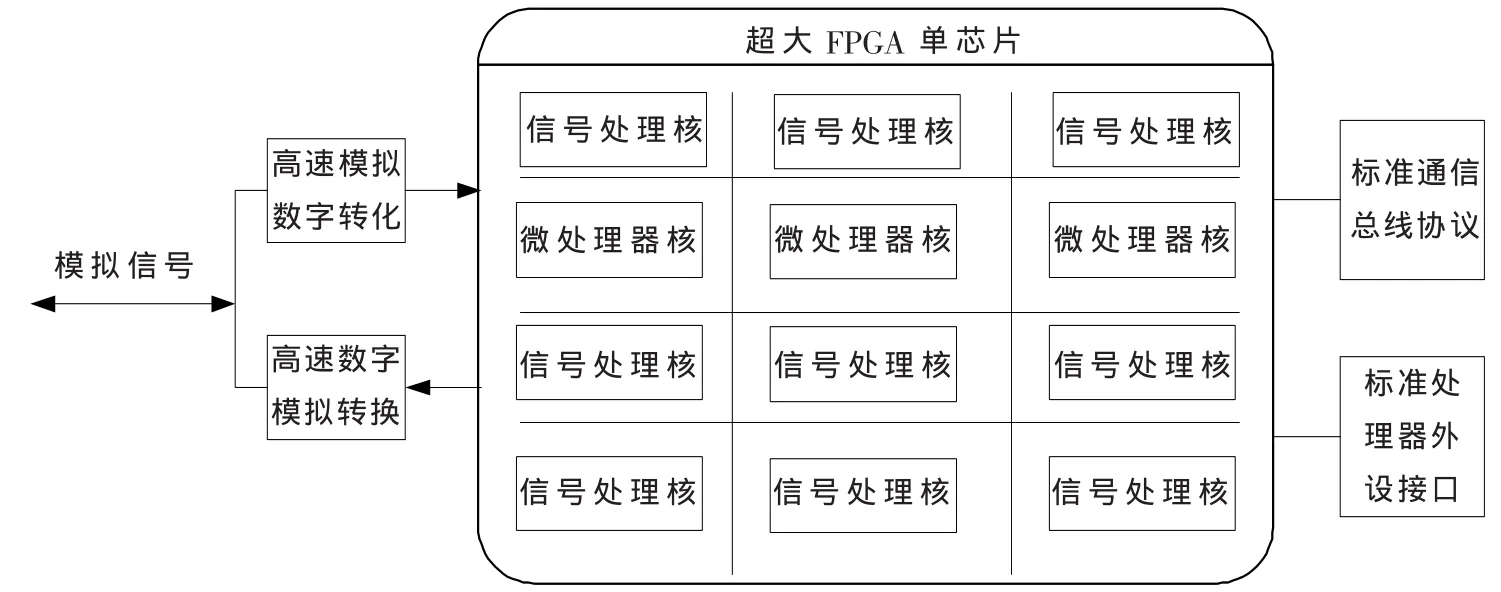

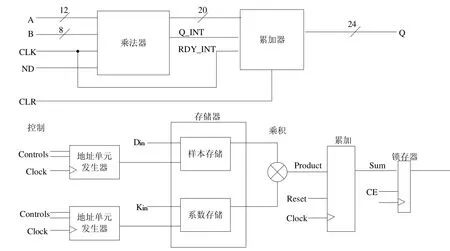

FPGA其技術的關鍵在于用戶可編程性,利用FPGA作為高度并行處理器件來設計嵌入式系統可以提供高信號處理的能力,滿足樣機開發周期短和產品上市快的要求,方便、快速地構造和仿真復雜的系統,根據用戶需要的變化或設計出現錯誤時,可以隨時升級或修改[3]。目前,圍繞嵌入式系統展開研究和開發,已經成為計算機軟、硬件技術發展最有潛力的方向之一。利用FPGA設計嵌入式系統已經成為制造業的核心技術,并廣泛地應用到醫療儀器、系統仿真、工業控制、信息家電、通信設備等領域。本文在介紹FPGA作為設計平臺實現嵌入式系統基本原理的基礎上,研究了利用FPGA實現嵌入式系統的設計方法,并利用嵌入處理器軟核,構造和裁剪嵌入式系統,在單個FPGA芯片上合理配置資源,實現多處理器的嵌入式系統。嵌入式處理器分為:嵌入式微處理器、嵌入式微控制器、嵌入式DSP處理器以及嵌入式片上系統等[4]。隨著FPGA邏輯門密度的不斷提高和設計工具軟件的不斷加強、優化,并出于對可編程的特性以及集成度等方面的考慮,以FPGA實現可配置的嵌入式系統已越來越廣泛。FPGA已經從最初的可編程邏輯器件發展到當今的可編程系統,以其豐富的可編程資源成為系統設計的平臺[5]。因此,基于FPGA的嵌入式系統設計方法實際上是一個基于可編程片上系統的設計過程。設計出來的是一種特殊的嵌入式系統:(1)它是片上系統,由單個芯片完成整個系統的主要邏輯功能;(2)它是可編程系統,具有靈活的設計方式,可裁剪、可擴充、可升級,并具備軟硬件在系統可編程的功能。這種設計一般有如下特征:至少包含1個以上的嵌入式處理器IP Core;具有小容量片內高速RAM資源;豐富的IP Core資源可以靈活地選擇;足夠的片上可編程邏輯資源;處理器調試接口和FPGA編程接口共用或并存;可能包含部分可編程模擬電路;單芯片、低功耗、微封裝。典型的基于FPGA的嵌入式系統如圖1所示。

圖1 基于FPGA的嵌入式系統結構示意圖

1.2 性能分析

要實現各種應用領域的新的復雜算法,需要有更高性能的信號處理引擎。FPGA通過并行方式可以提供極高性能的信號處理能力,可編程的靈活結構降低了設計風險。對于不斷更新和變化的標準和協議,可以通過移植設計來應對。FPGA支持DSP性能的主要機制與指令集結構的信號處理器完全不同,利用FPGA器件實現高性能的DSP功能是一種硬件實現數字信號處理的方法,因此,在處理速度上可以超過指令集結構的通用DSP。FPGA實現DSP處理時,其并行性使FPGA成為多引擎的乘法累加器,完全的并行性可以使數據的流量達到最大化。FPGA利用分布在器件內豐富的DSP資源來換取性能的提高,這些分布的DSP資源包括:查找表結構,可以實現組合邏輯、分布RAM和串行移位寄存器;嵌入式乘法器、進位鏈和乘法,專用于加速乘法運算能力;真正雙口塊RAM存儲器的多種用途,可以與嵌入乘法器配對使用;多個具有更高乘法和累加性能的DSP處理片。

1.3 FPGA實現DSP的結構變換

FPGA實現數字信號處理,一般主要通過其硬件資源、算法變換和結構變換來體現[6],而其中的難點和關鍵也在于結構變換上,而FPGA突出的優點就是能夠進行流水線和并行處理的結構變換。流水線處理是在數據通道中引入流水線寄存器來減少有效的關鍵路徑,在增加時鐘頻率的情況下也增加采樣速率;并行處理是利用重復的硬件來增加采樣速率,使得多個輸入可以并行地同時處理,多個輸出可以在同一時間產生。

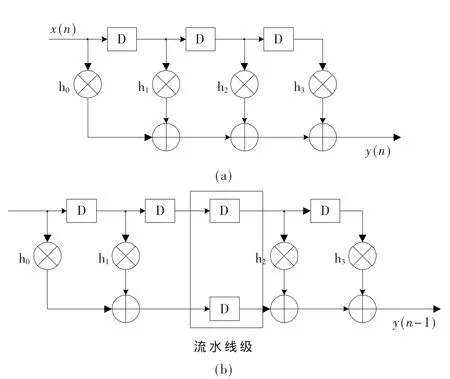

寄存器是流水線的每個功能部件所必須的[7],各流水段的時間應盡量相等,否則會引起流水線的阻塞和斷流等。DSP算法的流水線轉換時在數據通道中添加寄存器,這樣使得算法可以進行流水線處理。例如在2個乘法運算單元之間放置1個寄存器,其關鍵路徑可縮短一半,關鍵路徑上的分布電容也可減少一半,從而使得電源電壓可以降低,可相應地減少功耗。圖2為2種形式的FIR濾波器,圖 2(a)為直接形式的、N=4階的 FIR濾波器,其輸入數據的速率受限于關鍵路徑的處理速度。關鍵路徑包含3個加法和1個乘法,故其處理時間的遲滯為:Tcritical=Tmultiply+(N-1)Tadd。 其中,Tcritical為臨界處理時間,Tmultiply為累加器處理時間,Tadd則為加法器處理時間。而圖2(b)則是利用割集重新定義定時,在前饋割集邊上添加寄存器,在輸入輸出的任何路徑上延時元件的數目比原始的時序電路增加了數倍,從而實現流水線處理和運行。

圖2 2種形式的濾波器

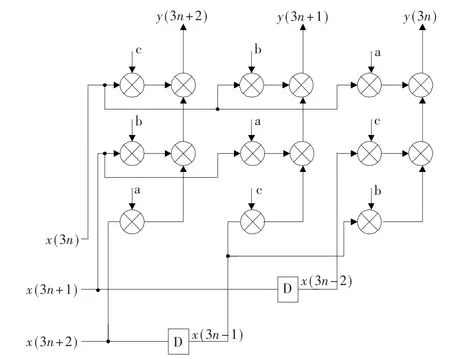

并行處理在結構上采用復制硬件的方法,幾個輸入并行地進行處理,在1個時鐘周期內同時進行計算,并同時產生幾個輸出,因此采樣率增加數倍,如二級并行處理結構則增加2倍的采樣率[8]。在并行處理系統中,關鍵路徑保持不變,如圖3所示。時鐘周期必須滿足:Tclk≥Tmultiply+2Tadd,Tclk為符合要求的時鐘周期。然而因為3個采樣是在1個時鐘周期內處理的,所以其迭代周期為:Titeration=Tsample=Tclk/L=(Tmultiply+2Tadd)/L。其中,Titeration為迭代周期,Tsample為采樣周期,Tclk為在任意1路使用寄存器產生有效延時為L個采樣率的時間。

圖3 三階并行處理結構

2 具體應用

圖4 乘法累加驅動模式

如圖4所示的乘法累加驅動的濾波器,實際上是一個簡化的DSP處理器,其N個抽頭的計算必須在采樣周期T內執行,乘法累加的速率最小應是N倍的采樣率,時鐘速率必須比采樣率更高。RAM需要與抽頭一樣多的字,其位寬由采樣尺寸設定,而ROM則要滿足系數要求。另外,采樣和系數數據是每個周期都改變的,所以需要1個完全乘法器,其位寬是由采樣數和最大系數尺寸設定。總之,濾波器的采樣頻率完全由處理全部濾波器組合所花費的時間來設定,即性能不是由器件的計算能力來決定,而是由存儲器的帶寬來限制。保持分布的RAM用來支持具有對稱性的乘法累加驅動,帶有1個預先加法器,由分布RAM提供系數。當數據寫入時,總是向右移位,但是可以讀進任何次序。單個譯碼器可以由幾個查找表來形成,后半個或這個抽頭則按照相反的次序讀入,并輸入到加法器。該譯碼器也保證奇數抽頭濾波器的中間抽頭沒有任何數據加到它上面。存儲器要輸出2個操作數到乘法累加器,并且要順序地讀出這對數據,每2個存儲器讀出周期進行1次乘法累加操作,計算結果保持或存入存儲器,以便累加器可以被復位并開始新的計算。

FPGA具有極高并行度的信號處理引擎,能夠滿足算法復雜度不斷增加的應用要求,通過并行方式提供極高性能的信號處理能力。本文針對FPGA的特性,分析和研究了FPGA實現嵌入式系統的基本原理和實現方式,并通過應用來進一步解釋和分析其設計實現過程。

[1]KAMAI R.嵌入式系統:體系結構、編程與設計[M].陳曙暉等,譯.北京:清華大學出版社,2005.

[2]RANDALL S.Specification and design methodology for real-time embedded systems[M].Janka Kluwer Academic Publishers,2002.

[3]DESCHAMP J P, BIOULG J A, SUTTER G D.Synthesis of arithmetic circuits: FPGA, ASIC and embedded systems[M].Hoboken, John Wiley, &Sons, Inc.2006.

[4]JANTSCH A.Modeling embedded system and SoC:concurrency and time in modes of computation[M].Morgan Kaufmann Publishers,2004.

[5]劉明章.基于 FPGA的嵌入式系統設計[M].北京:國防工業出版社,2007.

[6]孟憲元,錢偉康.FPGA嵌入式系統設計[M].北京:電子工業出版社,2007.

[7]ATKINSON C.Component-based software development for embedded systems:an overview of current research trends[M].Springer Verlag New York Inc,2005.

[8]BAESE U M.數字信號處理的FPGA實現[M].劉凌,譯.北京:清華大學出版社,2006.