基于DSP Builder數(shù)字信號處理器的FPGA設計

雷能芳

(渭南師范學院 物理與電子工程系,陜西 渭南 714000)

DSP技術(shù)廣泛應用于各個領(lǐng)域,但傳統(tǒng)的數(shù)字信號處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現(xiàn)數(shù)字信號處理系統(tǒng),具有很強的實時性和靈活性,因此利用FPGA實現(xiàn)數(shù)字信號處理成為數(shù)字信號處理領(lǐng)域的一種新的趨勢。

以往基于FPGA的數(shù)字信號處理系統(tǒng)的模型及算法采用VHDL或VerilogHDL等硬件描述語言描述。 但這些硬件描述語言往往比較復雜,而采用Altera公司推出的專門針對數(shù)字信號處理器設計工具DSP Builder則可大大簡化設計過程,提高設計效率。

1 基于DSPBuilder的數(shù)字信號處理器設計流程

DSP Builder是一個系統(tǒng)級(或者說算法級)設計工具,它架構(gòu)在多個軟件工具之上,并連接系統(tǒng)級的算法仿真建模和RTL級的硬件實現(xiàn)兩個設計領(lǐng)域的設計工具,最大程度地發(fā)揮了這兩種工具的優(yōu)勢。

DSP Builder依賴于Math-Works公司的數(shù)學分析工具Matlab/Simulink,以Simulink的Blockset出現(xiàn),可在Simulink中進行圖形化設計和仿真,同時又通過Signal Compiler把Maltlab/Simulink/DSPBuilder的設計文件轉(zhuǎn)成相應的VHDL設計文件,以及用控制綜合與編譯的tcl腳本。而對后者的處理可以由FPGA/CPLD開發(fā)工具QuartusⅡ完成[1]。其設計流程[2]如下:

Step1:在Simulink環(huán)境中調(diào)用Altera DSP庫 (非MA TLAB自帶的DSP庫)中的塊,進行數(shù)學模型設計。

Step2:在MATLAB中進行純數(shù)學上的仿真、驗證及修改。

Step3:當仿真符合設計要求后,再加入并運行Signal Compiler模塊,將.mdl文件自動轉(zhuǎn)成.vhd文件,進行RTL級的功能仿真和邏輯綜合。

Step4:在QuartusⅡ中進行編譯設計并進行時序仿真。

Step5:下載到一個硬件開發(fā)板上并測試。

2 設計實例

FIR和IIR濾波器是當前數(shù)字信號處理中最常用的2種濾波器,其中FIR因其具有精確的線性相位特性而得到廣泛應用。下面以截止頻率為5 kHz,采樣頻率為32 kHz,輸入序列位寬為9位(最高位為符號位)的12階FIR低通數(shù)字濾波器為例,闡述基于DSP Builder的數(shù)字信號處理器設計方案。

2.1 FIR數(shù)字濾波器結(jié)構(gòu)模型

對于N階FIR數(shù)字濾波系統(tǒng),其沖擊響應總是有限長的,系統(tǒng)函數(shù)為:

濾波器的差分方程為:

式中,x(n)是輸入采樣序列,h(n)是濾波器系數(shù),N 是濾波器的階數(shù),y(n)表示濾波器的輸出序列。

設計濾波器的任務就是尋找一個因果、物理上可實現(xiàn)的系統(tǒng)函數(shù) H(z),使其頻率響應 H(eiω)滿足所希望的頻域指標。圖1為階FIR數(shù)字濾波器的結(jié)構(gòu)圖[3]。可見,F(xiàn)IR的數(shù)字濾波過程就是一個信號逐級延遲的過程,將各級的延遲輸出加權(quán)累計,即得到FIR的輸出。

圖1 N階FIR濾波器的結(jié)構(gòu)圖Fig.1 Structure block diagrom of N-tap FIR filter

2.2 濾波器系數(shù)的確定

濾波器系數(shù)使用 Matlab的 FDATool設計工具獲得[4]。FDATool即為Filter Design&Analysys Tool,可以完成多種濾波器的設計、分析和性能評估。

啟動FDATool后就是濾波器的設計界面,設置相應參數(shù),便可生成所需的系數(shù)。由于得到的系數(shù)均為介于[-1,1]區(qū)間的浮點數(shù),而在DSP Builder下建立的FIR濾波器模型需要一個整數(shù)(有符號整數(shù)類型)作為濾波器系數(shù),故需將其量化為整數(shù)。量化后濾波器系數(shù)為:

h(0)=h(11)=-22; h(1)=h(10)=-33; h(2)=h(9)=-13;

h(3)=h(8)=41; h(4)=h(7)=108; h(5)=h(6)=-154.

2.3 濾波器模型的建立

在DSP Builder平臺上設計FIR濾波器,首先在Matlab的Simulink中建立一個.MDL模型文件,即根據(jù)所要設計FIR濾波器的結(jié)構(gòu)調(diào)用Altera DSP Builder和其他Simulink庫中的圖形模塊,構(gòu)成設計框圖文件。

如果把所有的模塊放在一個Simulink圖中,設計圖會顯得非常復雜、龐大,不利于閱讀或排錯,這時可以利用層次設計方法設計。對于12階FIR數(shù)字濾波器,可以先設計一個3階FIR濾波器子模塊fir3(圖2),然后調(diào)用3個fir3子模塊構(gòu)造成12階FIR數(shù)字濾波器。使用DSP Builder工具箱建立的12階FIR數(shù)字濾波器模型,如圖3所示。

圖2 fir3子模塊模型圖Fig.2 fir3 sub-module

圖3 12階FIR濾波器模型圖Fig.3 12-tap FIR filter module

2.4 基于Simulink的系統(tǒng)VHDL代碼生成

完成模型設計后,先在Simulink中對模型進行系統(tǒng)仿真,即通過Simulink中的2通道示波器Scope模塊查看仿真結(jié)果。DSP Builder可提供QuartusⅡ 軟件和MATLAB/Simulink工具之間的接口,即Signal Compiler模塊。

若通過系統(tǒng)仿真,該系統(tǒng)已達到設計要求,雙擊Signal Compiler模塊,設置好相關(guān)參數(shù)后,即可將模型文件.mdl轉(zhuǎn)化為硬件描述語言文件.vhd,并可對其進行綜合。之后在QuartusⅡ環(huán)境中,打開DSP Builder.建立的QuartusⅡ工程文件,就可以對生成的VHDL代碼進行器件配置、引腳設定、編譯、時序仿真、硬件下載等工作。

2.5 基于QuartusⅡ 的時序仿真

在Simulink中進行的系統(tǒng)仿真是針對算法實現(xiàn)的,與目標器件和硬件系統(tǒng)沒有關(guān)系,其仿真結(jié)果并不能精確反映電路的全部硬件特性,因此,需要對設計進行時序仿真[5]。

在QuartusⅡ環(huán)境中,打開DSP Builder建立的 QuartusⅡ工程文件,對上述的VHDL代碼進行時序仿真。圖4為在QuartusⅡ7.0環(huán)境下FIR數(shù)字濾波器時序仿真圖。圖4中clock為系統(tǒng)時鐘,sclrp為清零信號,xin為輸入數(shù)據(jù),yout為濾波器的輸出結(jié)果。

由式(2)知:若 xin{1,-5}, h(n)={-22,-33,-13,41,108,154,154,108,41,-13,-33,-22},則濾波器的輸出 yout的理論結(jié)果為:yout=xinh(n)={-14,-56,-14,53,128,180,178,124,42,-31,-64,-56,-14,28}。 可見, 所設計的 FIR 數(shù)字濾波器在QuartusII 7.0中進行時序仿真得到的輸出結(jié)果和理論上計算得到的結(jié)果是完全一致的。

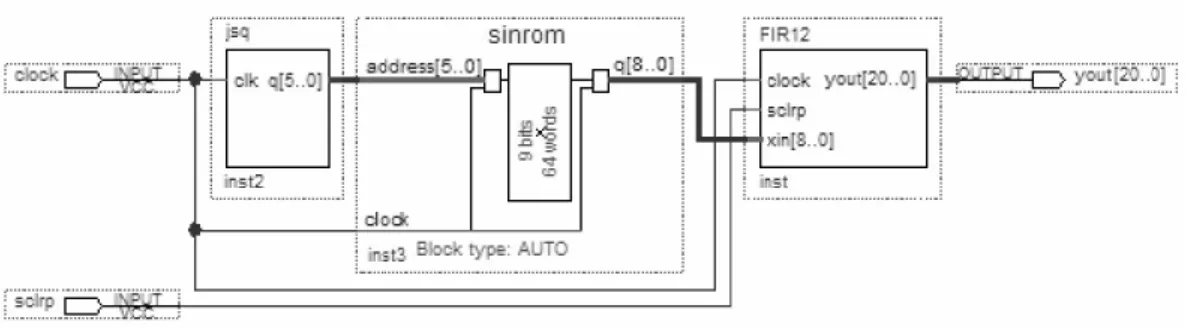

3 實際硬件測試

只進行工程軟件仿真遠遠不夠,還必須進行硬件實時測試。在硬件實際運行時,可以從外部信號源接入器件內(nèi)部或者在其內(nèi)部存儲正弦波數(shù)據(jù)。這里采用后者,即在頂層文件中引入LPM_ROM宏模塊,在其中存入頻率分別為0.5和8 kHz 2個正弦波迭加信號數(shù)據(jù)的.hex文件,F(xiàn)IR濾波器模塊直接從ROM中讀取數(shù)據(jù)[6],測試電路如圖5所示。

圖4 FIR濾波器時序仿真波形Fig.4 Timing simulation waveform of fir filter

圖5 測試電路Fig.5 Test circuit

在QuartusⅡ環(huán)境中,對測試電路進行編譯,下載到cyclone系列EP1C12Q240C8器件后,就可以對硬件進行測試。采用Altera公司的SignalTapⅡ嵌入式邏輯分析儀進行芯片測試,用戶無需外接專用儀器,就可以通過FPGA器件內(nèi)部所有信號和節(jié)點的捕獲對系統(tǒng)故障進行分析和判斷,而又不影響原硬件系統(tǒng)的正常工作[7]。

經(jīng)嵌入式邏輯分析儀得到的實時波形如圖6所示。實際測試發(fā)現(xiàn),經(jīng)過設計的低通濾波器后,高頻信號被濾除,只有低頻信號輸出,濾波效果滿足系統(tǒng)要求。需要注意的是,SignalTapⅡ嵌入式邏輯分析需工作在JTAG方式,在調(diào)試完成后,需將SignalTapⅡ移除設計,以免浪費資源。

圖6 實時波形Fig.6 Real-time waveform

4 結(jié)束語

由以上設計過程可知,基于Matlab/Simulink/DSP Builder/QuartusⅡ的設計流程,可以幫助設計者完成基于FPGA的數(shù)字信號處理系統(tǒng)設計。使用相對獨立功能的電路模塊和子系統(tǒng)進行模塊化的設計,避免了繁瑣的VHDL語言編程;設計者只要對DSP Builder模塊庫中相應模塊的基本參數(shù)進行簡單設置,而不需要對各模塊具體的實現(xiàn)過程進行詳細了解,甚至不需要了解FPGA本身和硬件描述語言,極大縮短了開發(fā)周期。而且隨著技術(shù)的發(fā)展,F(xiàn)PGA的性能越來越高,價格則逐步降低,芯片的處理速度更快,片內(nèi)資源更大,這將給FPGA在信號處理領(lǐng)域的應用提供更為廣闊的空間。

[1] 陳虹,崔葛瑾.基于FPGA的系數(shù)可調(diào)FIR濾波器設計[J].實驗室研究與探索,2008,27(6):47-50.CHEN Hong,CUI Ge-jin.Design of FIR filter with adjustable coefficients based on FPGA[J].Research and Exploration in Laboratory,2008,27(6):47-50.

[2] 楊麗杰,崔葛瑾.基于FPGA的FIR濾波器設計方法的研究[J].東華大學學報,2006,32(6):93-96.YANG Li-jie,CUI Ge-jin.The research of FIR filter design methods implemented on FPGA [J].Journal of Donghua University,2006,32(6):93-96.

[3] 程佩青.數(shù)字信號處理教程[M].3版.北京:清華大學出版社,2003:203-204.

[4] 張志恒,王衛(wèi)芳.基于Matlab信號處理工具箱的數(shù)字濾波器設計與仿真[J].電力學報,2007,22(1):54-56.ZHANG Zhi-heng,WANG Wei-fang.Digital filter design and simulation of signal processing toolbox based on MATLAB[J].Journal of Electric Power,2007,22(1):54-56.

[5] 張 淼,伏云昌.基于DSP Builder的14階FIR濾波器的設計[J].現(xiàn)代電子技術(shù),2007(21):185-186.ZHANG Miao,FU Yun-chang.Design of 14-taps FIR filter based on DSP Builder[J].Modern Electronic Technique,2007(21):185-186.

[6] 彭雪峰,汪臨偉,許建平.基于MATLAB與QUARTUSⅡ的FIR濾波器設計與驗證[J].電子設計工程,2009,17(11):118-124.PENG Xue-feng,WANG Lin-wei,XU Jian-ping.Design and verification of FIR filter based on MATLAB and QUARTUSⅡ[J].Electronic Design Engineering,2009,17(11):118-124.

[7] 潘松,黃繼業(yè).EDA技術(shù)與VHDL[M].北京:清華大學出版社,2005:178-180.