基于FPGA與DSP的雷達(dá)高速數(shù)據(jù)采集系統(tǒng)

梅坤,胡姝玲,劉宏海

(北京航空航天大學(xué)北京100191)

隨著雷達(dá)數(shù)據(jù)處理技術(shù)的快速發(fā)展,需要高速采集雷達(dá)回波信號(hào)。然而激光雷達(dá)的發(fā)射波及回波信號(hào)經(jīng)光電器件轉(zhuǎn)換后,形成的電信號(hào)脈寬窄,幅度低,而且背景噪聲大,如采用低速的數(shù)據(jù)采集系統(tǒng)進(jìn)行采集,存在數(shù)據(jù)精度不高等問題。同時(shí),為避免數(shù)據(jù)傳輸不及時(shí),發(fā)生數(shù)據(jù)丟失,影響系統(tǒng)的可靠性和實(shí)時(shí)性,需設(shè)計(jì)開發(fā)高速數(shù)據(jù)采集系統(tǒng)[1]。

設(shè)計(jì)中針對前端輸出約-25~25 mV,帶寬為20 MHz的信號(hào),采用高帶寬,低噪聲,高數(shù)據(jù)傳輸率,高分辨率數(shù)模轉(zhuǎn)換芯片AD9235;利用XC2V250內(nèi)部的大小為6 KB的異步FIFO實(shí)現(xiàn)AD9235轉(zhuǎn)換器與TMS320C6201間的高速數(shù)據(jù)傳輸。采集系統(tǒng)的采樣率為30 MHz,分辨率為12位,內(nèi)部異步緩存FIFO[2]為6 KB,滿足高速數(shù)據(jù)采集要求。

1 系統(tǒng)設(shè)計(jì)

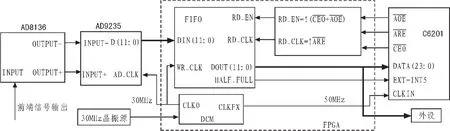

如果A/D直接與DSP的外部存儲(chǔ)接口EMIF連接,會(huì)使DSP的負(fù)荷過重,另一方面DSP還需擴(kuò)展外設(shè),與采樣輸入共用一條外部總線,進(jìn)行外部設(shè)備的讀寫,不允許數(shù)據(jù)采集始終占用外部總線。如果不能及時(shí)接收數(shù)據(jù),上次存儲(chǔ)的數(shù)據(jù)會(huì)被覆蓋,造成數(shù)據(jù)丟失。異步FIFO能實(shí)現(xiàn)不同時(shí)鐘域的數(shù)據(jù)傳輸,可將它作為A/D轉(zhuǎn)換器和EMIF之間的橋梁,每寫入一塊數(shù)據(jù),便通知EMIF從FIFO取走數(shù)據(jù)[3]。基于以上分析,圖1為高速數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)框圖。

FPGA內(nèi)部DCM為A/D轉(zhuǎn)換器和DSP提供采樣時(shí)鐘和外部振蕩源,A/D轉(zhuǎn)換器與DSP工作在不同時(shí)鐘,在FPGA內(nèi)部生成一個(gè)異步FIFO作為數(shù)據(jù)傳輸緩存。A/D轉(zhuǎn)換器把采樣值寫入FIFO,F(xiàn)IFO寫使能WR_EN一直有效,系統(tǒng)上電后,A/D轉(zhuǎn)換器一直處于工作狀態(tài),每寫入一塊數(shù)據(jù)便向DSP發(fā)出中斷信號(hào),在中斷中讀取FIFO中的數(shù)據(jù)。FIFO輸入數(shù)據(jù)寬度12位,輸出數(shù)據(jù)寬度為24位[4],F(xiàn)IFO讀時(shí)鐘高于寫時(shí)鐘,DSP讀取數(shù)據(jù)比A/D向FIFO寫數(shù)據(jù)快,而且DSP內(nèi)部數(shù)據(jù)處理時(shí)間較快,可保證系統(tǒng)高速實(shí)時(shí)采集。

圖1 高速數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)Fig.1 Structure of the high-speed data acquisition system

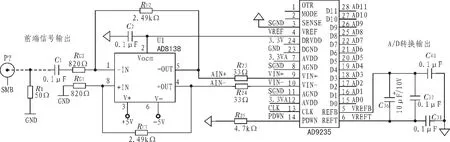

2 A/D轉(zhuǎn)換電路

A/D轉(zhuǎn)換電路是整個(gè)系統(tǒng)的重要組成部分。對前端輸出約-25~25 mV,帶寬為20 MHz的射頻信號(hào)數(shù)字化,設(shè)計(jì)采用模數(shù)轉(zhuǎn)換器芯片AD9235[5],最大采樣率40 Mb/s,12 bit數(shù)據(jù)輸出,信噪比RSN=70 dB。AD9235是差分輸入,單端信號(hào)輸入需要A/D驅(qū)動(dòng)芯片,選用低失真差分A/D驅(qū)動(dòng)芯片AD8138,圖2為A/D轉(zhuǎn)換電路,AD9235模擬輸入設(shè)置在2VPP,參考電壓VREF采用內(nèi)部1 V參考電壓,同時(shí)還作為驅(qū)動(dòng)芯片AD8138的共模電壓。利用AD8138對輸入信號(hào)進(jìn)行放大,放大倍數(shù)RF/RG=2.49 kΩ/820 Ω≈3。因此,經(jīng)過AD8138單端差分轉(zhuǎn)換及放大輸入信號(hào)范圍為25~175 mV。

圖2 A/D轉(zhuǎn)換電路Fig.2 Circuit of A/D converter

3 FPGA接口設(shè)計(jì)

3.1 時(shí)鐘設(shè)計(jì)

采用30 MHz外部晶振作為整個(gè)系統(tǒng)的時(shí)鐘源,利用XCV250內(nèi)部的時(shí)鐘管理器DCM,分別為AD9235、異步FIFO、TMS320C6201提供時(shí)鐘源。DCM輸出CLK0的30 MHz時(shí)鐘作為AD9235采樣時(shí)鐘和異步FIFO的寫周期WR_CLK。

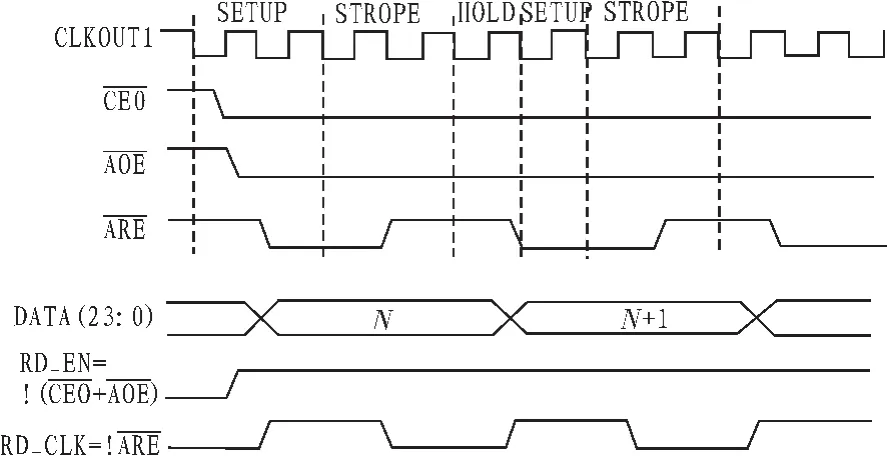

利用DCM數(shù)字頻率合成器[6]輸出CLKFX作為TMS32-0C6201的時(shí)鐘源。公式:DCM輸出CLKFX的頻率=輸入時(shí)鐘CLKIN的頻率×(M/D),取M/D=5/3。這樣DCM為TMS320C6201提供50 MHz時(shí)鐘,經(jīng)過4倍頻,DSP系統(tǒng)時(shí)鐘為200 MHz,外部存儲(chǔ)EMIF時(shí)鐘CLKOUT1為200 MHz。設(shè)置CE0空間控制寄存器的參數(shù),使FIFO讀時(shí)序SETUP、HOLD等于一個(gè)CLKOUT1周期,STROPE等于兩個(gè)CLKOUT1周期,讀時(shí)序如圖3所示,讀第一個(gè)數(shù)時(shí),EMIF會(huì)自動(dòng)維護(hù)最小2個(gè)時(shí)鐘周期的建立時(shí)間,后續(xù)數(shù)據(jù)讀取,建立時(shí)間為1個(gè)時(shí)鐘周期。FIFO讀時(shí)鐘周期約為50 MHz,比A/D向FIFO寫數(shù)據(jù)時(shí)間快,保證系統(tǒng)實(shí)時(shí)采集。

圖3 EMIF讀FIFO數(shù)據(jù)時(shí)序Fig.3 Timing diagram of reading FIFO

3.2 異步FIFO接口時(shí)序

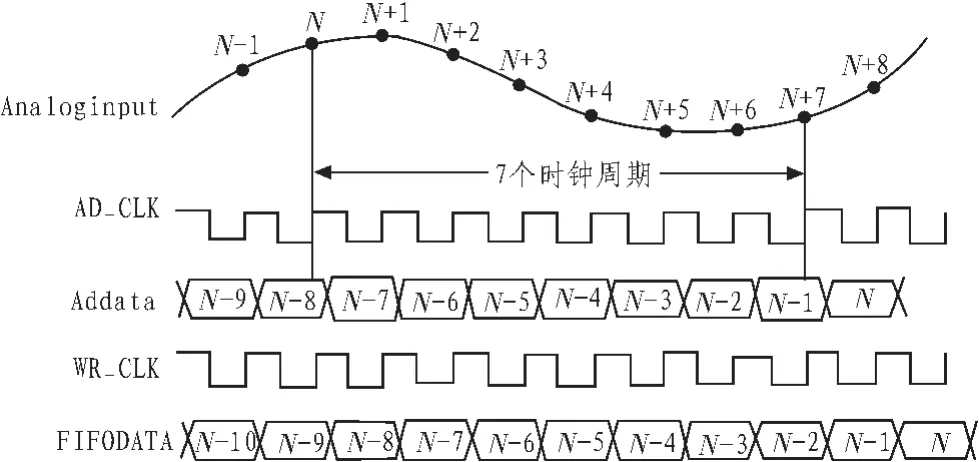

AD9235與FPGA接口設(shè)計(jì)應(yīng)仔細(xì)考慮ADC轉(zhuǎn)換時(shí)鐘、FIFO寫時(shí)鐘及所選中間邏輯器件的時(shí)序和延時(shí)特性,以保證正確地設(shè)置采樣時(shí)鐘。AD9235的采樣數(shù)據(jù)在延時(shí)7個(gè)采樣周期后出現(xiàn)在數(shù)據(jù)線上,圖4為A/D與FIFO接口時(shí)序。

圖4 AD9235與FIFO接口時(shí)序Fig.4 Timing diagram between AD9235 and FIFO

讀FIFO操作[7],利用EMIF外部存儲(chǔ)器的控制信號(hào),包含有:輸出使能位AOE和讀使能ARE以及外部空間片選信號(hào)CE0。讀寫時(shí)序如圖3,輸出使能AOE和外部空間片選信號(hào)CE0低時(shí),異步FIFO讀使能RD_EN有效,當(dāng)讀使能位ARE為低時(shí),待讀出的數(shù)據(jù)進(jìn)行初始化,隨后ARE會(huì)跳變?yōu)楦唠娖剑惒絉D_CLK端產(chǎn)生上升沿,此時(shí)異步FIFO中數(shù)據(jù)被讀出。圖1中的HALF_FULL位直接與TMS320C6201外部存儲(chǔ)區(qū)域中斷EXT-INT5觸發(fā)連接,當(dāng)FIFO緩存達(dá)到半滿時(shí),上升沿觸發(fā)DSP外部中斷,DSP啟動(dòng)DMA(直接數(shù)據(jù)存儲(chǔ))以突發(fā)方式讀取FIFO數(shù)據(jù),在時(shí)鐘CLOCKOUT1下讀取FIFO存儲(chǔ)數(shù)據(jù)。EMIF與FIFO的讀邏輯關(guān)系為RD_CLK=!ARE;RD_EN=!(CEO+AOE)。

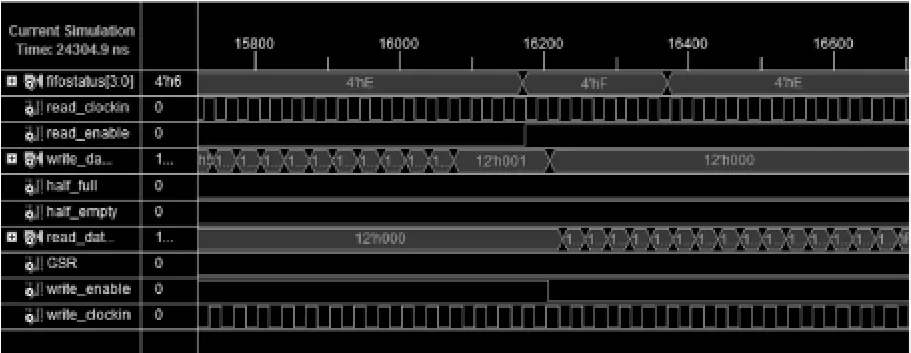

圖5為異步FIFO仿真圖,輸入數(shù)據(jù)寬度12位,輸出數(shù)據(jù)寬度為24位。讀時(shí)鐘為50置MHz,寫時(shí)鐘為30 MHz。

圖5 FIFO讀寫時(shí)序仿真Fig.5 Timing simulations of reading and writing FIFO

4 設(shè)計(jì)應(yīng)注意問題

若用異步FIFO中的FULL信號(hào)作為中斷源,滿信號(hào)位FULL有效,觸發(fā)DMA開始傳輸,在滿信號(hào)和DMA傳輸之間,A/D采集時(shí)鐘仍然驅(qū)動(dòng)A/D轉(zhuǎn)換器,會(huì)覆蓋之前存儲(chǔ)的采集數(shù)據(jù),造成數(shù)據(jù)丟失;若采用HALF-FULL信號(hào)作信號(hào)標(biāo)志位,半滿時(shí)候,開始DMA傳輸,不用中斷數(shù)據(jù)采集,由于A/D寫入速度低于EMIF讀出速度,也不會(huì)造成數(shù)據(jù)覆蓋。

FPGA內(nèi)部的異步FIFO數(shù)據(jù)總線與TMS320C6201的數(shù)據(jù)總線相連,應(yīng)注意數(shù)據(jù)采集與TMS320C6201訪問外設(shè)間的總線沖突[8-9]。應(yīng)保證沒有長時(shí)間占用數(shù)據(jù)總線的外部設(shè)備,否則造成采集數(shù)據(jù)丟失。

5 結(jié)論

針對雷達(dá)的回波信號(hào),設(shè)計(jì)基于FPGA與DSP的高速數(shù)據(jù)采集系統(tǒng),介紹了雷達(dá)前端信號(hào)A/D外圍轉(zhuǎn)換電路,利用DCM和異步FIFO實(shí)現(xiàn)ADC與高速DSP間的數(shù)據(jù)緩沖,以保證采集數(shù)據(jù)的有效傳輸。系統(tǒng)采樣率為30 MHz,采樣精度為12位,異步存儲(chǔ)緩沖FIFO大小為6 kbits,能較好地滿足高速采集要求。FIFO與DSP采用24位數(shù)據(jù)接口,讀取FIFO采用DMA數(shù)據(jù)傳輸,較充分利用DSP資源,提高了系統(tǒng)實(shí)時(shí)處理的能力。

[1]周委,陳思平,趙文龍,等.基于DSP EMIF口及FPGA設(shè)計(jì)并實(shí)現(xiàn)多DSP嵌入式系統(tǒng)[J].電子應(yīng)用技術(shù),2008,34(6):39-42.

ZHOU Wei,CHEN Si-Ping,ZHAO Wen-long,et al.Design and implementation of multi DSP embedded system based on the DSP EMIF port and FPGA[J].Application of Electronic Technique,2008,34(6):39-42.

[2]王宏臣,林詠海.基于FPGA的異步FIFO硬件實(shí)現(xiàn)[J].電子與封裝,2006,6(12):34-36.

WANG Hong-chen,LIN Yong-hai.Asynchronous FIFO hardware design based on FPGA[J].Electronics&Packaging,2006,6(12):34-36.

[3]周剛,吳杰.基于TMS320C6201的高速數(shù)據(jù)采集模塊設(shè)計(jì)[J].儀表技術(shù)與傳感器,2008(4):69-70.

ZHOU Gang,WU Jie.Design of high-speed data acquisition module based on TMS-320C6201[J].Instrument Technique and Sensor,2008(4):69-70.

[4]徐向飛.基于VHDL的FIFO存儲(chǔ)器的設(shè)計(jì)[J].南京工業(yè)職業(yè)技術(shù)學(xué)院學(xué)報(bào),2007,7(4):48-50,52.

XU Xiang-fei.The design of FIFO memory based on VHDL[J].Journal of Nanjing Institute of Industry Technology,2007,7(4):48-50,52.

[5]Analog Devices Inc.AD9235 Datasheet[EB/OL].(2004)[2010].http://www.analog.com/.

[6]宋克柱.基于FPGA的數(shù)字時(shí)鐘設(shè)計(jì)[J].核電子學(xué)與探測技術(shù),2008,28(5):982-986.

SONG Ke-zhu.FPGA-based digital clock design[J].Nuclear Electronics&Detection T-echnology,2008,28(5):982-986.

[7]王成,薛小剛,鐘信潮,等.FPGA/CPLD設(shè)計(jì)工具Xilinx ISE使用詳解[M].北京:人民郵電出版社,2005.

[8]皮代軍,張海勇,葉顯陽,等.基于FPGA的高速實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)[J].現(xiàn)代電子技術(shù),2009,32(6):12-14.

PI Dai-jun,ZHANG Hai-yong,YE Xian-yang,et al.Design of high speed real-time data acquisition system based on FPGA[J].Modern Electronics Technique,2009,32(6):12-14.

[9]劉振波,熊慶國,唐明濤.FPGA和EZUSBFX2在采集圖像數(shù)據(jù)中的應(yīng)用[J].現(xiàn)代電子技術(shù),2009,32(8):31-32.

LIU Zhen-bo,XIONG Qing-guo,TANG Ming-tao.Application of FPGA and EZUSB FX2 in image data acquisition[J].Modern Electronics Technique,2009,32(8):31-32.